# UNITED STATES PATENT AND TRADEMARK OFFICE BEFORE THE PATENT TRIAL AND APPEAL BOARD

TAIWAN SEMICONDUCTOR MANUFACTURING COMPANY, LTD., Petitioner,

v.

# ADVANCED INTEGRATED CIRCUIT PROCESS LLC Patent Owner

\_\_\_\_\_

IPR2025-00832 U.S. Patent 8,796,779

# PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT 8,796,779

Mail Stop PATENT BOARD Patent Trial and Appeal Board U.S. Patent & Trademark Office P.O. Box 1450 Alexandria, VA 22313-1450

# TABLE OF CONTENTS

| I. Ir   | ntroduction                                          | 1  |

|---------|------------------------------------------------------|----|

| II. G   | rounds for Standing                                  | 1  |

| III. Id | lentification of Challenge                           | 2  |

| A.      | Prior Art                                            | 2  |

| B.      | Grounds for Challenge                                | 3  |

| IV. T   | he '779 patent                                       | 3  |

| A.      | Technical Background                                 | 3  |

| B.      | '779 Patent's Background                             | 8  |

| C.      | '779 Patent Overview                                 | 9  |

| D.      | Prosecution History                                  | 11 |

| 1.      | '779 Patent                                          | 11 |

| 2.      | JP Application                                       | 11 |

| E.      | Claim Construction                                   | 13 |

| F.      | Level of Ordinary Skill in the Art                   | 13 |

| V. G    | ROUNDS OVERVIEW                                      | 13 |

| VI. G   | ROUND 1: Torii Anticipates Claims 1, 12-15           | 14 |

| A.      | Torii Overview                                       | 14 |

| B.      | Independent Claim 1                                  | 17 |

| 1.      | Preamble [1P]                                        | 17 |

| 2.      | Limitations [1A]-[2A]                                | 18 |

| 3.      | Limitations [1A.1]-[1A.2]/[2A.1]-[2A.2]              | 20 |

|         | a. "Active Region[s] in the Semiconductor Substrate" | 21 |

|         | b. "Gate Insulating Film"                            | 22 |

|         | c. "Gate Electrode"                                  | 25 |

| 4.      | Limitation [1B]                                      | 26 |

| 5.      | Limitation [1C]                                      |    |

| C.      |                                                      |    |

| D.      | Claim 14                                                                    | 28  |

|---------|-----------------------------------------------------------------------------|-----|

| E.      | Claim 15                                                                    | 29  |

|         | ROUND 2: Combination of Torii and Mise Renders Claims 8-11 Obviou 2         | lS. |

| A.      | Combination Overview                                                        | 33  |

| 1.      | Mise                                                                        | 33  |

| 2.      | Motivation to Combine                                                       | 34  |

|         | a. Combining Mise's teaching of a two-layer metal gate electrode with Torii |     |

|         | b. Combining Mise's teaching of a cap layer with Torii                      | 36  |

| В.      | PMIS Claims 8-9                                                             |     |

| C.      | NMIS Claims 10-11                                                           | 42  |

| VIII. C | GROUND 3: Combination of Torii and Yu Renders Claim 15 Obvious              | 43  |

| A.      | Yu Overview                                                                 | 44  |

| B.      | Claim 15                                                                    | 45  |

| IX. G   | ROUND 4: Gilmer Renders Claims 1, 12-15 Obvious                             | 54  |

| A.      | Gilmer                                                                      | 54  |

| B.      | Independent Claim 1                                                         | 55  |

| 1.      | Preamble [1P]                                                               | 55  |

| 2.      | Limitations [1A]-[2A]                                                       | 55  |

| 3.      | Limitations [1A.1]-[1A.2]/[2A.1]-[2A.2]                                     | 60  |

|         | a. "Active Region[s] in the Semiconductor Substrate"                        | 60  |

|         | b. Limitations [1A.1]-[1A.2]/[2A.1]-[2A.2]                                  | 61  |

|         | c. Limitation [1B]                                                          | 64  |

|         | d. Limitation [1C]                                                          | 65  |

| C.      | Claims 12-13                                                                | 66  |

| D.      | Claim 14                                                                    | 67  |

| E.      | Claim 15                                                                    | 68  |

|         | ROUND 5: Combination of Gilmer and Chen Renders Claims 1, 12-15             | 70  |

| A.      | Chen                                                                                                                      | 70 |

|---------|---------------------------------------------------------------------------------------------------------------------------|----|

| B.      | Combination of Chen's Core and I/O transistors of the same conductivitype with Gilmer                                     | -  |

| 1.      | Independent Claim 1                                                                                                       | 75 |

| 2.      | Claims 12-15                                                                                                              | 76 |

| C.      | Combination of Chen's gate electrode work function variation teaching with Gilmer's transistors renders claim 15 obvious. |    |

|         | ROUND 6: Combination of Gilmer, Chen, and Mise Renders Claims 8-1 bvious.                                                 |    |

| A.      | Combination of Gilmer, Chen, and Mise                                                                                     | 79 |

| B.      | PMIS Claims 8-9                                                                                                           | 82 |

| C.      | NMIS Claims 10-11                                                                                                         | 83 |

| XII. Di | iscretionary Denial In Not Appropriate                                                                                    | 84 |

| A.      | 35 U.S.C. §314(a)                                                                                                         | 84 |

| B.      | 35 U.S.C. §325(d)                                                                                                         | 85 |

| XIII. N | Mandatory Notices (37 C.F.R. §42.8(b))                                                                                    | 86 |

| A.      | Real Parties-in-Interest.                                                                                                 | 86 |

| B.      | Related Matters                                                                                                           | 86 |

| C.      | Lead and Back-Up Counsel                                                                                                  | 86 |

| XIV (   | Conclusion                                                                                                                | 88 |

# **EXHIBIT LIST**

| Exhibit | Description                                                                                                                 |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------|--|

| 1001    | U.S. Patent 8,796,779 to Ito et al. ("the '779 patent")                                                                     |  |

| 1002    | File History of U.S. Patent 8,796,779 ("'779 File History")                                                                 |  |

| 1003    | Declaration of Jakub Kedzierski                                                                                             |  |

| 1004    | CV of Jakub Kedzierski                                                                                                      |  |

| 1005    | U.S. Patent 6,881,657 to Torii, et al. ("Torii")                                                                            |  |

| 1006    | U.S. Patent Publication 2010/0258878 to Mise, et al. ("Mise")                                                               |  |

| 1007    | U.S. Patent 8,114,739 to Chowdhury, et al. ("Chowdhury")                                                                    |  |

| 1008    | U.S. Patent 6,693,333 to Yu ("Yu")                                                                                          |  |

| 1009    | U.S. Patent 6,787,421 to Gilmer, et al. ("Gilmer")                                                                          |  |

| 1010    | U.S. Patent 7,382,023 to Chen ("Chen")                                                                                      |  |

| 1011    | Van Zant, "Microchip Fabrication" (Fifth Edition, 2004) ("Van Zant")                                                        |  |

| 1012    | Weste, "CMOS VLSI Design: A Circuits and Systems Perspective" (Third Edition, 2005) ("Weste")                               |  |

| 1013    | Houssa, M., "High-k Dielectrics" to Houssa (IOP Publishing Ltd. 2004) ("Houssa")                                            |  |

| 1014    | Wolf, "Silicon Processing for the VLSI Era, Volume 4 – Deep-<br>Submicron Process Technology" (2002) ("Wolf-4")             |  |

| 1015    | Plummer, J., et al., "Silicon VLSI Technology: Fundamentals, Practice and Modeling" (Prentice Hall 2000) ("Plummer")        |  |

| 1016    | "International Technology Roadmap for Semiconductors: Process Integration, Devices, and Structures" (2007 Edition) ("ITRS") |  |

| Exhibit | Description                                                                                                                                                                                                                    |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1017    | Campbell, "The Science and Engineering of Microelectronic Fabrication" (Second Edition, 2001) ("Campbell")                                                                                                                     |  |  |

| 1018    | Chau, "Advanced Metal Gate/High-K Dielectric Stacks" ("Chau")                                                                                                                                                                  |  |  |

| 1019    | Guha, et al. "Examination of flatband and threshold voltage tuning of HfO2/TiN field effect transistors by dielectric cap layers", Applied Physics Letters (March 1, 2007) ("Guha")                                            |  |  |

| 1020    | HJ. Li and M. Gardner, "Dual high-k gate dielectric with poly gate electrode: HfSiON on nMOS and Al2O3 capping layer on pMOS," IEEE Electron Device Lett., vol. 26, no. 7, pp. 441-443, 2005. ("Li/Gardner")                   |  |  |

| 1021    | U.S. Patent 7,807,990 to Koyama ("Koyama")                                                                                                                                                                                     |  |  |

| 1022    | U.S. Publication 2006/0244035 to Bojarczuk, JR, et al. ("Bojarczuk")                                                                                                                                                           |  |  |

| 1023    | "Semiconductor Devices: Physics and Technology" by Sze (Second Edition, 2002) ("Sze")                                                                                                                                          |  |  |

| 1024    | Lee, S. J., et al. "High Quality Ultra Thin CVD HfO <sub>2</sub> Gate Stack with Poly-Si Gate Electrode," Digest of International Electron Devices Meeting, pp. 31-34, Dec. 10-13, 2000 ("Lee")                                |  |  |

| 1025    | Lee, B.H., et al., "Ultrathin Hafnium Oxide with Low Leakage and Excellent Reliability for Alternative Gate Dielectric Application," Digest of International Electron Devices Meeting, pp. 133-36, Dec. 5-8, 1999 ("Lee-1999") |  |  |

| 1026    | U.S. Patent 7,709,331 to Karve, et al. ("Karve")                                                                                                                                                                               |  |  |

| 1027    | U.S. Patent 8,017,469 to Luo, et al. ("Luo")                                                                                                                                                                                   |  |  |

| 1028    | Reserved                                                                                                                                                                                                                       |  |  |

| 1029    | Wolf, "Silicon Processing for the VLSI Era, Volume 3 – The Submicron MOSFET" (1995) ("Wolf-3")                                                                                                                                 |  |  |

| Exhibit | Description                                                                                                                                                  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1030    | Translated Excerpts from File History of JP2010-205599                                                                                                       |  |  |

| 1031    | U.S. Patent 8,384,160 to Onishi, et al. ("Onishi")                                                                                                           |  |  |

| 1032    | "An Adjustable Work Function Technology Using Mo Gate for CMOS Devices", Lin, et al., IEEE Electron Device Letters, Vol. 23, No. 1, January 2002             |  |  |

| 1033    | "Dual Work Function Metal Gate CMOS Transistors by Ni-Ti<br>Interdiffusion", Polishchuk, et al., IEEE Electron Device Letters,<br>Vol. 23, No. 4, April 2002 |  |  |

#### I. Introduction

Taiwan Semiconductor Manufacturing Company, Limited ("Petitioner") petitions for *inter partes* review of U.S. Patent 8,796,779 ("'779 patent"; TSMC-1001) claims 1 and 8-15 ("the challenged claims"). The challenged claims are directed to "a semiconductor device" comprising two MIS transistors, each having a "gate insulating film" including an "interface layer" and "high dielectric constant insulating film." (*See* TSMC-1001, claim 1.) The allegedly novel feature, that the "interface layer" of one transistor "has a thickness larger than" the "interface layer" of the other transistor, was determined by the Japanese Examiner to be known during prosecution of the Japanese counterpart application. Applicant acquiesced and narrowed the independent claim in Japan, a fact not shared with the U.S. Examiner.

Petitioner, supported by the declaration of Dr. Jakub Kedzierski, having over two decades of experience, demonstrates the challenged claims are unpatentable.

# II. Grounds for Standing

Petitioner certifies the '779 patent is available for IPR and it is not barred or estopped from requesting IPR on the grounds herein.

#### **III.** Identification of Challenge

#### A. Prior Art

The '779 patent was filed on October 31, 2012 as a continuation of PCT/JP2011/002868 ("PCT application"), filed May 24, 2011, which claims priority to JP2010-205599 ("JP application"), filed September 14, 2010. Petitioner does not acquiesce the '779 patent is entitled to priority benefit of the PCT or the JP applications. Regardless, each applied reference was filed or published before September 14, 2010.

- 1. **U.S. Patent 6,881,657 to Torii, et al.** ("Torii"; TSMC-1005), issued April 19, 2005, is prior art under 35 U.S.C. §102(b).

- 2. **U.S. Publication 2010/0258878 to Mise, et al.** ("Mise"; TSMC-1006), filed November 26, 2008, is prior art under 35 U.S.C. §102(e).

- 3. **U.S. Patent 6,693,333 to Yu** ("Yu"; TSMC-1008), issued February 17, 2004, is prior art under 35 U.S.C. §102(b).

- 4. **U.S. Patent 6,787,421 to Gilmer, et al.** ("Gilmer"; TSMC-1009), issued September 7, 2004, is prior art under 35 U.S.C. §102(b).

- 5. **U.S. Patent 7,382,023 to Chen, et al.** ("Chen"; TSMC-1010), issued June 3, 2008, is prior art under 35 U.S.C. §102(b).

## **B.** Grounds for Challenge

| Gro | und | Claims   | Prior Art            |

|-----|-----|----------|----------------------|

| 1   | 102 | 1, 12-15 | Torii                |

| 2   | 103 | 8-11     | Torii + Mise         |

| 3   | 103 | 15       | Torii + Yu           |

| 4   | 103 | 1, 12-15 | Gilmer               |

| 5   | 103 | 1, 12-15 | Gilmer + Chen        |

| 6   | 103 | 8-11     | Gilmer, Chen, + Mise |

## IV. The '779 patent.

## A. Technical Background

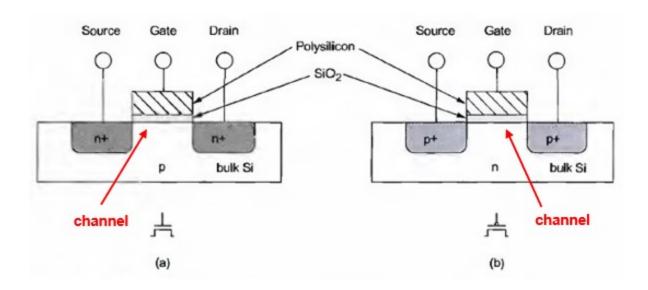

A metal-insulating-semiconductor transistor (MISFET or MOSFET) generally includes a conducting gate electrode, an insulating layer, and "the silicon wafer, also called the substrate, body or bulk." (TSMC-1012, 8.) An nMOS transistor "is built with a p-type body and has regions of n-type semiconductor adjacent to the gate called the source and drain." (TSMC-1012, 8, Figure 1.8(a)(below).) A pMOS transistor "is just the opposite, consisting of p-type source and drain regions with an n-type body." (TSMC-1012, 8, Figure 1.8(b)(below)<sup>1</sup>.)

<sup>&</sup>lt;sup>1</sup> Unless otherwise noted, all shading and annotations added.

Weste, Figure 1.8

A key device feature is the gate insulating film, commonly referred to as a "gate dielectric", which separates the gate electrode from the semiconductor channel between the source and drain. For over 40 years (1961-2007), siliconbased oxides were the primary materials used for gate dielectrics in MOSFETs due to their excellent insulating properties, thermal stability, and compatibility with silicon. However, as transistors scaled down, the silicon-based oxide layer had to become thinner, leading to increased gate leakage due to quantum tunneling. (TSMC-1013, 5-8.) High-k dielectrics, which allow for a thicker gate insulator while maintaining the same capacitance, replaced silicon-based oxides to address these challenges. (TSMC-1013, 8-9.)

Equivalent Oxide Thickness (EOT) is a key concept used in assessing high-k dielectrics. The EOT ( $t_{eq}$ ) of a material "is defined as the thickness of the SiO<sub>2</sub>

layer that would be required to achieve the same capacitance density as the high-k material in consideration." (TSMC-1013, 9.) The EOT of a gate dielectric having only a high-k layer is given by the following equation:

$$\frac{t_{\text{eq}}}{\varepsilon_{\text{r,SiO}_2}} = \frac{t_{\text{high-}\kappa}}{\varepsilon_{\text{r,high-}\kappa}}$$

(1.1.2)

"where  $t_{high-k}$  and  $\epsilon_{r,high-k}$  are the thickness and relative dielectric constant of the high-k material, respectively." (*Id.*) For example, "using ZrO<sub>2</sub> as gate dielectric ( $\epsilon_r \approx 20$ )" allows "use a 5.1 nm thick layer in order to achieve a capacitance equivalent to a 1 nm thick SiO<sub>2</sub> layer; the equivalent oxide thickness of this ZrO<sub>2</sub> layer is thus 1 nm." (*Id.*)

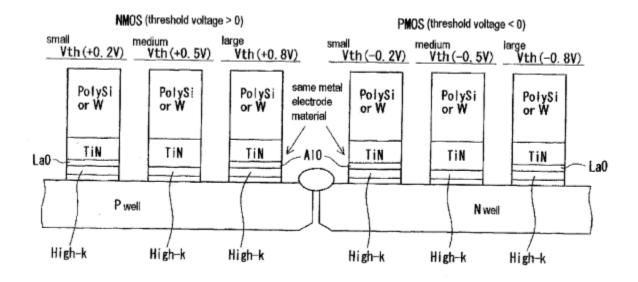

The threshold voltage is the voltage applied at the gate which brings the onset of inversion (formation of the current-carrying channel)—i.e., the transistor's "turn-on" voltage. (TSMC-1011, 526.) Because pMOS and nMOS transistors are built on different dopant type bodies and feature different types of dopants for their respective source/drain terminals, nMOS transistors, which use electrons in a p-type body to form the channel between the source and drain terminals, have a **positive** threshold voltage and pMOS transistors, which use holes in an n-type body to form the channel between the source and drain terminals, have a **negative** threshold voltage. (*See, e.g.,* TSMC-1012, 74, 293-296, 302; TSMC-1003, ¶54.)

Consumer devices often have multiple transistors of the same conductivity types but with different threshold voltages to cope with various demands on standby power and operation speed. For example, a device may include transistors for low operating power (LOP), transistors for low stand-by power (LSTP), and transistors for high performance (HP). (TSMC-1003, ¶55; TSMC-1016, 5.) HP transistors have the highest operating speed, the shortest gate length, the thinnest gate oxide, and the lowest threshold voltage among the three. (TSMC-1016, 11, 17, 21.) LSTP transistors are designed for low performance and low leakage current and therefore have thicker gate oxides and higher threshold voltage, while LOP transistors are between the HP and LSTP devices in terms of performance, leakage current, and threshold voltage. (TSMC-1016, 11, 17, 21.)

Threshold voltage has three main components: flatband voltage ( $V_{FB}$ ), voltage drop across the gate oxide ( $V_o$ ), and semiconductor potential at the semiconductor surface during strong inversion ( $\psi_s(inv)$ ). (TSMC-1023, 175, 178, 194; TSMC-1003, ¶¶57-59.) For a given semiconductor and dielectric material, the primary "knobs" that can be used to predictably tune a transistor's threshold voltage are substrate doping, oxide thickness  $t_{ox}$ , and the metal work function  $\Phi_m$ . (TSMC-1013, 535, 537; TSMC-1003, ¶59.) When the substrate doping and gate oxide thickness are carefully engineered to control channel mobility and the gate

capacitance, respectively, the gate electrode work function is the "knob" of choice to optimize (fine-tune) the threshold voltage further. (TSMC-1003, ¶59.)

A material's "work function" is "the minimum energy required to bring an electron from the Fermi level to the vacuum level." (TSMC-1029, 117; *see, e.g.,* TSMC-1003, ¶¶42-53, 60.) However, in MOS/MIS structures, the metal is in direct contact with a dielectric, not with the vacuum. Moreover, work functions of metal gates are highly dependent on material properties and interfaces. To differentiate this, an "effective work function" of **the metal gate**<sup>2</sup> is commonly used to refer to the metal work function as measured, e.g., through the threshold voltage of the device. (TSMC-1003, ¶61.)

Metal gates are commonly used in gate stacks with high-k gate dielectrics because metal gates eliminate the polysilicon depletion effect, have very low resistance, and have better compatibility with high-k dielectrics (e.g., are immune to Fermi level pinning). (TSMC-1003, ¶32.) Because the work function of a metal is an intrinsic material property that cannot be easily tuned via doping as in the case of polysilicon gates, introducing metal gates into transistors means the threshold voltage of the MOSFET becomes tied to the metal selection. (TSMC-

<sup>&</sup>lt;sup>2</sup> The '779 patent's use of the term "effective work function of **the transistor"** is discussed in §IV.B.

1016, 3; TSMC-1003, ¶64.) Many techniques existed prior to the '779 patent to tune the work function of a metal gate including, for example, adjusting the gate electrode composition and adding metal layer(s). (See TSMC-1003, ¶¶65-66.)

#### B. '779 Patent's Background

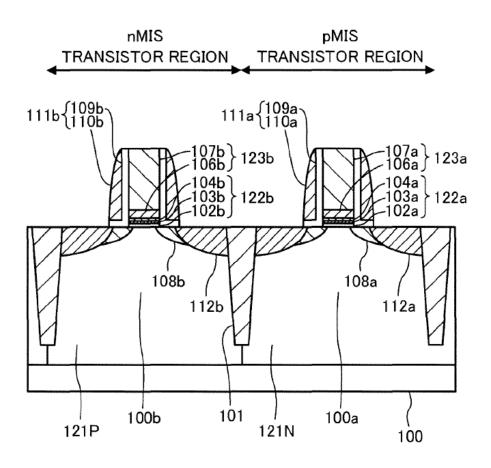

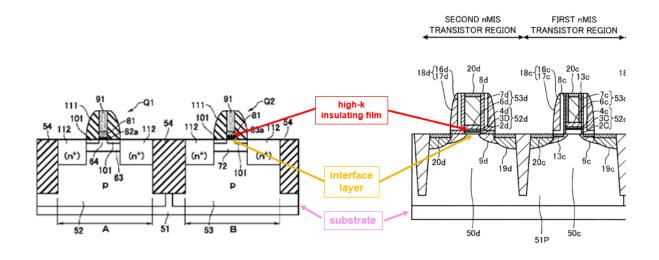

The '779 patent describes a conventional "complementary metal insulator semiconductor (CMIS) device composed of an n-type MIS transistor and a p-type MIS transistor which are provided on an identical substrate." (TSMC-1001, 1:48-51.) The pMIS/nMIS transistors in the conventional device include a gate insulating film having interface layer 102, high-k dielectric 103, and cap layer 104 and a gate electrode having a metal film and a polysilicon film. (See TSMC-1001, 1:61-2:31; Figure 13 (below).) The background section acknowledges pMIS cap film 104a and nMIS cap film 104b "enable control of a work function of each of the gate electrodes 123a and 123b." (TSMC-1001, 2:24-27.) The '779 patent also refers to an effective work function of a transistor which it describes as "a work function obtained from electrical characteristics of a MIS transistor." (TSMC-1001, 3:18-19.) The '779 patent contends the transistor's "effective work function is obtained by incorporating influence such as a level in an insulating film<sup>3</sup> into a

<sup>&</sup>lt;sup>3</sup> Unless otherwise noted, all emphasis added.

work function related to physical properties and representing a difference between a vacuum level and an energy level of a metal." (TSMC-1001, 3:20-24.)

'779 Patent, Figure 13 [Admitted Prior Art]

#### C. '779 Patent Overview

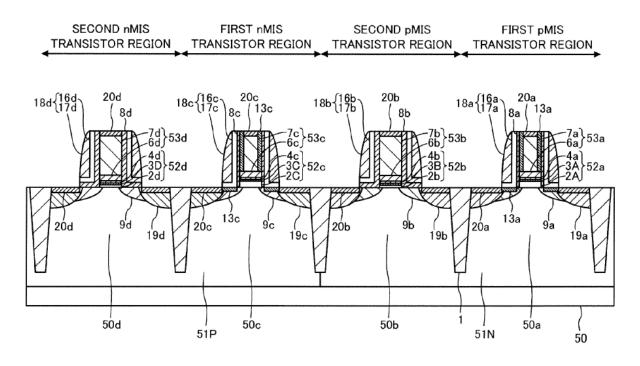

The '779 patent's purported objective is to "enable formation of a plurality of transistors of the same conductivity type having different work functions in a semiconductor device having a MIS structure in which a high-k film is used as a gate insulating film." (TSMC-1001, 3:50-54.) The '779 patent's semiconductor device includes first and second pMIS transistor regions and first and second nMIS

transistor regions. (TSMC-1001, 7:13-14, Figure 9 (below).) Each transistor includes gate electrode (53a-d) with gate insulating film (52a-52d) interposed between the gate electrode and an active region of the substrate (50a-d). (TSMC-1001, 8:47-60.) Each gate insulating film includes interface layer 2a-2d, high-k film 3a-3d, and cap film 4a-4d. (TSMC-1001, 8:61-67.) The interface layers 2A and 2C in the first nMIS and pMIS regions are thicker than the interface layers 2b and 2d in the second nMIS and pMIS regions. (*See* TSMC-1001, 9:55-10:5.)

'779 Patent, Figure 9

The '779 patent concludes the increased interface layer thickness of the first pMIS and nMIS transistors leads to an increased EOT which results in an increased "effective work function of the transistors": "Accordingly, the EOT of the gate insulating film 52a of the first pMIS transistor and that of the gate insulating film

52c of the first nMIS transistor increase, **thereby causing** the effective work functions of the first pMIS transistor and the first nMIS transistor to increase." (TSMC-1001, 13:23-27; *see also*, 12:47-54, 13:19-23.)

#### **D.** Prosecution History

#### 1. '779 Patent

The U.S. application was filed with one independent semiconductor device claim corresponding to issued claim 1. The Examiner rejected the claim as anticipated by U.S. Patent 8,492,230 to Ishikawa, et al. ("Ishikawa"). (TSMC-1002, 204-205.) In response, Applicant argued Ishikawa's gate insulating films "are formed above different base substrate[s]" and therefore Ishikawa does not anticipate claim 1. (TSMC-1002, 300-301.) Notably, Applicant did not dispute Ishikawa discloses two transistors with different interface layer thicknesses. Applicant also amended claim 1 to recite "each of the first interface layer and the second interface layer is made of a silicon dioxide film or a silicon oxynitride film." (TSMC-1002, 294.) The Examiner subsequently allowed the claims. (TSMC-1002, 312-313.)

# 2. JP Application

The JP priority application was filed with a device claim having nearly identical scope as the '779 patent's issued claim 1. (TSMC-1030, 1.) On August 20, 2013, before issuance of the '779 patent, the JP Examiner found the claims

unpatentable over three separate JP publications including JP2003-100896 to Fujiwara ("Fujiwara"). (TSMC-1030, 4-5.) Fujiwara, illustrated in Figure 11 (below left), discloses transistors of the same conductivity type formed on the same substrate with different interfacial layer thicknesses, like the '779 patent's claimed transistors.

Fujiwara's, Figure 11; '779 Patent, Figure 9-Excerpt

In response, on September 13, 2013, Applicant narrowed the independent claim to recite sidewall spacer limitations corresponding to the '779 patent's issued claim 2. (TSMC-1030, 7.) The JP Examiner allowed the claims based on this amendment.

Thus, Applicant acquiesced during JP prosecution that the scope of issued claim 1 of the '779 patent was unpatentable. Though the JP refusal and Applicant's subsequent JP amendment occurred before the '779 patent's issuance, Applicant

did not provide a translation of the JP refusal notice or its response to the U.S. Examiner.

#### E. Claim Construction

Petitioner does not believe any claims require construction to resolve the patentability disputes in this proceeding. *See Vivid Techs., Inc. v. Am. Sci. & Eng'g, Inc.*, 200 F.3d 795, 803 (Fed. Cir. 1999)

#### F. Level of Ordinary Skill in the Art

A POSITA would have had at least a Master's degree in electrical engineering, physics, chemistry, materials science, or related fields, and three years of work experience in semiconductor manufacturing, including planar transistors. (TSMC-1003, ¶89.) Additional graduate education could substitute for work experience, and additional work experience/training could substitute for formal education. (*Id.*)

#### V. GROUNDS OVERVIEW

The Petition presents Grounds 1, 4 and 5 demonstrating independent claim 1 and dependent claims 12-14 are unpatentable and Grounds 2 and 6 demonstrating dependent claims 8-11 are unpatentable. Regarding claim 15, the '779 patent describes the **effective work function of a transistor** and discloses only one technique for adjusting it—altering the thickness of the interfacial layer of the gate insulating layer and hence the EOT of the gate insulating layer. Claim 15 is

specifically directed to this concept, reciting "an effective work function of the first MIS transistor is higher than an effective work function of the second MIS transistor." Grounds 1 and 4 establish claim 15 is anticipated or obvious in the same manner as disclosed in the '779 patent.

Despite this limited disclosure, PO alleges in the co-pending district court litigation a transistor with an additional metal layer in its gate electrode would demonstrate a slightly higher effective work function than another MIS transistor missing this layer because the additional layer allegedly possesses a higher effective work function<sup>4</sup>. Regardless, adjusting the **work function of a metal gate electrode** in this and other ways was well known before the '779 patent. (TSMC-1003, ¶62-67.) Grounds 3 and 5 establish claim 15 is obvious under PO's litigation allegations.

# VI. GROUND 1: Torii Anticipates Claims 1, 12-15

#### A. Torii Overview

Torii's first embodiment device includes MISFET 110 for LOP (low operating power), MISFET 120 for LSTP (low stand-by power), and MISFET 130

<sup>&</sup>lt;sup>4</sup> PO's litigation allegations are subject to the district court's protective order. Petitioner reserves the right to seek discovery in the present proceeding should PO take an inconsistent position.

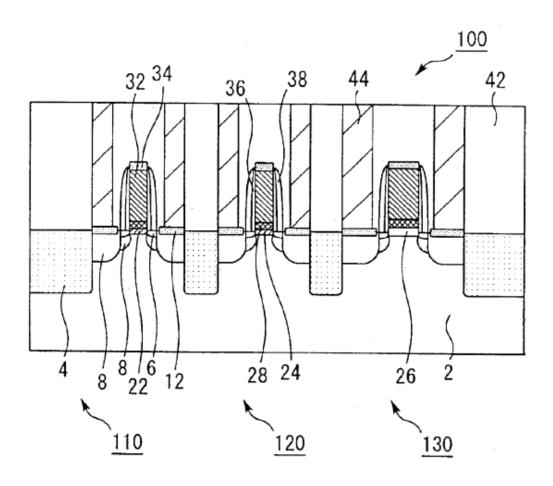

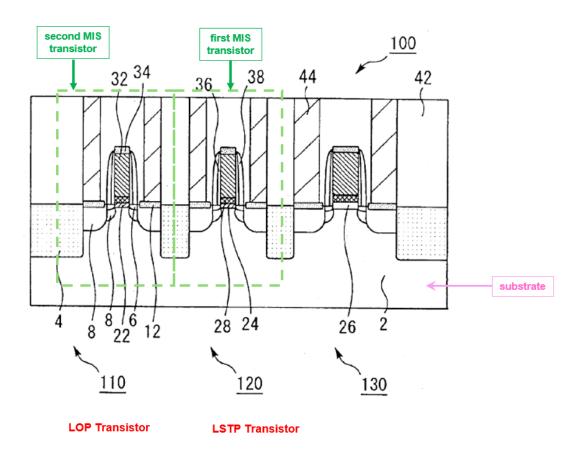

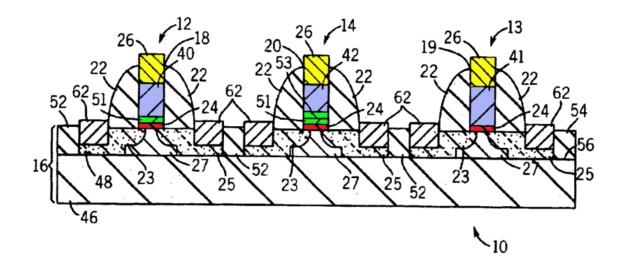

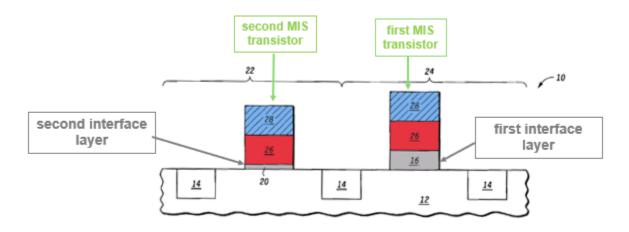

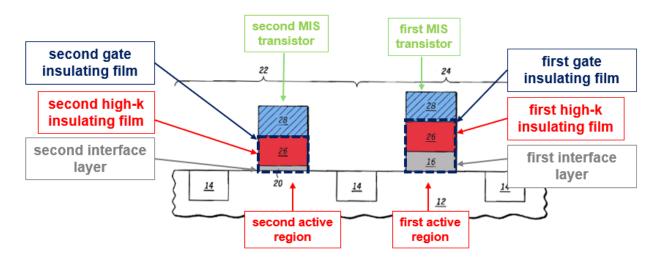

for high withstand voltage. (TSMC-1005, 4:61-5:4, Figure 1(below).) The LOP and LSTP FETs each includes a gate electrode and a "gate insulating film includ[ing] a silicon oxynitride film [22, 24] and a high-dielectric constant film [28]." (TSMC-1005, 3:65-4:4, 5:62-6:1.)

Torii, Figure 1

Torii's device has the same structure as the '779 patent's claim 1, as evidenced by the striking similarity between Torii's claim 1 and '779 patent claims 1 and 13.

| Torii – Claim 1                                                                                                                                               | '779 Patent – Claims 1 and 13                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. A semiconductor device comprising;                                                                                                                         | 1. A semiconductor device comprising:                                                                                                                                                                                    |

| a substrate,  a first field-effect transistor, including a first gate insulating film and a first gate electrode, on the                                      | a first MIS transistor and a second<br>MIS transistor of an identical<br>conductivity type provided on an<br>identical semiconductor substrate,                                                                          |

| major surface of said substrate, and                                                                                                                          | wherein the first MIS transistor includes a <b>first gate insulating film</b> formed on a first active region in the semiconductor substrate and a <b>first gate electrode</b> formed on the first gate insulating film, |

| a second field-effect transistor, including a second gate insulating film and a second gate electrode, on the major surface of said substrate, wherein        | the second MIS transistor includes a second gate insulating film formed on a second active region in the semiconductor substrate and a second gate electrode formed on the second gate insulating film,                  |

| each of said first gate insulating film<br>and said second gate insulating film<br>includes a silicon oxynitride film and a<br>high-dielectric-constant film, | the first gate insulating film includes a first interface layer being in contact with the semiconductor substrate and a first high dielectric constant insulating film formed on the first interface layer,              |

|                                                                                                                                                               | the second gate insulating film includes a second interface layer being in contact with the semiconductor substrate and a second high dielectric constant insulating film formed on the second interface layer,          |

| equivalent-oxide thickness of said first gate insulating film is thicker than                                                                                 | the first interface layer has a thickness larger than that of the second interface layer, and                                                                                                                            |

| Torii – Claim 1                                                                                                                                                       | '779 Patent – Claims 1 and 13                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| equivalent-oxide thickness of said second gate insulating film, and                                                                                                   |                                                                                                                                         |

|                                                                                                                                                                       | each of the first interface layer and the second interface layer is made of a silicon dioxide film or a silicon oxynitride film.        |

| the high-dielectric-constant film in said first gate insulating film-has the same thickness as the high-dielectric-constant film in said second gate insulating film. | 13. The semiconductor device of claim 1, wherein the first and second high dielectric constant insulating films are equal in thickness. |

# B. Independent Claim 1

# 1. Preamble [1P]

Torii discloses "a semiconductor device<sup>5</sup>" [1P]: "present invention relates to a **semiconductor device** having a plurality of transistors comprising gate insulating films of different film thickness." (TSMC-1005, 1:11-14; *see also*, TSMC-1005, 3:54-60, claim 1 (claiming a "semiconductor device"); TSMC-1003, ¶¶103-105.)

<sup>&</sup>lt;sup>5</sup> Claim language indicated by italics throughout. A challenged claim listing with labels is provided in the Appendix.

#### 2. Limitations [1A]-[2A]

Torii teaches "[1A] a first MIS transistor and [2A] a second MIS transistor of an identical conductivity type provided on an identical semiconductor substrate." (TSMC-1003, ¶¶107-110.)

Torii's device includes Si substrate 2 ("semiconductor substrate") having regions "isolated by STI (shallow trench isolation) 4." (TSMC-1005, 5:1-4; Figure 1 (below).) The "Si substrate 2 is divided into a region for forming **an MISFET** for LSTP [low operating power] 110, a region for forming **an MISFET** for LSTP [low stand-by power] 120, and a region for forming an MISFET for high withstand voltage 130." (TSMC-1005, 6:14-18; see also, 4:61-67.) The LSTP

<sup>&</sup>lt;sup>6</sup> Torii uses a "polycrystalline silicon film" for its gate electrode, which is a conductive, non-metal. (TSMC-1005, 7:6-10.) Torii's usage of "MIS" to refer to its transistors with a conductive gate electrode is consistent with the common convention in the field prior to the '779 patent. (TSMC-1003, ¶107, *citing* TSMC-1012, 8 ("Gates of early transistors were built from metal, so the stack was called metal-oxide-semiconductor, or MOS. Now the gate is typically formed from polycrystalline silicon (*polysilicon*), but the name stuck") (emphasis in original), ¶32; *see also*, TSMC-1007, 2:22-29.) Indeed, the '779 patent's gate electrode also includes "a silicon film 7." (*See, e.g.,* TSMC-1001, 9:1-2.)

transistor is "a first MIS transistor" [1A] and the LOP transistor is "a second MIS transistor" [2A]. (TSMC-1003, ¶107.) Because the LSTP and LOP transistors are formed on the same substrate, the LOP and LSTP transistors are "provided on an identical semiconductor substrate." (See TSMC-1005, 3:62-65 ("[a]ccording to one aspect of the present invention, a semiconductor device comprises a substrate, and a first field-effect transistor and a second field effect transistor formed on the substrate"); TSMC-1003, ¶108.)

Torii, Figure 1

Torii teaches the LOP transistor and LSTP transistor are "n-type transistor[s]." (TSMC-1005, 10:39-40.) However, "the present invention may be applied to the case wherein a p-type transistor is formed." (TSMC-1005, 10:40-42.) The LOP and LSTP transistors are therefore "of an identical conductivity type." (TSMC-1003, ¶109-110; see also, TSMC-1003, ¶22-24, 38-41.)

# 3. Limitations [1A.1]-[1A.2]/[2A.1]-[2A.2]

Torii's LSTP transistor ("first MIS transistor") includes "a first gate insulating film formed on a first active region in the semiconductor substrate and a first gate electrode formed on the first gate insulating film" [1A.1], "the first gate insulating film includes a first interface layer being in contact with the semiconductor substrate and a first high dielectric constant insulating film formed on the first interface layer" [1A.2]. (TSMC-1003, ¶¶112-127.)

Torii's LOP transistor ("second MIS transistor") includes "a second gate insulating film formed on a second active region in the semiconductor substrate and a second gate electrode formed on the second gate insulating film" [2A.1], "the second gate insulating film includes a second interface layer being in contact with the semiconductor substrate and a second high dielectric constant insulating film formed on the second interface layer" [2A.2]. (TSMC-1003, ¶¶112-126, 128.)

# a. "Active Region[s] in the Semiconductor Substrate"

The LSTP transistor ("first MIS transistor") and LOP transistor ("second MIS transistor") each has an "active region in the semiconductor substrate" between isolation (STI) structures. (TSMC-1003, ¶¶112-114; TSMC-1005, Figure 1 (below); TSMC-1015, 52-53 (regions between isolation structures "where transistors will be built, are called the 'active' regions of the substrate"); TSMC-1001, 1:67-2:3 (describing "a portion of the semiconductor substrate 100 surrounded by the shallow trench isolation 101 … serves as an active region 100b"); §IV.A.)

Torii, Figure 1

Torii's fabrication method confirms the presence of an "active region" in both the LSTP and LOP transistors. (TSMC-1003, ¶113.) Specifically, after dividing the substrate into regions for forming transistors (TSMC-1005, 6:14-18), "implantation of p-type ions for controlling the impurity content in the substrate, heat treatment the impurity diffusion, ion implantation for controlling the threshold voltage, and heat treatment for activation are performed." (TSMC-1005, 6:24-27.) Further, "[o]n each region of the Si substrate isolated by STI 4", source-drain extension 6, punch-through stopper 8, and source-drain region 10 are formed. (TSMC-1005, 5:5-12.)

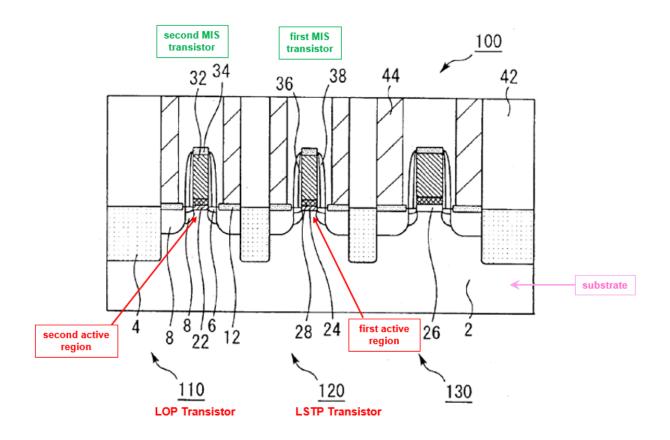

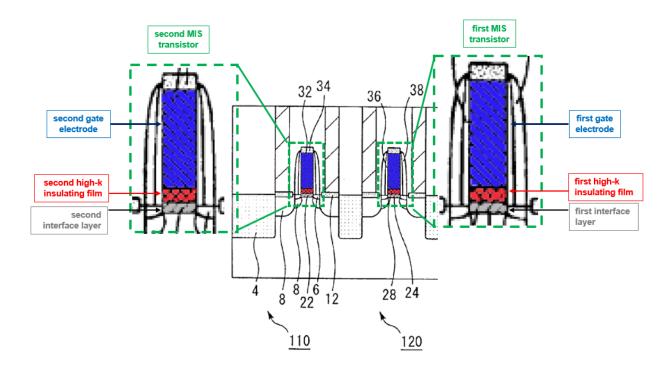

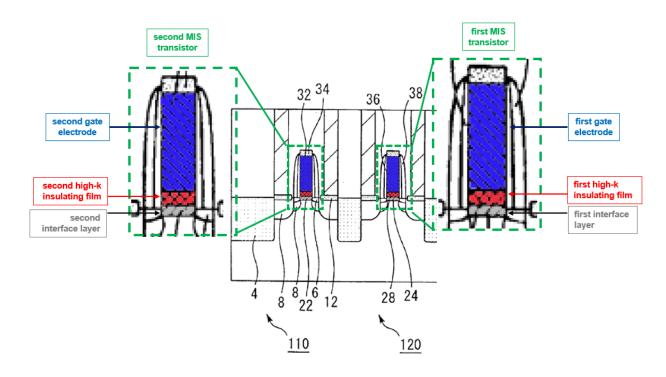

# b. "Gate Insulating Film"

As shown in the enlargements of the LSTP and LOP transistors in Figure 1 below, the gate stack of Torii's LOP transistor 110 includes silicon oxynitride film 22 (shaded grey) and high-k film 28 (shaded red); the gate stack of LSTP transistor 120 includes silicon oxynitride film 24 (shaded grey) and high-k film 28 (shaded red). (TSMC-1005, 5:14-18, 5:33-36; *see also*, TSMC-1005, 6:66-7:5, 8:14-23.) Torii refers to oxynitride film and high-k film collectively as a "gate insulating film." (See TSMC-1005, 4:1-4 ("Each of the first gate insulating film and the second gate insulating film includes a silicon oxynitride film and a high-dielectric-constant film"), 8:14-18.) Accordingly, oxynitride film 24 and high-k film 28 in the LSTP transistor are collectively "a first gate insulating film" and oxynitride

film 22 and high-k film 28 in the LOP transistor are collectively "a second gate insulating film." (TSMC-1003, ¶¶115-117.)

Torii, Excerpt from Figure 1 with enlargements

Silicon oxynitride films 22, 24 are each an "interface layer." (See TSMC-1005, 9:32-38 (referring to oxynitride films 22/24 as "interfacial gate insulating films"); TSMC-1003, ¶118.) In Torii's LOP transistor, "silicon oxynitride film 22 [shaded grey] is formed as an **interfacial** gate insulating film in the area sandwiched by source-drain extensions 6 **on the Si substrate 2**." (TSMC-1005, 5:14-17.) In the LSTP transistor, "a silicon oxynitride film 24 [shaded grey] is formed in an equivalent area." (TSMC-1005, 5:17-18, 9:32-38.) Thus, as shown in Figure 1, silicon oxynitride films 24/22 ("first/second interface layer") are each "in

contact with the semiconductor substrate" [1A.2]/[2A.2] and therefore the "gate insulating film" of both the LSTP and LOP transistors is "formed on a [first/second] active region in the semiconductor substrate" [1A.1]/[2A.1]. (TSMC-1003, ¶¶118-119.)

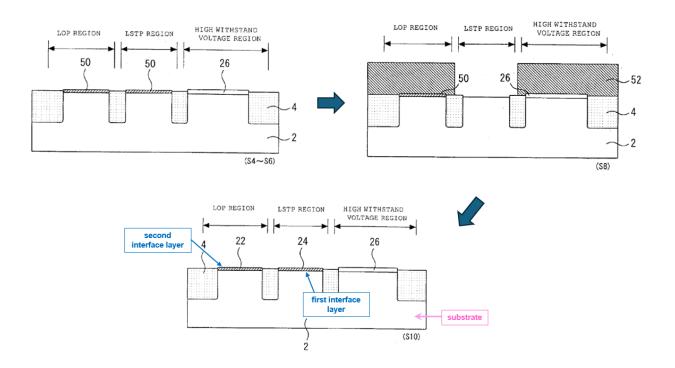

Torii's manufacturing method confirms the Figure 1 structure. During manufacture, "silicon nitride film 50 is formed in each of the regions for LOP and LSTP." (TSMC-1005, 6:36-37, Figure 4 (top-left).) After silicon nitride film 50 is removed in the LSTP region (Figure 5, top-right), "heat treatment in a nitrogen monoxide (NO) environment" is performed which forms silicon oxynitride film 24 in the LSTP region (Figure 6, bottom). (TSMC-1005, 6:46-56.) Silicon nitride film 50 in the LOP region "is oxidized to form a silicon oxynitride film 22." (TSMC-1005, 6:57-59.) For both the LOP and LSTP transistors, the silicon oxynitride film ("interface layer") of the "gate insulating film" is formed on an active region of the substrate. (TSMC-1003, ¶¶119-123.)

Torii, Figures 4 (top-left), 5 (top-right), 6 (bottom)

On each silicon oxynitride film 24/22, a "high-k film [shaded red] such as a hafnia (HfO<sub>2</sub>) film 28" is formed. (TSMC-1005, 5:33-36; see also, TSMC-1005, 6:66-7:5, 8:14-23, Figure 1.) That is, in the LSTP and LOP transistors, a "[first]/[second] high dielectric constant insulating film [high-k film 28] is formed on the [first]/[second] interface layer [oxynitride films 24/22]." (TSMC-1003, ¶¶124-125.)

#### c. "Gate Electrode"

In Torii, "[o]n each high-k film 28, a **gate electrode** 32 [shaded blue] is formed." (TSMC-1005, 5:42, Figure 1 (below); *see also*, TSMC-1005, 7:6-22.)

Accordingly, each LSTP and LOP transistor includes a "gate electrode formed on the [first/second] gate insulating film." (TSMC-1003, ¶126.)

Torii, Excerpt from Figure 1 with enlargements

# 4. Limitation [1B]

Torii teaches "the first interface layer has a thickness larger than that of the second interface layer" [1B]. (TSMC-1003, ¶¶130-132.)

Torii's "relates to a semiconductor device having a plurality of transistors comprising **gate insulating films of different film thicknesses**." (TSMC-1005, 1:11-13; *see also*, TSMC-1005, 4:4-6, claim 1.) Specifically, in the LSTP transistor (the "first MIS transistor"), the thickness of silicon oxynitride film 24 ("first interface layer") "is about 1.3 nm; and the EOT thereof is about 1.0 nm." (TSMC-1005, 5:23-25.) In the LOP transistor (the "second MIS transistor"), the thickness

of silicon oxynitride film 22 ("second interface layer") "is about 0.9 to 0.95 nm, and the EOT thereof is about 0.7 nm." (TSMC-1005, 5:20-23.) That is, silicon oxynitride film 24 in the LSTP MISFET is thicker than silicon oxynitride film 22 in the LOP MISFET. (TSMC-1003, ¶129-132.)

#### 5. Limitation [1C]

Torii teaches "each of the first interface layer and the second interface layer is made of a silicon dioxide film or a silicon oxynitride film" [1C]. (TSMC-1003, ¶133.) As discussed in §VI.B.3.b, the "first interface layer" is silicon oxynitride film 24 and the "second interface layer" is silicon oxynitride film 22. (See also, TSMC-1005, claim 1, 5:14-18.)

#### C. Claims 12-13

Torii teaches "each of the first and second high dielectric constant insulating films contains hafnium or zirconium" [12]. (TSMC-1003, ¶134.) In Torii, a "high-k film such as a hafnia (HfO<sub>2</sub>) film 28" is formed on each of silicon oxynitride films 22 and 24. (TSMC-1005, 5:33-36; see also, TSMC-1005, 6:66-7:3, 8:14-18; see also, TSMC-1005, 10:9-16 (listing alternative high-k materials including hafnia (HfO<sub>2</sub>), hafnium aluminate (Hf<sub>x</sub>Al<sub>1-x</sub>O<sub>y</sub>)).)

Torii further teaches "the first and second high dielectric constant insulating films are equal in thickness" [13]. (TSMC-1003, ¶¶135-137.) In Torii, a high-k film "of a thickness of about 3.0 nm" with an EOT "of about 0.5 nm" is formed

"[o]n each of the silicon oxynitride films 22 and 24." (TSMC-1005, 5:33-37.) That is, the physical thickness and EOT of the high-k film in both the LOP and LSTP transistors is equal. (TSMC-1003, ¶¶135-137; *see also*, TSMC-1005, 4:6-9 ("high-dielectric-constant film in the first gate insulating film has the **same thickness** as the high-dielectric-constant film in the second gate insulating film"), 6:66-7:3, claim 1.)

#### D. Claim 14

Torii teaches "the first and second gate electrodes are made of an identical material" [14]. (TSMC-1003, ¶138.)

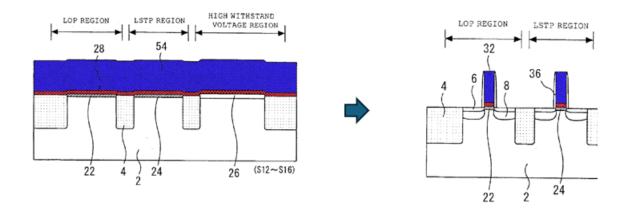

To form Torii's gate electrodes in the LSTP and LOP transistors, "polycrystalline silicon film 54 is formed on the high-k film." (TSMC-1005, 6:66-7:7, Figure 7 (below-left).) A "resist mask of a width of the gate electrode is formed on the polycrystalline silicon film 54 ... and etching is performed using the resist mask to process the polycrystalline silicon film 54 and the high-k film 28 to have the width of the gate electrode 32." (TSMC-1005, 7:13-19.) "Thereby, a gate electrode 32 and a gate insulating film are formed in each of the regions for LOP, LSTP, and high withstand voltage." (TSMC-1005, 7:20-22, Figure 8 (below-right).)

Torii, Figure 7 (left), Excerpt of Figure 8 (right)

Because the gate electrodes of both the LSTP and LOP transistors are formed from the same polycrystalline silicon film layer, "the first and second gate electrodes are made of an identical material" [14]. (TSMC-1003, ¶138; see also, §VI.B.3.c (discussing gate electrode).)

#### E. Claim 15

Torii discloses "the effective work function of the first MIS transistor is higher than an effective work function of the second MIS transistor." (TSMC-1003, ¶¶139-144.)

Torii's device includes an LSTP transistor ("first MIS transistor") with a gate insulating film comprising silicon oxynitride film 24 and high-k film 28 and an LOP transistor ("second MIS transistor") with a gate insulating film comprising silicon oxynitride film 22 and high-k film 28. (TSMC-1005, 5:14-17, 5:33-36, 6:55-7:5; Figure 1 (below).)

Torii, Excerpt from Figure 1 with enlargements

The '779 patent relates a transistor's "effective work function" to the transistor's EOT. Specifically, the '779 patent states "since an EOT of the gate insulating film of the first MIS transistor increases, an effective work function of the first MIS transistor increases." (TSMC-1001, 4:29-31, 13:23-27 ("Accordingly, the EOT of the gate insulating film 52a of the first pMIS transistor and that of the gate insulating film 52c of the first nMIS transistor increase, **thereby causing** the effective work functions of the first pMIS transistor and the first nMIS transistor to increase").)

Torii teaches the high-k film of both the LSTP and LOP transistors is formed in the same process step and therefore has the same thickness and is formed of the

same material (i.e., same dielectric constant). (TSMC-1005, 6:66-7:3.)

Accordingly, the contribution of the high-k film to the EOT of both transistors is the same, "about 0.5 nm" as taught by Torii. (TSMC-1005, 5:36-37; TSMC-1003, ¶141; See §VI.C.)

As discussed in §VI.D, the gate electrodes of the LSTP and LOP transistors are the same. When comparing the two transistors' EOT as shown in the below equation, the high-k contributions effectively cancel one another (and are therefore greyed out). (TSMC-1003, ¶¶140-141.)

EOT (LSTP) EOT (LOP)

$$\left(\frac{t_{28}}{\epsilon_{28}}\right) \epsilon_{SiO_2} + \left(\frac{t_{24}}{\epsilon_{24}}\right) \epsilon_{SiO_2} [1.0 \text{ nm}] > \left(\frac{t_{28}}{\epsilon_{28}}\right) \epsilon_{SiO_2} + \left(\frac{t_{22}}{\epsilon_{22}}\right) \epsilon_{SiO_2} [0.7 \text{ nm}]$$

Torii teaches the contribution of the silicon oxynitride film 24 to the LSTP transistor's EOT is greater than contribution of the silicon oxynitride film 22 to the LOP transistor's EOT: "thickness of the silicon oxynitride film 24 ["first interface layer"] ... is about 1.3 nm; and the EOT [equivalent oxide thickness] thereof is about 1.0 nm" (TSMC-1005, 5:23-25.) and "the thickness of the silicon oxynitride film 22 ["second interface layer"] ... is about 0.9 to 0.95 nm, and the EOT thereof is about 0.7 nm." (TSMC-1005, 5:20-23.)

Accordingly, because the LSTP transistor ("first MIS transistor") has a greater EOT than the LOP transistor ("second MIS transistor"), the "effective work

function of the" LSTP transistor ("first MIS transistor") "is higher than an effective work function of the" LOP transistor ("second MIS transistor"), according to the disclosure of the '779 patent. (TSMC-1003, ¶¶139-144.)

# VII. GROUND 2: Combination of Torii and Mise Renders Claims 8-11 Obvious.

Torii discloses the "first and second MIS transistors" of its semiconductor device are "pMIS transistors" [8A] or alternatively "nMIS transistors" [10A]. (§VI.B.2; TSMC-1005, 10:39-42.) Torii however does not explicitly disclose that when "the first and second MIS transistors are pMIS transistors" [8A], "the first gate insulating film further includes a first cap film formed on the first high dielectric constant insulating film and containing aluminum, and the second gate insulating film further includes a second cap film formed on the second high dielectric constant insulating film and containing aluminum" [9] or when "the first and second MIS transistors are nMIS transistors" [10A], "the first gate insulating film further includes a first cap film formed on the first high dielectric constant insulating film and containing lanthanum, and the second gate insulating film further includes a second cap film formed on the second high dielectric constant insulating film and containing lanthanum" [11]. Mise provides these teachings.

#### A. Combination Overview

#### 1. Mise

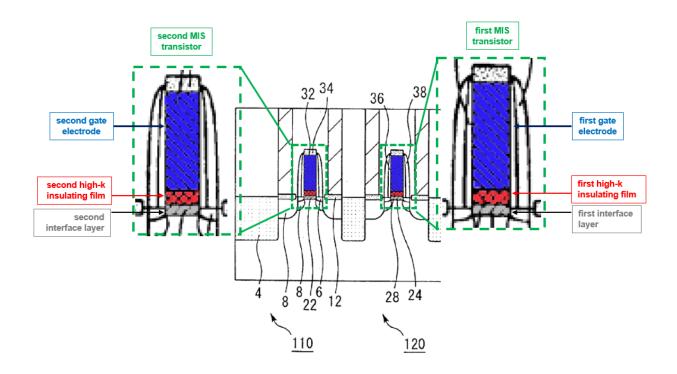

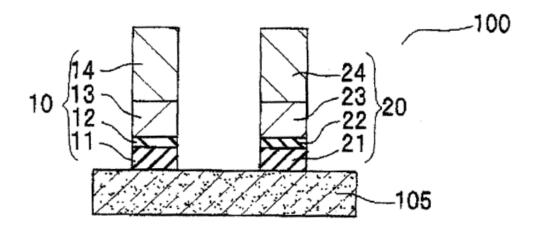

Mise describes a CMOS device having "an n-type MOSFET 101 and a p-type MOSFET 1027." (TSMC-1006, ¶69, Figure 1(k) (below).) The n-type MOSFET includes gate stack 10 having gate insulation layer 11 "composed of a high-k material such as HfLaO or HfMgO", cap layer 12 "composed of MgO or LaO", and gate metal layers 13 and 14. (TSMC-1006, ¶71.) The p-type MOSFET includes gate stack 20 having gate insulation layer 21 "composed of a high-k material such as HfAlO", cap layer 22 "composed of AlO", and gate metal layers 23 and 24. (TSMC-1006, ¶72.) Mise discloses gate metal layers 13 and 23 are "composed of a mid-gap material ... such as TiN, TaN, TaSiN, NiSi, PtS, or CoSi<sub>2</sub>" and gate metal layers 14 and 24 are "made of a low resistance material such as W." (TSMC-1006, ¶71, ¶72 ("gate metal layers 23 and 24 are composed of the same materials as those of the gate metal layers 13 and 14").)

<sup>&</sup>lt;sup>7</sup> Mise's specification contains a typographical error, stating p-type MOSFET 102 has p-type well region 120 and n-type MOSFET 101 has n-type well region 110. (TSMC-1006, ¶70.) A POSITA would have understood the p-type MOSFET has an n-type well and the n-type MOSFET has a p-type well. (TSMC-1003, ¶149, *citing* TSMC-1017, 8-9.)

Mise, Figure 1(k)

#### 2. Motivation to Combine

Both Torii and Mise are in the same field as the '779 patent— "semiconductor devices and methods for fabricating the same." (TSMC-1001, 1:15-16; TSMC-1005, 1:9-10; TSMC-1006, ¶1.) A POSITA would have motivated to make at least the following two combinations of Mise's teachings with Torii.

# a. Combining Mise's teaching of a two-layer metal gate electrode with Torii.

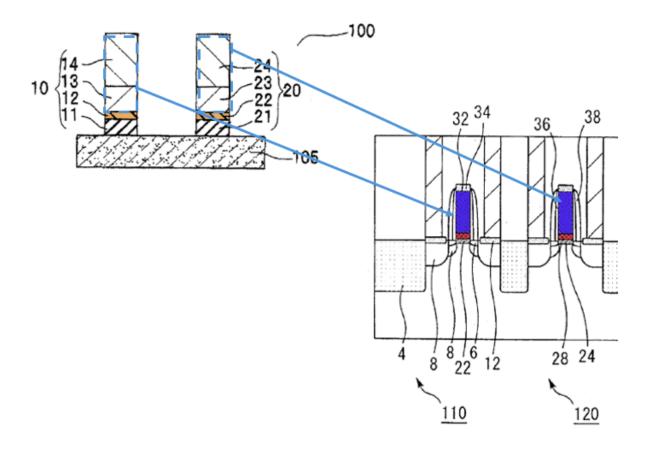

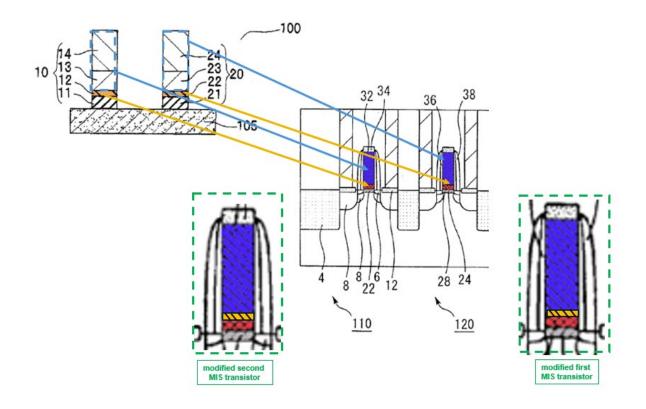

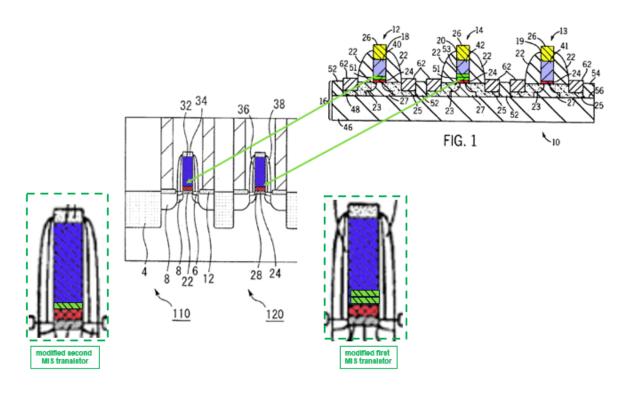

A POSITA would have been motivated to integrate Mise's teaching of using a two-layer metal gate electrode in Torii's transistors, as illustrated below. (TSMC-

1003, ¶¶153-155.)

Mise, Figure 1 (left); Torii, Figure 1 (right)

Torii's LSTP and LOP transistors include a "gate insulating film" having a high-k film and a polysilicon "gate electrode" on the high-k film. (See TSMC-1005, 5:33-36, 5:42, 6:66-7:15; §VI.B.3.) A POSITA would have been motivated to make the above combination because the challenges with using high-k dielectrics with polysilicon ("polySi") gates were known prior to the '779 patent. (TSMC-1003, ¶154.) For example, due to Fermi level pinning at the interface between high-k dielectrics and polySi, the threshold voltage shifts. (TSMC-1006, ¶23; TSMC-1018, 1.) PolySi/high-k transistors also exhibit lower channel

mobility. (*See* TSMC-1018, 1.) A POSITA would have understood that metal gates are more effective with high-k gate dielectrics but require additional adjustment to achieve an optimal threshold voltage which, as discussed below, is a motivation to use a cap layer. (*See* TSMC-1018, 1; TSMC-1003, ¶¶154-155.) A POSITA would have therefore been motivated to improve Torii's device using the metal gate electrodes discussed by Mise to avoid Fermi level pinning and improve channel mobility. (TSMC-1003, ¶¶153-155.)

### b. Combining Mise's teaching of a cap layer with Torii.

A POSITA would also have been motivated to integrate a cap layer over the high-k dielectric as taught by Mise in Torii's gate stack in addition to using Mise's gate electrode, as illustrated in the figure below. (TSMC-1003, ¶¶156-162.) Specifically, a POSITA would have been motivated to include an Al containing cap layer in Torii's p-type MISFETs and a La containing cap layer in Torii's n-type MISFETs. (TSMC-1003, ¶156.)

Mise, Figure 1 (top-left); Torii, Figure 1 (top-right) enlargements showing transistors of combination of Torii and Mise

A POSITA would have been motivated to make the above combination to improve transistor operation. (TSMC-1003, ¶¶157-162.) A POSITA would have understood a cap layer helps reduce defects that negatively impact electrical performance when metal gate electrodes are used. (TSMC-1003, ¶157; see also, TSMC-1009, 5:25-31, 5:38-39 ("Metal gate electrodes may also benefit from use of a capping layer over the bulk dielectric material [i.e., gate dielectric]").) For example, use of a cap layer helps reduce leakage current by misaligning "the grain boundaries within the layers." (See TSMC-1009, 5:21-24.) A POSITA would have also understood the cap layer improves the interface between the gate electrode

and gate insulating film, alleviating compatibility issues. (TSMC-1003, ¶157; see TSMC-1009, 5:25-35.) A POSITA would have also understood the cap layer permits the threshold voltage of the transistor to be adjusted. (TSMC-1003, ¶¶158-162.) Indeed, Mise discloses use of an AlO/LaO cap layer for the pMOS/nMOS transistors respectively to adjust the threshold voltage, as discussed further below. (See, e.g., TSMC-1006, ¶¶154, 183-193, 195.)

A POSITA would have been motivated to use a cap film containing aluminum as taught by Mise with Torii's pMIS transistors. (TSMC-1003, ¶158.) Mise's gate electrode includes a gate metal layer 13/23 composed of a mid-gap material. (TSMC-1006, ¶¶71-72, TSMC-1019, 1.) A POSITA would have understood use of aluminum in the cap layer lowers the threshold voltage, making it ideal for pMOS devices. (*See* TSMC-1006, ¶¶154, 183-193, 195, Figure 11; TSMC-1020, 441-444; *see also*, TSMC-1021, 12:8-23; TSMC-1003, ¶158.)

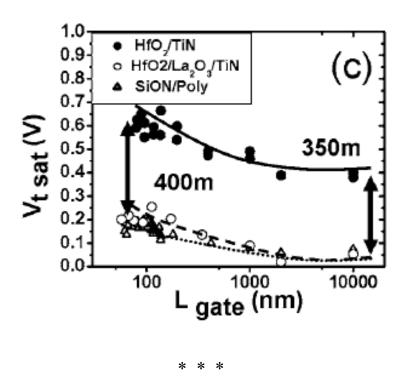

A POSITA would have been motivated to use a cap film containing lanthanum as taught by Mise with Torii's nMIS transistors. (TSMC-1003, ¶¶159-162.) Mise's gate electrode includes a gate metal layer 13/23 "composed of a midgap material" which is too high for an nMIS transistor. (See TSMC-1006, ¶¶71-72, Figure 11; TSMC-1019, 1 (noting the "resulting threshold voltages" for a HfO<sub>2</sub> dielectric and TiN electrode "are unacceptably high and an additional threshold adjustment technique is needed to produce devices suitable for high performance

logic applications").) A POSITA would have therefore been motivated to form the cap layer in the combination of Torii and Mise using lanthanum to adjust the threshold voltage to a value suitable for nMIS devices. (TSMC-1003, ¶159, *citing* TSMC-1019, 1 ("We have recently solved this problem and shown that be introducing ultrathin La<sub>2</sub>O<sub>3</sub> cap layers between the HfO<sub>2</sub> dielectric and TiN electrode, the threshold voltage can be controllably shifted to a position ideal for nMOSFETs").)

The following figure from Guha (TSMC-1019) highlights this motivation. For example, Guha explains a TiN gate electrode layer by itself on a high-k dielectric (i.e., without an intervening cap layer) results in a threshold voltage of 0.6V at 100 nm gate length. (*See*, TSMC-1019, 2.) A POSITA would have understood this threshold voltage is too high for an nMIS device. (TSMC-1003, ¶160.) The traditional nMOS device with SiON and poly-silicon gate is shown in the bottom curve. As shown, a lanthanum containing cap layer (HfO<sub>2</sub>-La<sub>2</sub>O<sub>3</sub>-TiN) shifts the threshold voltage closer to that of traditional device.

Adding cap layers and using metal gate layers in Torii's transistors would be nothing more than using a known technique (e.g., incorporating cap layers between the high-k dielectric and the gate electrode material and using metal gate layers according to Mise's teachings) to improve similar devices in the same way for the above reasons. (TSMC-1003, ¶¶155, 162.) A POSITA would have had a reasonable expectation of success and the results of the combination would have been predictable because Mise forms the cap layers and metal gate layers through conventional, well-known processes. (*Id.*) For example, Mise describes that its cap layers are "made by the ALD method, the MOCVD method, the sputtering method, or the like" and its metal layers are formed "by the sputtering method." (TSMC-1006, ¶80, 85, 94.) A POSITA would have known these were conventional and

well known deposition methods in semiconductor fabrication prior to the '779 patent. (TSMC-1003, ¶¶155, 162.) Further, high-k metal gate devices were known before the '779 patent. (*See, e.g.*, TSMC-1013, Figure 5.1.18; TSMC-1009, 4:38-40 (indicating either a metal or polysilicon gate can be used with a high-k dielectric).)

#### B. PMIS Claims 8-9

Torii teaches the "first and second MIS transistors are pMIS transistors" [8A]: "the present invention may be applied to the case wherein a p-type transistor is formed." (TSMC-1005, 10:40-42; TSMC-1003, ¶163; §VI.B.2.)

The combination of Torii and Mise uses a cap layer containing aluminum on the high-k insulating film in Torii's LSTP and LOP pMIS transistors, as taught by Mise. (§VII.A.2; TSMC-1006, ¶72 (cap layer 22 of pMOS transistor "is composed of AlO").) Thus, the combination provides "the first gate insulating film further includes a first cap film formed on the first high dielectric constant insulating film and containing aluminum" [9A] and "the second gate insulating film further includes a second cap film formed on the second high dielectric constant insulating film and containing aluminum" [9B]. (TSMC-1003, ¶164.)

Torii teaches the material for the high-k gate insulating film in its transistors includes hafnium aluminate ( $Hf_xAl_{1-x}O_y$ ) and alumina ( $Al_2O_3$ ). (TSMC-1005, 10:8-16.) Mise similarly teaches the pMOS transistor's gate insulating film "is

composed of a high-k material such as **HfAlO**." (TSMC-1006, ¶72.) A POSITA would have understood the high-k gate insulating material in the combination contains aluminum, as taught by Torii and Mise, at least as a result of diffusion during later thermal processing of Torii (e.g., source-drain activation, silicidation). (*See, e.g.,* TSMC-1005, 7:54-58, 7:63-66; TSMC-1003, ¶166; TSMC-1021, 11:1-26 (describing Al diffusion through the gate insulating stack); TSMC-1022, ¶19 (mentioning diffusion of metal atoms across the gate stack).) Thus, in the combination of Torii and Mise, the "high dielectric constant insulating films" of both the LSTP and LOP transistors "contain aluminum" [8B]. (TSMC-1003, ¶¶165-168.)

#### C. NMIS Claims 10-11

Torii teaches the "first and second MIS transistors are nMIS transistors"

[10A]: LOP transistor and LSTP transistor are "n-type transistor[s]." (TSMC-1005, 10:39-40; TSMC-1003, ¶169; §VI.B.2.)

The combination of Torii and Mise uses a cap layer containing lanthanum on the high-k insulating film in Torii's LSTP and LOP nMIS transistors, as taught by Mise. (§VII.A.2; TSMC-1006, ¶71 (cap layer 22 of nMOS transistor "is composed of MgO or LaO").) Thus, in the combination of Torii and Mise, "the first gate insulating film further includes a first cap film formed on the first high dielectric constant insulating film and containing lanthanum" [11A] and "the second gate

insulating film further includes a second cap film formed on the second high dielectric constant insulating film and containing lanthanum" [11B]. (TSMC-1003, ¶170.)

Torii teaches the high-k insulating film in its transistors include lanthanum oxide. (TSMC-1005, 10:8-16.) Mise similarly teaches the gate insulation film of its nMOS transistor "is composed of a high-k material such as **HfLaO** or HfMgO." (TSMC-1006, ¶71.) A POSITA would have also understood the high-k material in the combination contains lanthanum, as taught by Torii and Mise, at least because of diffusion as a result of thermal processing as discussed in §VII.B. (*See, e.g.,* TSMC-1005, 7:54-58 (describing heat treatment to activate source/drain), 7:63-66 (describing heat treatment for silicidation); TSMC-1003, ¶166; TSMC-1022, ¶19 (discussing diffusion of metal atoms across the gate stack).) Thus, in the combination of Torii and Mise, the "high dielectric constant insulating films" of both the LSTP and LOP transistors "contain lanthanum" [10B]. (TSMC-1003, ¶171-172.)

#### VIII. GROUND 3: Combination of Torii and Yu Renders Claim 15 Obvious.

Torii anticipates claim 15 based on the '779 patent's disclosure. (§VI.E.)

Torii does not disclose modifying the work function of a metal gate electrode to adjust the effective work function (and threshold voltage) of a transistor under PO's litigation allegations. (See §V.) However, Yu discloses varying the metal gate

work function of transistors having the same conductivity type formed on the same substrate.

#### A. Yu Overview

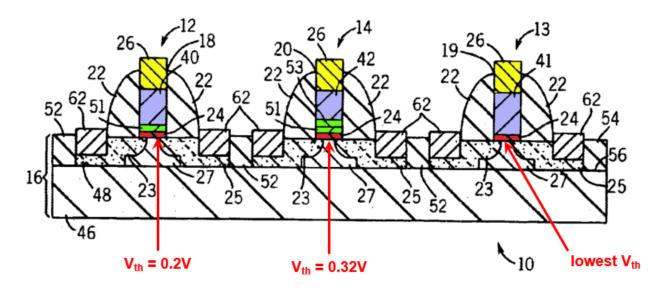

Yu generally relates "to an integrated circuit (IC) and the fabrication of an integrated circuit" which is a semiconductor device and is therefore in the same field as Torii and the '779 patent. (TSMC-1008, 1:27-28; *see also* TSMC-1001, 1:15-16; TSMC-1005, 1:9-10.) Yu specifically "relates to an integrated circuit with transistors having multiple threshold voltage values." (TSMC-1008, 1:28-31.) Yu's integrated circuit includes transistors 12, 13, and 14 having "a threshold voltage between 0.15V and 0.4V or less." (TSMC-1008, 5:16-17, Figure 1 (below).) Each transistor is "disposed on a substrate 16" separated by isolation structures 52. (TSMC-1008 5:9-11, 6:56-63.) Although Yu teaches substrate 16 "provides an SOI substrate," Yu discloses transistors 12, 13, and 14 could "utilize the principles of the present invention on a bulk-type substrate." (TSMC-1008, 6:65-67.)

Yu, Figure 1

Gate stacks 18, 19, and 20 include gate dielectric 24 (shaded red) and doped polysilicon gate conductor 40, 41, and 42 (shaded blue). (TSMC-1008, 5:30-34.) The threshold voltages of transistors 12 and 14 are adjusted by inserting metal layer 51 (shaded green) in gate stack 18 and metal layers 51 and 53 (shaded green) in gate stack 20. (TSMC-1008, 5:51-53.)

#### B. Claim 15

The combination of Torii and Yu discloses or suggests "an effective work function of the first MIS transistor is higher than an effective work function of the second MIS transistor" under PO's litigation allegations. (TSMC-1003, ¶¶173-203; §V.)

Torii discloses a semiconductor device composed of LOP, LSTP, and high withstand voltage transistors. As discussed in §VI.B.3.c, to form the gate

electrodes of Torii's transistors, non-doped polycrystalline silicon film 54, "a material film for gate electrodes", "is formed on the high-k film 28", as shown in Figure 7 (top). (TSMC-1005, 7:6-9.) "Thereafter, impurity ions for the gate electrodes are implanted into the non-doped polycrystalline silicon film 54." (TSMC-1005, 7:10-12.) Polycrystalline silicon film 54 is then "processed for a gate electrode 32 of each region", illustrated in the excerpt from Figure 8 (bottom). (TSMC-1005, 7:13-15.)

Torii, Figure 7 (top), Excerpt from Figure 8 (bottom)

A POSITA would have been motivated to combine Yu's teachings regarding inserting metal layers into the LOP and LSTP nMIS transistors of Torii to vary the work functions of the gate electrode and hence the threshold voltages of the LOP and LSTP nMIS transistors. (TSMC-1003, ¶194; TSMC-1005, 10:39-40;

§§VI.B.2.) Because both Torii and Yu's gate electrode use polysilicon, a POSITA would have understood that Yu's process steps associated with forming the metal layers by masking and metal layer deposition can be used with Torii's fabrication process. (TSMC-1003, ¶194) Specifically, as illustrated below, a POSITA would have been motivated to insert a metal layer into the LOP transistor ("second MIS transistor") and first and second metal layers into the LSTP transistor ("first MIS transistor"), as taught by Yu using a similar process as Yu. (Id.)

Torii, Modified Figure 1 (left); Yu, Figure 1 (right)

In Yu, the thickness and types of materials for layers 51 and 53 used in the gate stacks "can be controlled to control the adjustment to the work function, thereby selecting threshold voltage." (TSMC-1008, 6:1-3.) Yu teaches that "[i]f

transistors 12 and 14 are N-channel transistors, transistor 12 has a lower threshold voltage than transistor 14." (INTEL-1008, 6:26-31.) For example, if transistors are nMOS transistors, transistor 12 "has a threshold voltage of approximately 0.2V" and transistor 14 "has a threshold voltage of approximately 0.32V." (TSMC-1008, 6:36-38.) Transistor 13 "has the lowest threshold voltage." (TSMC-1008, 6:34-35.) That is, for nMOS transistors, the transistor with two metal layers has higher threshold voltage than the transistor with one metal layer which has a higher threshold voltage than the transistor without a metal layer. (TSMC-1003, ¶195.)

Yu, Figure 1

Thus, in the combination of Torii and Yu, the LSTP nMIS transistor (with two added metal layers) has a higher threshold voltage than the LOP nMIS transistor (with one added metal layer), as taught by Yu, consistent with Torii's disclosure that the LSTP has a higher threshold voltage than LOP transistor.

Based on this disclosure, the combination of Torii and Yu also discloses or suggests claim 15 under PO's litigation allegations. PO alleges in the co-pending district court litigation a transistor with an additional metal layer in its gate electrode would demonstrate a slightly higher effective work function than another MIS transistor missing this layer because the additional layer allegedly possesses a higher effective work function. The combination of Torii and Yu teaches addition of a metal layer with a higher work function into the gate stack of the LSTP transistor ("first" MIS transistor).

In the combination of Torii and Yu, the LSTP nMIS transistor has two metal layers 51 and 53 and the LOP nMIS transistor has a single metal layer 51. In Yu, layers 51 and 53 "can be nickel or titanium layers formed on top of each other or on top of gate dielectric 24." (TSMC-1008, 5:56-58; *see also*, TSMC-1008, 7:22-30.) Yu stresses the second metal layer (layer 53) "preferably has a different work function associated with it than" the first layer. (TSMC-1008, 7:63-67.)

Accordingly, Yu teaches two options for the LSTP gate stack: Ti (layer 51)-Ni (layer 53) or Ni (layer 51)-Ti (layer 53). Each ordering would have been obvious to try because only two alternatives exist. *See KSR Int'l Co. v. Teleflex Inc.*, 550 U.S. 398, 421 (2007). A POSITA would have had a reasonable expectation of success in pursuing both ordering alternatives. (TSMC-1003, ¶198.) Indeed, the order of depositing Ti and Ni layers is "the product **not of innovation** but of ordinary skill

and **common sense**." See Perfect Web Techs., Inc. v. InfoUSA, Inc., 587 F.3d 1324, 1331 (Fed. Cir. 2004), quoting KSR, 550 U.S. at 421.

A POSITA would have understood that Ti is a low work function metal ( $\Phi_m$  ~ 4eV) and Ni is a high work function metal ( $\Phi_m$  ~ 5eV). (*See* TSMC-1033<sup>8</sup>, 200.) Thus, when layer 51 is Ti ( $\Phi_m$  ~ 4eV) and layer 53 is Ni ( $\Phi_m$  ~ 5eV), the additional layer 53 in the LSTP transistor has a higher work function than layer 51, the only layer present in the LOP transistor. According to PO's litigation allegations, the LSTP transistor (having both Ti (layer 51) and Ni (layer 53)) will exhibit a higher effective work function than the LOP transistor (having only the Ti layer (layer 51)). (TSMC-1003, ¶199.)

The combination of Torii and Yu therefore discloses or suggests "an effective work function of the first MIS transistor is higher than an effective work function of the second MIS transistor" under PO's litigation allegations.

<sup>&</sup>lt;sup>8</sup> Polishchuk expresses the work function of Ti and Ni in volts (V) rather than the customary energy units of electron volts (eV). (TSMC-1003, ¶199.)

Because an eV is defined as the product of voltage (V) and the elementary charge (e), a POSITA would recognize 1eV is equivalent to 1V × e, or that 1V produces 1eV of energy for a single electron (e). (*Id.*) That is, in this context, V and eV are interchangeable. (*Id.*)

A POSITA would have been motivated to make the above combination for numerous reasons. (TSMC-1003, ¶¶200-203.) Torii suggests, and a POSITA would have known, that LOP and LSTP nMIS transistors require different threshold voltages. (TSMC-1005, 2:51-54, 3:2-10; TSMC-1016, 11, 17, 21; TSMC-1003, ¶200.). A POSITA would have been motivated to combine Torii and Yu to fine tune the gate effective work functions of the LOP and LSTP transistors by adding metal layers so that their threshold voltages can be set to the desired values without having to rely on gate dielectric thickness engineering and channel and gate electrode doping engineering, which can be burdensome and fabrication intensive. (TSMC-1003, ¶200-201.) Yu confirms this motivation, explaining that "[u]tilizing channel implants to adjust the threshold voltages of transistors can be problematic because transistor short-channel performance is very susceptible to process variations" which "is particularly problematic as transistors become smaller and packing densities increase." (TSMC-1008, 3:27-37.) Accordingly, a POSITA would have been motivated to modify the metal work function to fine tune the threshold voltages of Torii's nMIS transistors. (TSMC-1003, ¶¶200-201.)

A POSITA would have been further motivated to apply Yu's teaching in Torri to address the challenges with using high-k dielectrics with polysilicon gates, as discussed in §VII.A.2 in the combination of Torii and Mise. (TSMC-1003, ¶202.) For example, the metal layers in Yu shield Torii's polysilicon gate electrode

from Fermi level pinning by spatially moving the polysilicon gate away from the high-k dielectric. (*Id.*)

Finally, the combination is merely the application of a known technique (inserting one or more metal layers into the gate stack and adjusting the thicknesses and types of materials of those meta layers) to a known device (Torii's semiconductor device) ready for improvement for the above reasons. (TSMC-1003, ¶203.) Yu's gate electrode uses polysilicon, like Torii's gate electrode. (TSMC-1005, 7:13-19; TSMC-1008, 5:30-34.) Therefore, applying Yu's teaching regarding inserting one or more metal layers to Torii's transistors would be nothing more than applying the fabrication process disclosed in Yu for forming the additional metal layers of the gate electrode to Torii's fabrication process. (TSMC-1003, ¶203.) The results of the combination would have been predictable and a POSITA would have had a reasonable expectation of success. (Id.) Both Yu and Torii describe devices having transistors of the same conductivity device with different threshold voltages and Yu teaches that its technique is applicable to both SOI and "bulk-type substrates." (TSMC-1008, 6:25-35, 6:65-67; see also, 5:60-67.) Moreover, Yu, filed a decade before the '779 patent, uses conventional photolithography and processes to add the metal layers to a gate stack. Such conventional techniques would have been well-known and understood by a POSITA. (TSMC-1003, ¶203.)

Thus, the combination of Torii and Yu renders claim 15 obvious under PO's litigation allegations.

## IX. GROUND 4: Gilmer Renders Claims 1, 12-15 Obvious.

#### A. Gilmer

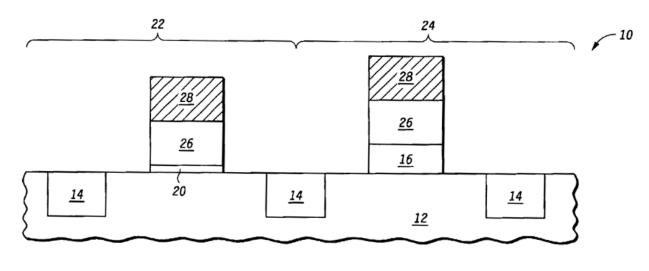

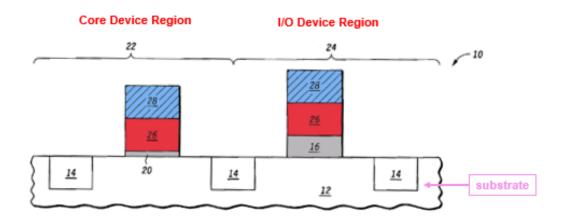

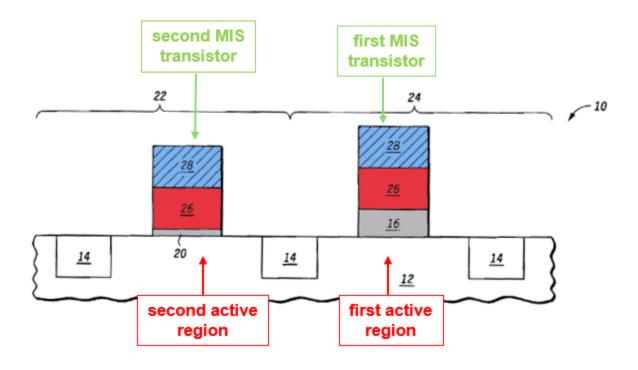

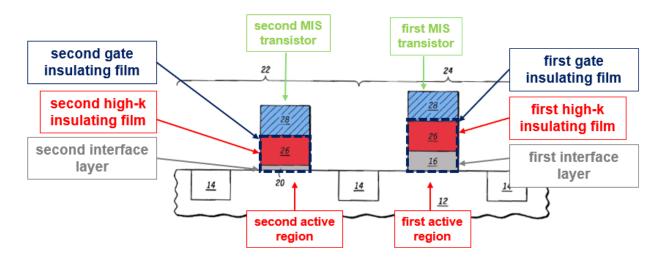

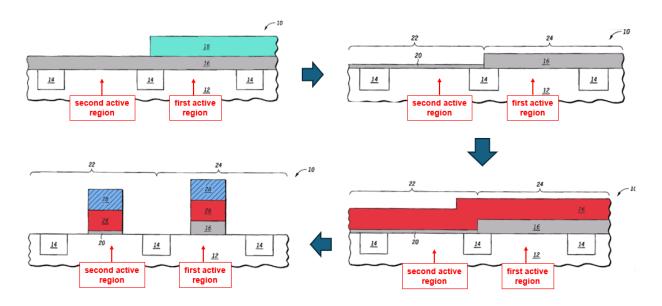

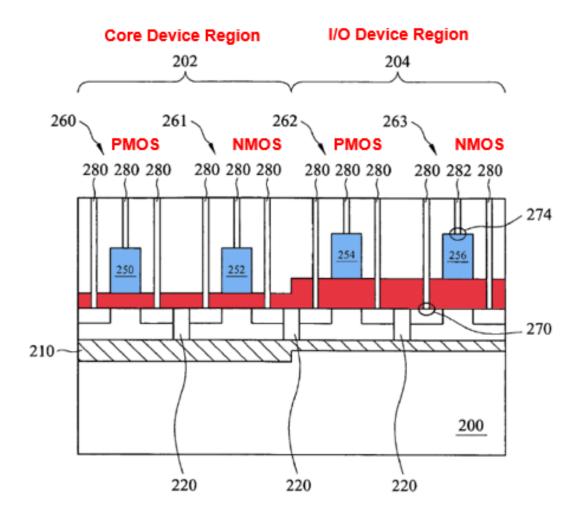

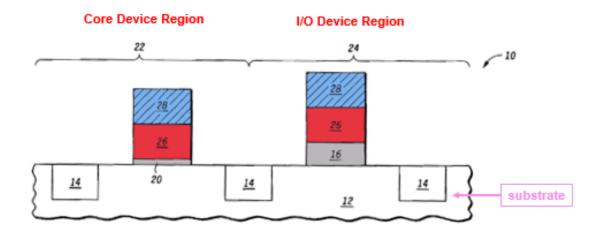

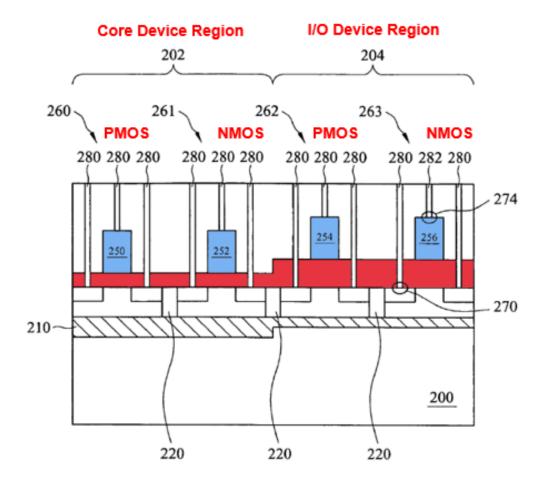

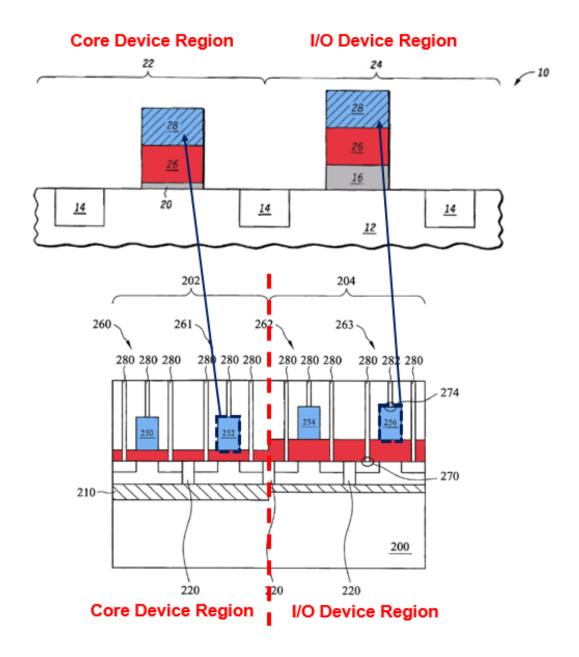

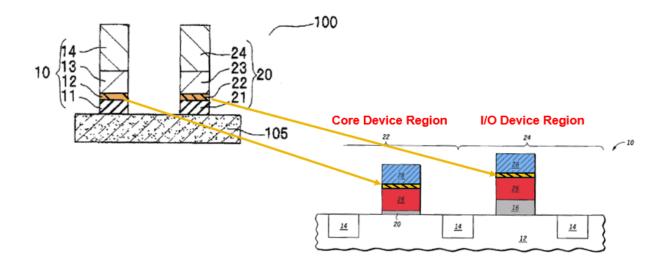

Gilmer discloses a semiconductor device "having dual gate dielectric thicknesses and utilizing high-k gate dielectric materials such as metal oxides." (TSMC-1009, 1:7-10.) Gilmer's device 10 includes transistors in core region 22 and I/O region 24. (*See* TSMC-1009, 4:43-47, Figure 4 (below).) Core transistor 22 includes a gate stack having gate dielectric 20, high-k dielectric (metal oxide) 26, and gate electrode 28. (TSMC-1009, 4:35-38.) I/O transistor 24 includes gate dielectric 16, high-k dielectric (metal oxide) 26, and gate electrode 28. (TSMC-1009, 4:35-38.)

Gilmer, Figure 4

#### **B.** Independent Claim 1

## 1. Preamble [1P]

Gilmer discloses "a semiconductor device" [1P]: "present invention relates generally to semiconductor devices." (TSMC-1009, 1:7-8; see also, TSMC-1009, Abstract, 1:57-60 (Figures 1-4 illustrate "views of a semiconductor device ... as it undergoes processing")); TSMC-1003, ¶211.)

## 2. Limitations [1A]-[2A]

Gilmer teaches or at least suggests "[1A] a first MIS transistor and [2A] a second MIS transistor of an identical conductivity type provided on an identical semiconductor substrate." (TSMC-1003, ¶¶212-224.)

Gilmer's "semiconductor device 10 includes a **semiconductor substrate 12** which in a preferred embodiment is a single crystal silicon substrate." (TSMC-1009, 2:38-40.) Gilmer's device "includes two different device regions, namely a core device region 22 and an I/O device region 24." (TSMC-1009, 2:59-60.) Core device region 22 and I/O device region 24 each includes a "*transistor*." (*See* TSMC-1009, 4:43-44 ("conventional processing occurs to complete the **transistor**"; TSMC-1003, ¶212.)

Gilmer, Figure 4