| UNITED STATES PATENT AND TRADEMARK OFFICE  |

|--------------------------------------------|

| BEFORE THE PATENT TRIAL AND APPEAL BOARD   |

| PHISON ELECTRONICS CORPORATION,            |

| Petitioner                                 |

| V.                                         |

| VERVAIN, LLC,                              |

| Patent Owner                               |

|                                            |

| Inter Partes Review Case No. IPR2025-00212 |

| Patent 8,891,298                           |

|                                            |

PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT NO. 8,891,298

#### **TABLE OF CONTENTS**

| I.    | INTRODUCTION:1                                                                                                                 |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

| II.   | MANDATORY NOTICES UNDER 37 C.F.R. § 42.8:4                                                                                     |

| A.    | REAL PARTY-IN-INTEREST UNDER 37 C.F.R. § 42.8(B)(1)):                                                                          |

| В.    | RELATED MATTERS UNDER 37 C.F.R. § 42.8(B)(2):4                                                                                 |

| C.    | LEAD AND BACK UP COUNSEL UNDER 37 C.F.R. § 42.8(B)(3):                                                                         |

| D.    | SERVICE INFORMATION UNDER 37 C.F.R. § 42.8(B)(4):5                                                                             |

| III.  | ADDITIONAL REQUIREMENTS:6                                                                                                      |

| A.    | PAYMENT OF FEES UNDER 37 C.F.R. § 42.15:6                                                                                      |

| В.    | TIMING UNDER 37 C.F.R. § 42.102:                                                                                               |

| C.    | GROUNDS FOR STANDING UNDER 37 C.F.R. § 42.104(A):6                                                                             |

| IV.   | NAND FLASH TECHNOLOGY BACKGROUND6                                                                                              |

| A.    | CHARACTERISTIC NATURE OF NAND FLASH MEMORY7                                                                                    |

| В.    | CHARACTERISTIC NAND FLASH MEMORY MANAGEMENT9                                                                                   |

| C.    | INTRODUCTION OF MLC AND SLC FLASH10                                                                                            |

| D.    | KNOWN HYBRID USE OF SLC AND MLC NAND FLASH MODULES WITH STRATEGIES OF PREFERENTIAL MAPPING, WEAR LEVELING AND ERROR MANAGEMENT |

| V.    | THE '298 PATENT: SPECIFICATION                                                                                                 |

| VI.   | THE CHALLENGED CLAIMS OF THE '298 PATENT (37 C.F.R. § 42.104(B)(1):                                                            |

| VII.  | PERSON OF ORDINARY SKILL IN THE ART16                                                                                          |

| VIII. | . 37 C.F.R. § 42.104(B)(3): CLAIM CONSTRUCTION                                                                                 |

| IX. | GROUND 1: THE CHALLENGED CLAIMS ARE OBVIOUS OVER GAVENS, INCLUDING INCORPORATED REFERENCES, IN VIEW OF KNOWLEDGE OF THE POSITA                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | CLAIM 1 IS OBVIOUS OVER GAVENS, INCLUDING INCORPORATED REFERENCES, IN VIEW OF KNOWLEDGE OF THE POSITA20                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.  | [1a] at least one MLC non-volatile memory module comprising a plurality of individually erasable blocks;                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.  | [1b] at least one SLC non-volatile memory module comprising a plurality of individually erasable blocks;                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.  | [1c] a controller coupled to the at least one MLC non-volatile memory module and the at least one SLC non-volatile memory module wherein the controller is adapted to;                                                                                                                                                                                                                                                                                                                                |

| 4.  | [1d] a) maintain an address map of at least one of the MLC and SLC non-volatile memory modules, the address map comprising a list of logical address ranges accessible by a computer system, the list of logical address ranges having a minimum quanta of addresses, wherein each entry in the list of logical address ranges maps to a similar range of physical addresses within either the at least one SLC non-volatile memory module or within the at least one MLC non-volatile memory module; |

| 5.  | [1e] b) determine if a range of addresses listed by an entry and mapped to a similar range of physical addresses within the at least one MLC non-volatile memory module, fails a data integrity test, and, in the event of such a failure, the controller remaps the entry to the next available equivalent range of physical addresses within the at least one SLC non-volatile memory module;                                                                                                       |

| 6.  | [1f] c) determine which of the blocks of the plurality of the blocks in the MLC and SLC non-volatile memory modules are accessed most frequently by maintaining a count of the number of times each one of the blocks is accessed; and                                                                                                                                                                                                                                                                |

| 7.  | [1g] d) allocate those blocks that receive the most frequent writes by transferring the respective contents of those blocks to the at least one SLC non-volatile memory module.                                                                                                                                                                                                                                                                                                                       |

| B. CLAIM 2 IS OBVIOUS OVER GAVENS, INCLUDING INCORPORATED REFERENCE IN VIEW OF KNOWLEDGE OF THE POSITA |   |

|--------------------------------------------------------------------------------------------------------|---|

| 1. [2Pre] The system of claim 1,                                                                       | 0 |

| 2. [2] wherein the minimum quanta of address is equal to one block                                     | 0 |

| C. CLAIM 3 IS OBVIOUS OVER GAVENS, INCLUDING INCORPORATED REFERENCE IN VIEW OF KNOWLEDGE OF THE POSITA |   |

| 1. [3Pre] The system of claim 1,                                                                       | 1 |

| 2. [3] wherein the minimum quanta of address is equal to one page                                      | 1 |

| D. CLAIM 4 IS OBVIOUS OVER GAVENS, INCLUDING INCORPORATED REFERENCE IN VIEW OF KNOWLEDGE OF THE POSITA |   |

| 1. [4Pre] The system of claim 1,                                                                       | 1 |

| 2. [4] wherein the MLC non-volatile memory module is NAND flas memory                                  |   |

| E. CLAIM 5 IS OBVIOUS OVER GAVENS, INCLUDING INCORPORATED REFERENCE IN VIEW OF KNOWLEDGE OF THE POSITA |   |

| 1. [5Pre] The system of claim 1,                                                                       | 2 |

| 2. [5] wherein the SLC non-volatile memory module is NAND flas memory                                  |   |

| F. CLAIM 6 IS OBVIOUS OVER GAVENS, INCLUDING INCORPORATED REFERENCE IN VIEW OF KNOWLEDGE OF THE POSITA | - |

| 1. [6Pre] The system of claim 1,                                                                       | 2 |

| 2. [6] wherein the MLC non-volatile memory module is resistive random-accememory (RRAM)                |   |

| G. CLAIM 7 IS OBVIOUS OVER GAVENS, INCLUDING INCORPORATED REFERENCE IN VIEW OF KNOWLEDGE OF THE POSITA |   |

| 1. [7Pre] The system of claim 1,                                                                       | 3 |

| 2. [7] wherein the SLC non-volatile memory module is resistive random-access memory (RRAM)                  |

|-------------------------------------------------------------------------------------------------------------|

| H. CLAIM 8 IS OBVIOUS OVER GAVENS, INCLUDING INCORPORATED REFERENCES, IN VIEW OF KNOWLEDGE OF THE POSITA33  |

| 1. [8Pre] The system of claim 1,                                                                            |

| 2. [8] wherein the MLC non-volatile memory module is phase change memory (PCM)                              |

| I. CLAIM 9 IS OBVIOUS OVER GAVENS, INCLUDING INCORPORATED REFERENCES, IN VIEW OF KNOWLEDGE OF THE POSITA    |

| 1. [9Pre] The system of claim 1,                                                                            |

| 2. [9] wherein the SLC non-volatile memory module is phase change memory (PCM)                              |

| J. CLAIM 10 IS OBVIOUS OVER GAVENS, INCLUDING INCORPORATED REFERENCES, IN VIEW OF KNOWLEDGE OF THE POSITA34 |

| 1. [10Pre] The system of claim 1,                                                                           |

| 2. [10] wherein the SLC non-volatile memory module is magnetic random-access memory (MAGRAM)                |

| K. CLAIM 11 IS OBVIOUS OVER GAVENS, INCLUDING INCORPORATED REFERENCES, IN VIEW OF KNOWLEDGE OF THE POSITA35 |

| 1. [11Pre] The system of claim 1,                                                                           |

| 2. [11] wherein the controller causes the transfer of content on a periodic basis                           |

| X. GROUND 2: THE CHALLENGED CLAIMS ARE OBVIOUS OVER MOSHAYEDI IN VIEW OF KNOWLEDGE OF THE POSITA36          |

| A. CLAIM 1 IS OBVIOUS OVER MOSHAYEDI IN VIEW OF KNOWLEDGE OF THE POSITA                                     |

| 1. [1a] at least one MLC non-volatile memory module comprising a plurality of individually erasable blocks; |

| _           | [1b] at least one SLC non-volatile memory module comprising a plurality of individually erasable blocks;                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8           | [1c] a controller coupled to the at least one MLC non-volatile memory module and the at least one SLC non-volatile memory module wherein the controller is adapted to;                                                                                                                                                                                                                                                                                                                                |

| r<br>l<br>a | [1d] a) maintain an address map of at least one of the MLC and SLC non-volatile memory modules, the address map comprising a list of logical address ranges accessible by a computer system, the list of logical address ranges having a minimum quanta of addresses, wherein each entry in the list of logical address ranges maps to a similar range of physical addresses within either the at least one SLC non-volatile memory module or within the at least one MLC non-volatile memory module; |

| s<br>r<br>t | [1e] b) determine if a range of addresses listed by an entry and mapped to a similar range of physical addresses within the at least one MLC non-volatile memory module, fails a data integrity test, and, in the event of such a failure, the controller remaps the entry to the next available equivalent range of physical addresses within the at least one SLC non-volatile memory module;                                                                                                       |

| a<br>1      | [1f] c) determine which of the blocks of the plurality of the blocks in the MLC and SLC non-volatile memory modules are accessed most frequently by maintaining a count of the number of times each one of the blocks is accessed; and                                                                                                                                                                                                                                                                |

| t           | [1g] d) allocate those blocks that receive the most frequent writes by transferring the respective contents of those blocks to the at least one SLC non-volatile memory module                                                                                                                                                                                                                                                                                                                        |

|             | AIM 2 IS OBVIOUS OVER MOSHAYEDI IN VIEW OF KNOWLEDGE OF THE OSITA                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1. [        | [2Pre] The system of claim 1,                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2. [        | [2] wherein the minimum quanta of address is equal to one block43                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | AIM 3 IS OBVIOUS OVER MOSHAYEDI IN VIEW OF KNOWLEDGE OF THE OSITA                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.                         | [3Pre] The system of claim 1,                                                           |

|----------------------------|-----------------------------------------------------------------------------------------|

| 2.                         | [3] wherein the minimum quanta of address is equal to one page44                        |

|                            | LAIM 4 IS OBVIOUS OVER MOSHAYEDI IN VIEW OF KNOWLEDGE OF THE<br>POSITA44                |

| 1.                         | [4Pre] The system of claim 1,                                                           |

| 2.                         | [4] wherein the MLC non-volatile memory module is NAND flash memory                     |

|                            | LAIM 5 IS OBVIOUS OVER MOSHAYEDI IN VIEW OF KNOWLEDGE OF THE<br>POSITA44                |

| 1.                         | [5Pre] The system of claim 1,                                                           |

| 2.                         | [5] wherein the SLC non-volatile memory module is NAND flash memory                     |

|                            | LAIM 6 IS OBVIOUS OVER MOSHAYEDI IN VIEW OF KNOWLEDGE OF THE<br>POSITA45                |

| _                          |                                                                                         |

|                            | [6Pre] The system of claim 1,                                                           |

| 1.                         |                                                                                         |

| 1.<br>2.<br><b>G.</b> C    | [6Pre] The system of claim 1,                                                           |

| 1.<br>2.<br><b>G.</b> C    | [6Pre] The system of claim 1,                                                           |

| 1.<br>2.<br><b>G.</b> C    | [6Pre] The system of claim 1,                                                           |

| 1. 2. G. C F 1. 2. H. C    | [6] wherein the MLC non-volatile memory module is resistive random-access memory (RRAM) |

| 1. 2. G. C. F. 1. 2. H. C. | [6] wherein the MLC non-volatile memory module is resistive random-access memory (RRAM) |

|                | LAIM 9 IS OBVIOUS OVER MOSHAYEDI IN VIEW OF KNOWLEDGE OF THE POSITA47                          |

|----------------|------------------------------------------------------------------------------------------------|

| 1.             | [9Pre] The system of claim 1,                                                                  |

| 2.             | [9] wherein the SLC non-volatile memory module is phase change memory (PCM)                    |

|                | LAIM 10 IS OBVIOUS OVER MOSHAYEDI IN VIEW OF KNOWLEDGE OF THE POSITA                           |

| 1.             | [10Pre] The system of claim 1,                                                                 |

| 2.             | [10] wherein the SLC non-volatile memory module is magnetic random-access memory (MAGRAM)      |

|                | CLAIM 11 IS OBVIOUS OVER MOSHAYEDI IN VIEW OF KNOWLEDGE OF THE POSITA                          |

| 1.             | [11Pre] The system of claim 1,                                                                 |

|                |                                                                                                |

| 2.             | [11] wherein the controller causes the transfer of content on a periodic basis                 |

| XI.            |                                                                                                |

| XI. (          | GROUND 3: THE CHALLENGED CLAIMS ARE OBVIOUS OVER                                               |

| XI.            | GROUND 3: THE CHALLENGED CLAIMS ARE OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE POSITA49 |

| XI.            | GROUND 3: THE CHALLENGED CLAIMS ARE OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE POSITA   |

| XI. () A. C 1. | GROUND 3: THE CHALLENGED CLAIMS ARE OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE POSITA   |

|                         | having a minimum quanta of addresses, wherein each entry in the list of logical address ranges maps to a similar range of physical addresses within either the at least one SLC non-volatile memory module or within the at least one MLC non-volatile memory module;                                                                                                                           |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.                      | [1e] b) determine if a range of addresses listed by an entry and mapped to a similar range of physical addresses within the at least one MLC non-volatile memory module, fails a data integrity test, and, in the event of such a failure, the controller remaps the entry to the next available equivalent range of physical addresses within the at least one SLC non-volatile memory module; |

| 6.                      | [1f] c) determine which of the blocks of the plurality of the blocks in the MLC and SLC non-volatile memory modules are accessed most frequently by maintaining a count of the number of times each one of the blocks is accessed; and                                                                                                                                                          |

| 7.                      | [1g] d) allocate those blocks that receive the most frequent writes by transferring the respective contents of those blocks to the at least one SLC non-volatile memory module.                                                                                                                                                                                                                 |

|                         | CLAIM 2 IS OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE POSITA56                                                                                                                                                                                                                                                                                                                           |

|                         | [2Pre] The system of claim 1,                                                                                                                                                                                                                                                                                                                                                                   |

| 2.                      | [2] wherein the minimum quanta of address is equal to one block 57                                                                                                                                                                                                                                                                                                                              |

|                         | [2] wherein the minimum quanta of address is equal to one block                                                                                                                                                                                                                                                                                                                                 |

|                         | CLAIM 3 IS OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE POSITA                                                                                                                                                                                                                                                                                                                             |

| I                       | CLAIM 3 IS OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE                                                                                                                                                                                                                                                                                                                                    |

| 1.                      | CLAIM 3 IS OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE POSITA                                                                                                                                                                                                                                                                                                                             |

| 1.<br>2.<br><b>D. C</b> | CLAIM 3 IS OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE POSITA                                                                                                                                                                                                                                                                                                                             |

| 1.<br>2.<br><b>D. C</b> | CLAIM 3 IS OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE POSITA                                                                                                                                                                                                                                                                                                                             |

| E. CLAIM 5 IS OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE POSITA                     |

|--------------------------------------------------------------------------------------------|

| 1. [5Pre] The system of claim 1,                                                           |

| 2. [5] wherein the SLC non-volatile memory module is NAND flash memory                     |

| F. CLAIM 6 IS OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE POSITA                     |

| 1. [6Pre] The system of claim 1,                                                           |

| 2. [6] wherein the MLC non-volatile memory module is resistive random-access memory (RRAM) |

| G. CLAIM 7 IS OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE POSITA. 60                 |

| 1. [7Pre] The system of claim 1,                                                           |

| 2. [7] wherein the SLC non-volatile memory module is resistive random-access memory (RRAM) |

| H. CLAIM 8 IS OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE POSITA. 60                 |

| 1. [8Pre] The system of claim 1,                                                           |

| 2. [8] wherein the MLC non-volatile memory module is phase change memory (PCM)             |

| I. CLAIM 9 IS OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE POSITA. 61                 |

| 1. [9Pre] The system of claim 1,                                                           |

| 2. [9] wherein the SLC non-volatile memory module is phase change memory (PCM)             |

| J. CLAIM 10 IS OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF THE POSITA                    |

| 1. [10Pre] The system of claim 1,                                                                |

|--------------------------------------------------------------------------------------------------|

| 2. [10] wherein the SLC non-volatile memory module is magnetic random access memory (MAGRAM)     |

| K. CLAIM 11 IS OBVIOUS OVER SUTARDJA IN VIEW OF KNOWLEDGE OF TH<br>POSITA                        |

| 3. [11Pre] The system of claim 1,                                                                |

| 4. [11] wherein the controller causes the transfer of content on a periodic basis                |

| XII. THE PENDING LITIGATIONS IN THE WESTERN DISTRICT OF TEXAS DO NOT WARRANT DENYING INSTITUTION |

| XIII. CONCLUSION60                                                                               |

#### **TABLE OF AUTHORITIES**

# **CASES**

| Apple Inc. v. Fintiv, Inc.,                              |              |

|----------------------------------------------------------|--------------|

| IPR2020-00019 (P.T.A.B. Mar. 20, 2020)                   | 80           |

| KSR Int'l Co. v. Teleflex Inc.,                          |              |

| 550 U.S. 398 (2007)                                      | 25, 48, 62   |

| Phillips v. AWH Corp.,                                   |              |

| 415 F.3d 1303 (Fed. Cir. 2005)                           | 20, 21       |

| Vervain, LLC v. Kingston Technology Company, Inc. et al. |              |

| No. 1:24-cv-00254 (W.D. Tex. filed March 7, 2024)        | 2, 82        |

| Vervain, LLC v. Micron Technology, Inc. et al.,          |              |

| No. 6:21-cv-00487 (W.D. Tex. filed May 10, 2021)         | 2            |

| Vervain, LLC v. Phison Electronics Corp.,                |              |

| No. 1:24-cv-00259 (W.D. Tex. filed March 8, 2024)        | 2, 4, 80, 81 |

| Vervain, LLC v. Western Digital Corp. et al.             |              |

| No. 6:21-cv-00488 (W.D. Tex. filed May 10, 2021)         | 2            |

| <u>Statutes</u>                                          |              |

| 35 U.S.C. § 103                                          | 19, 83       |

| OTHER AUTHORITIES                                        |              |

| 37 C.F.R. § 42.6(e)                                      | 84, 85       |

| 37 C.F.R. § 42.8                                         | 4            |

| 37 C.F.R. § 42.8(b)(1)                                   | 4            |

| xii                                                      |              |

| 37 C.F.R. § 42.8(b)(2)   | 4  |

|--------------------------|----|

| 37 C.F.R. § 42.8(b)(3)   | 4  |

| 37 C.F.R. § 42.8(b)(4)   | 5  |

| 37 C.F.R. § 42.10(b)     | 4  |

| 37 C.F.R. § 42.15        | 5  |

| 37 C.F.R. § 42.24(a)(ii) | 85 |

| 37 C.F.R. § 42.102       | 6  |

| 37 C.F.R. § 42.104(a)    | 6  |

| 37 C.F.R. § 42.104(b)(1) | 16 |

| 37 C.F.R. § 42.200(b)    | 20 |

| 37 C.F.R. § 42.204(b)(3) | 20 |

| 37 C.F.R. § 42.204(b)(4) | 24 |

| 37 C.F.R. § 42.204(b)(5) | 24 |

## LIST OF EXHIBITS

| Exhibit | Description                                                                                                                                                                                 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1001    | U.S. Patent No. 8,891,298, titled "LIFETIME MIXED LEVEL NON-VOLATILE MEMORY SYSTEM," to Rao                                                                                                 |

| 1002    | Declaration of Carl Sechen, Ph.D.                                                                                                                                                           |

| 1003    | U.S. Provisional Application No. 61/509,257, titled "IMPROVED LIFETIME MIXED LEVEL NAND FLASH SYSTEM" by Rao                                                                                |

| 1004    | U.S. Patent No. 7,855,916, titled "NONVOLATILE MEMORY SYSTEMS WITH EMBEDDED FAST READ AND WRITE MEMORIES," to Rao                                                                           |

| 1005    | Intentionally omitted                                                                                                                                                                       |

| 1006    | Excerpts from prosecution history of '298 patent                                                                                                                                            |

| 1007-24 | Intentionally omitted                                                                                                                                                                       |

| 1025    | Excerpts from Rino Micheloni, et al., INSIDE NAND FLASH MEMORIES (Springer 2010)                                                                                                            |

| 1026    | Excerpts from Nonvolatile Memory Technologies with Emphasis on Flash: A Comprehensive Guide to Understanding and Using NVM Devices (Joe E. Brewer & Manzur Gill eds. Wiley-IEEE Press 2008) |

| 1027    | Excerpts from MICROSOFT COMPUTER DICTIONARY (5 <sup>th</sup> ed. 2002)                                                                                                                      |

| 1028-29 | Intentionally omitted                                                                                                                                                                       |

| 1030    | Yu Cai et al., Program Interference in MLC NAND Flash Memory:<br>Characterization, Modeling and Mitigation (IEEE 2013)                                                                      |

| 1031 | Kang-Deog Suh et al., A 3.3 V 32 Mb NAND Flash Memory with Incremental Step Pulse Programming Scheme, 30 IEEE J. Solid State Circuits 1149 (Nov. 1995)                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1032 | Eitan Yaakobi et al., Error Characterization and Coding Schemes for Flash Memories (2010 IEEE Globecom Workshops, Miami, FL at 1856-60)                                                                                                 |

| 1033 | Evans, Chris, "Enterprise MLC: How flash vendors are boosting MLC write endurance" (June 3, 2011)                                                                                                                                       |

| 1034 | Nelson Duann, SLC & MLC Hybrid (Silicon Motion Flash Memory Summit, Santa Clara, CA, Aug. 12, 2008)                                                                                                                                     |

| 1035 | Ashish Jagmohan et. al., <i>Adaptive Endurance Coding for NAND Flash</i> (2010 IEEE Globecom Workshops, Miami, FL at 1841-45)                                                                                                           |

| 1036 | Sungjin Lee et al., FlexFS: A Flexible Flash File System for MLC NAND Flash Memory (2009 USENIX Annual Technical Conference, San Diego, CA, June 14-19, 2009)                                                                           |

| 1037 | Minyoung Sung & Kanghee Kim, Asymmetric Flash Volume<br>Management, 58 IEEE Transactions on Consumer Electronics 455<br>(May 2012)                                                                                                      |

| 1038 | Greg Atwood et al., <i>Intel StrataFlash</i> ™ Memory Technology Overview at 4, Intel Technology J. (Q4 1997)                                                                                                                           |

| 1039 | Taehee Cho et al., "A 3.3 V 1 Gb multi-level NAND flash memory with non-uniform threshold voltage distribution," 2001 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, ISSCC (Cat. No. 01CH37177) (2001) |

| 1040 | U.S. Patent No. 6,456,528, titled for "SELECTIVE OPERATION OF A MULTI-STATE NON-VOLATILE MEMORY SYSTEM IN A BINARY MODE" to Chen                                                                                                        |

| 1041 | U.S. Patent No. 8,078,794, titled "HYBRID SSD USING A COMBINATION OF SLC AND MLC FLASH MEMORY ARRAYS," to Lee et al.                                          |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1042 | U.S. Patent Appl. Pub. No. 2008/0140918, titled "HYBRID NON-VOLATILE SOLD STATE MEMORY SYSTEM" by Sutardja                                                    |

| 1043 | U.S. Patent Appl. Pub. No. 2009/0327591, titled "SLC-MLC COMBINATION FLASH STORAGE DEVICE," by Moshayedi                                                      |

| 1044 | U.S. Patent Appl. Pub. No. 2010/0172179, titled "SPARE BLOCK MANAGEMENT OF NON-VOLATILE MEMORIES," by Gorobets et al.                                         |

| 1045 | U.S. Patent No. 8,634,240, titled "NON-VOLATILE MEMORY AND METHOD WITH ACCELERATED POST-WRITE READ TO MANAGE ERRORS," to Gavens et al.                        |

| 1046 | U.S. Patent No. 8,806,301, titled "DATA WRITING METHOD FOR A FLASH MEMORY, AND CONTROLLER AND STORAGE SYSTEM USING THE SAME," to Yu et al.                    |

| 1047 | U.S. Patent Appl. Pub. No. 2010/0115192, titled "WEAR LEVELING METHOD FOR NON-VOLATILE MEMORY DEVICE HAVNG SINGLE AND MULTI LEVEL MEMORY CELL BLOCKS," by Lee |

| 1048 | U.S. Patent Appl. Pub. No. 2011/0271043, titled "SYSTEM AND METHOD FOR ALLOCATING AND USING SPARE BLOCKS IN A FLASH MEMORY," to Segal et al.                  |

| 1049 | U.S. Patent Appl. Pub. No. 2011/0153912, titled "MAINTAINING UPDATES OF MULTI-LEVEL NON-VOLATILE MEMORY IN BINARY NON-VOLATILE MEMORY," by Gorobets et al.    |

| 1050 | U.S. Patent No. 5,930,167, titled "MULTI-STATE NON-VOLATILE FLASH MEMORY CAPABLE OF BEING ITS OWN TWO STATE WRITE CACHE," to Lee et al.                       |

| 1051    | U.S. Patent Appl. Pub. No. 2010/0172180, titled "NON-VOLATILE MEMORY AND METHOD WITH WRITE CACHE PARTITIONING," by Paley et al.                                                            |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1052    | Intentionally omitted                                                                                                                                                                      |

| 1053    | U.S. Patent Appl. Pub. No. 2009/0268513, titled "MEMORY DEVICE WITH DIFFERENT TYPES OF PHASE CHANGE MEMORY," by De Ambroggi et al.                                                         |

| 1054    | U.S. Patent Appl. Pub. No. 2009/0307418, titled "MULTI-CHANNEL HYBRID DENSITY MEMORY STORAGE DEVICE AND CONTROL METHOD THEREFOR," by Chen et al.                                           |

| 1055    | U.S. Patent Appl. Pub. No. 2010/0058018, "MEMORY SCHEDULER FOR MANAGING INTERNAL MEMORY OPERATIONS," by Kund et al.                                                                        |

| 1056-60 | Intentionally omitted                                                                                                                                                                      |

| 1061    | Duane H. Oto et al., <i>High-Voltage Regulation and Process Considerations for High-Density 5 V-Only E</i> <sup>2</sup> <i>PROM's</i> , SC-18 IEEE J. Solid State Circuits 532 (Oct. 1983) |

| 1062    | Gheorghe Samachisa et al., <i>A 128K Flash EEPROM Using Double-Polysilicon Technology</i> , SC-22 IEEE J. Solid State Circuits 676 (Oct. 1987)                                             |

| 1063    | Masaki Momodomi et al., <i>An Experimental 4-Mbit CMOS EEPROM with a NAND-Structured Cell</i> , 24 IEEE J. Solid State Circuits 1238 (Oct. 1989)                                           |

| 1064    | Tae-Sun Chung et al., <i>A survey of Flash Translation Layer</i> , 55 J. Systems Architecture 332-43 (2009)                                                                                |

| 1065    | Yoshiba Iwata et al., A High-Density NAND EEPROM with Block-<br>Page Programming for Microcomputer Applications, 25 IEEE J.<br>Solid-State Circuits 417 (Apr. 1990)                        |

|         | <del>-</del>                                                                                                                                                               |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1066    | Simona Boboila and Peter Desmoyers, Write Endurance in Flash Drives: Measurements and Analysis, Usenix Conference (Feb. 2010)                                              |

| 1067    | SiliconSystems, <i>Increasing Flash SSD Reliability</i> , StorageSearch.com (April 2005)                                                                                   |

| 1068    | Taehee Cho et al., <i>A Dual-Mode NAND Flash Memory: 1-Gb Multilevel and High-Performance 512-Mb Single Level Modes</i> , 36 IEEE J. Solid State Circuits 1700 (Nov. 2001) |

| 1069    | Ken Takeuchi, A Multipage Cell Architecture for High-Speed<br>Programming Multilevel NAND Flash Memories, 33 IEEE J. Solid-<br>State Circuits 1228 (Aug. 1998)             |

| 1070-79 | Intentionally omitted                                                                                                                                                      |

| 1080    | Docket list for <i>Vervain, LLC v. Phison Electronics Corp.</i> , No. 1:24-cv-00259 (W.D. Tex., filed March 8, 2024)                                                       |

| 1081    | Docket list for <i>Vervain, LLC v. Kingston Technology Company, Inc.</i> , No. 1:24-cv-00254 (W.D. Tex. filed March 7, 2024)                                               |

| 1082    | First Amended Complaint, Doc. No. 9 in <i>Vervain, LLC v. Phison Electronics Corp.</i> , No. 1:24-cv-00259 (W.D. Tex.)                                                     |

| 1083    | Signed Agreed Scheduling Order, Doc. No. 16 in <i>Vervain, LLC v. Phison Electronics Corp.</i> , No. 1:24-cv-00259 (W.D. Tex.)                                             |

#### I. INTRODUCTION:

Phison Electronics Corporation ("Phison" or "Petitioner") requests *inter* partes review ("IPR") of all claims 1-11 (the "Challenged Claims") of U.S. Patent No. 8,891,298, entitled "LIFETIME MIXED LEVEL NON-VOLATILE MEMORY SYSTEM," to Rao (the "298 patent") (Ex. 1001), which is assigned to Vervain, LLC ("Vervain" or "Patent Owner"). The '298 patent, which issued on Nov. 18, 2014, from U.S. Appl. No. 13/455,267 filed Apr. 25, 2012, incorporated by reference Dr. Rao's U.S. Patent No. 7,855,916,¹ and claimed priority from U.S. Provisional App. No. 61/509,257,² filed on July 19, 2011 ("Provisional," Ex. 1003).

The '298 patent and seven other patents, U.S. Patent Nos. 9,196,385 ("the '385 patent"), 9,997,240 ("the '240 patent"), 10,950,300 ("the '300 patent"), 11,830,546 ("the '546 patent"), 11,854,612 ("the '612 patent"), 11,967,369 and

<sup>1</sup> ('298 1:12-16, "Rao '916," Ex. 1004.) Rao '916, entitled "NONVOLATILE MEMORY SYSTEMS WITH EMBEDDED FAST READ AND WRITE MEMORIES," incorporated along with a then-pending application by Dr. Rao of the same title and specification ('298 1:16-21).

<sup>2</sup> ('298 1:7-12 [also incorporated by reference].) Note that the '298 application's title omitted "improved" from the Provisional title.

11,967,370, all with the same title and based on the same Apr. 25, 2012, specification and claiming July 19, 2011, priority, are currently asserted (First Amended Complaint, Ex. 1082) by Patent Owner against Petitioner in *Vervain, LLC v. Phison Electronics Corp.*, No. 1:24-cv-00259 (W.D. Tex. filed March 8, 2024).<sup>3</sup> Petitioner has petitioned for post-grant reviews of the '546 patent in pending *Phison*

\_

<sup>&</sup>lt;sup>3</sup> All are also asserted against a customer of Phison in *Vervain, LLC v. Kingston Technology Company, Inc., Kingston Digital, Inc., and Kingston Technology Corp.*, No. 1:24-cv-00254 (W.D. Tex. filed March 7, 2024). The first four patents were earlier asserted in *Vervain, LLC v. Micron Technology, Inc.*, No. 6:21-cv-00487 (W.D. Tex. filed May 10, 2021, settled April 21, 2023) and *Vervain, LLC v. Western Digital Corp.*, No. 6:21-cv-00488 (W.D. Tex. filed May 10, 2021, settled Aug. 8, 2023). Micron petitioned this Board for *inter partes* review in *Micron Technology, Inc. v. Vervain, LLC*, IPR2021-01547 ('298 patent), -01548 ('385 patent), -01549 ('240 patent), and -01550 ('300 patent), which were instituted on April 8 and 11, 2022, and terminated on April 4, 2023, on settlement after hearing but prior to final written decision.

Electronics Corp. v. Vervain, LLC, PGR2024-00047<sup>4</sup> and of the '612 patent in Phison Electronics Corp. v. Vervain, LLC, PGR2024-00048.<sup>5</sup>

This Petition demonstrates by a preponderance of the evidence that the Challenged Claims are unpatentable as claiming a long-known hybrid memory system of distinct Single-Level Cell ("SLC") and Multi-Level Cell ("MLC") NAND flash memory modules "adapted" to perform two optional functions of directing data preferentially to the SLC module under two circumstances: (1) failure of a "data integrity test" (7:26-13); and (2) "allocation" by "transfer" of the "contents" of "blocks" in the MLC and SLC modules "that receive the most frequent writes" (8:1-9). These functions were suggested in the specification as improving "lifetime (endurance)" but those functions in the detail recited had long been disclosed in the extensive NAND flash memory art which included many error management and wear leveling techniques for avoiding premature failure of hybrid systems. For Ground 1 of invalidity, Petitioner starts with a published hybrid memory system with multiple error management techniques and shows that a POSITA would apply known wear leveling techniques for the common objective of avoiding premature failure, thereby showing claim 1 obvious in view of the knowledge of the POSITA.

.

<sup>&</sup>lt;sup>4</sup> (Accorded filing date Aug. 27, 2024 [Paper No. 5].)

<sup>&</sup>lt;sup>5</sup> (Accorded filing date Sept. 25, 2024 [Paper No. 5].)

Conversely, for Grounds 2 and 3, Petitioner starts with two published hybrid memory systems with multiple wear leveling techniques and shows that a POSITA would apply known error management techniques for the common objective of avoiding premature failure, thereby showing claim 1 obvious in view of the knowledge of the POSITA. Under each Ground, the remaining Challenged Claims are also obvious over the asserted document in view of that document and other knowledge of the POSITA.

#### II. MANDATORY NOTICES UNDER 37 C.F.R. § 42.8:

## A. Real Party-In-Interest Under 37 C.F.R. § 42.8(b)(1)):

Petitioner Phison Electronics Corporation is the real party-in-interest.

#### B. Related Matters Under 37 C.F.R. § 42.8(b)(2):

As set forth further at note 3 supra, the '298 patent (along with seven other patents based on the same specification) is currently asserted by Vervain against Phison and its customer (separately) in the Western District of Texas. In the Phison case a claim construction hearing is tentatively scheduled for December 5, 2024, and jury selection is tentatively scheduled for December 15, 2025 (*Vervain, LLC v. Phison Electronics Corp.*, No. 1:24-cv-00259, Doc. No. 16 (W.D. Tex. July 15, 2024) (Ex. 1083). Resolution of this Petition may simplify that litigation and promote settlement.

# C. Lead and Back Up Counsel Under 37 C.F.R. § 42.8(b)(3):

Pursuant to 37 C.F.R. § 42.8(b)(3), lead counsel for this Petition is Hsuanyeh Chang, PhD (Reg. No. 73,431) and back-up counsel are Stephen Y. Chow (Reg. No. 31,338), Douglas E. Chin (Reg. No. 66,713), and Peter Yi (Reg. No. 61,790). Pursuant to 37 C.F.R. § 42.10(b), Petitioner has filed a power of attorney designating the above-identified counsel.

## D. Service Information Under 37 C.F.R. § 42.8(b)(4):

Service information under 37 C.F.R. § 42.8(b)(4) for the Petition is as follows:

| Lead Counsel                                                                                                                                       | Back-Up Counsel                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hsuanyeh Chang, PhD Reg. No. 73,431 HSUANYEH LAW GROUP PC 11 Beacon Street, Suite 900 Boston MA 02108 (617) 886-9088 (Phone) hsuanyeh@hsuanyeh.com | Stephen Y. Chow Reg. No. 31,338 HSUANYEH LAW GROUP PC 11 Beacon Street, Suite 900 Boston MA 02108 (617) 886-9288 (Phone) Stephen.Y.Chow@hsuanyeh.com |

|                                                                                                                                                    | Douglas E. Chin Reg. No. 66,713 HSUANYEH LAW GROUP PC 11 Beacon Street, Suite 900 Boston MA 02108 (617) 886-9488 (Phone) Doug.Chin@hsuanyeh.com      |

|                                                                                                                                                    | Peter Yi Reg. No. 61,790 HSUANYEH LAW GROUP PC 11 Beacon Street, Suite 900 Boston MA 02108 (617) 886-9188 (Phone) Peter. Yi@hsuanyeh.com             |

Petitioner consents to electronic service at the email addresses above.

#### III. ADDITIONAL REQUIREMENTS:

#### A. Payment of Fees Under 37 C.F.R. § 42.15:

The required fees are submitted from Deposit Account No. 50-6685 (Order No. 1280-0009). If any additional fees are due at any time during this proceeding, the Office is authorized to charge such fees to Deposit Account No. 50-6685 (Order No. 1280-0009).

#### B. Timing Under 37 C.F.R. § 42.102:

The present petition for *inter partes* review is filed more than nine months after the grant of the '298 patent.

### C. Grounds for Standing Under 37 C.F.R. § 42.104(a):

Petitioner certifies that: (1) the '298 patent is eligible for *inter partes* review; and (2) Petitioner is not barred or estopped from requesting *inter partes* review of any claims of the '298 patent on the grounds identified herein.

#### IV. NAND FLASH TECHNOLOGY BACKGROUND

Petitioner's expert, Dr. Carl Sechen, has provided in his declaration ("Sechen," Ex. 1002) a deep analysis of the state of NAND flash technology implicitly relied on by the '298 patent (Sechen Section V), the embodiments admitted or advanced in the '298 specification (Sechen Section VII), the evolution of the '298 claims through prosecution and their remaining defects (Sechen Section VIII), and invalidity of those claims over the prior art in view of the POSITA's

knowledge of the art (Sechen Sections IX through XII). Following is a summary of the NAND flash memory technology underlying the '298 patent base claim to a "system for storing data," based on known MLC and SLC NAND flash modules, and a known controller "adapted" to perform essential NAND flash mapping and optional, also known, error management and wear leveling

### A. Characteristic Nature of NAND Flash Memory

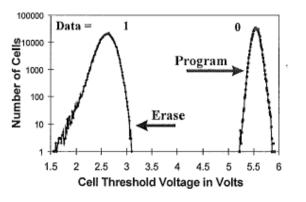

A **NAND flash cell** is type of transistor with an analog floating gate that can retain (store) a range of electrical charges associated with "threshold voltages" that, applied to a control gate, allows conduction of electrical current from drain to source. (Sechen ¶¶ 26 [Fig. 2.1(a)], 40 [Figures 6 and 7 from Atwood {Ex. 1038}] and 41.)

Data = 11 10 01 00 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100 1 100

Figure 6: Single bit/cell array threshold voltage histogram

Figure 7: Two bit/cell array threshold voltage histogram

These threshold voltages/charges may be chosen to represent information to be stored, in earlier NAND memory operation, using two threshold voltage levels (Figure 6), the lower level to represent ("store") a logical "1" and the higher level to store a logical "0" of one bit of (binary) digital computer data. (*Id.*) The same NAND

storage cell can use four threshold voltage levels (Figure 7) to represent four values corresponding to two bits of binary computer data (which in NAND memory operation is sourced from two distinct groups, "pages," of logical data). (*Id.*) An n power of two ( $2^n$ : eight, sixteen, . . .) threshold levels may be used in NAND flash operation to represent corresponding bits of n NAND flash pages (id. ¶¶ 40 and 42-43). But a storage cell or group of storage cells do not constitute "memory," which requires circuitry for selecting, programming (writing) and reading the cell or group of cells (id. ¶¶ 26 and 29).

To form NAND flash memory, NAND storage cells are hard wired in strings (bit-line "columns") and word-line "rows" forming NAND "pages" each typically 2K storage cells programmed page by page. (Id. ¶ 26.) A defining characteristic of NAND flash is that it is hard wired such that "blocks" of 64 pages are erased in unison in required preparation for writing to pages in that block that are not empty or previously erased (id. ¶¶ 28-30). Thus, unlike magnetic hard disk drives (and the '298 patents' proposed alternative technologies) which allow "write in place" of data assigned to a particular physical location, updates to data (considered "logical") in NAND flash must be written to a new physical location that is empty or must be erased in preparation ("erase before write"). (Id.) To maintain logical visibility to the user (host computer) of a NAND flash memory device such as a Solid State Drive ("SSD") (shown at Sechen ¶ 30), there are maintained and updated tables in or

available to a NAND flash device controller, shown as a hardware module or chip on an SSD circuit board (*id.*) to "map" logical locations visible to the user to physical locations in the NAND flash memory array ("L2P mapping"), which update for each data write (*id.* ¶¶ 30 and 31). The physical instances of NAND flash pages and blocks determine the Physical Block Addresses ("PBA") mapped from the construct of Logical Block Addresses ("LBA"). (*Id.* ¶¶ 32-34) This mapping and remapping is typically done with a software Flash Translation Layer ("FTL"). (*Id.*) The physical reading, writing and erasing of NAND flash cells is performed by circuity in a NAND flash memory module, shown in multiples in Sechen paragraphs 29 and 30 ("flash," "flash memory" or just "NAND") on a board, along with a block diagram identifying reading, writing and erasing functions (*id.* ¶ 29). A POSITA would understand this to be a NAND flash memory or module. (*Id.* ¶ 30.)

## B. Characteristic NAND Flash Memory Management

Sechen paragraphs 34-38 review well-known processes to manage the peculiarities of NAND flash memory. These include **bad block management** and **garbage collection**. Typically, "hot" data, *i.e.*, frequently updated (such as system) data, and "cold" (not-"hot") data are clustered in respective physical NAND flash blocks in order to facilitate efficient (fewer erase-and-re-writes) collecting of "valid" (un-updated) stored data and freeing up the blocks they otherwise occupy. In addition to avoiding unnecessary burdening of the NAND system operation with

long "erases," this and other "wear leveling" processes even out write and erase stresses on NAND memory blocks – which have limited expected "endurance" ("lifetime") – aiming to avoid premature failure or retirement of enough blocks that would compromise system use. (Sechen ¶ 39 [system lifetime].)

#### C. Introduction of MLC and SLC Flash

Multi-level cell (MLC) NAND flash, developed in 1992-97, as described in Atwood (Ex. 1038), was the use of the NAND storage cell with four threshold voltage levels to represent two bits of information. (Sechen ¶¶ 40-41.) The first known use of the term "SLC" was in a 2001 article that called the established technology "single-level program cell NAND flash (SLC)" and compared it with then new MLC. (Ex. 1039, Sechen ¶ 42.) Although the terms have been shortened over the years to their acronyms, a POSITA would understand that "MLC" refers to the use of NAND storage cells, each storing two bits written in two passes – a "lower" (least significant bit, "LSB") logical page and then a distinct "upper" (most significant bit, "MSB") logical page. (Id. ¶ 43.) That is, MLC flash memory allows writing two logical data pages into one physical page of memory. As reviewed at Sechen paragraph 43 (particularly Sechen note 17), the programming of MLC memory is more complex and stressful than for SLC because of MLC's narrower window for distinct threshold charges and its multiple passes of writing; also, a word-wide set of latches (word buffer) is required for reading each level of logical

word programming. Thus, a POSITA would understand that different circuitry is required for MLC NAND flash memory than for SLC NAND flash memory, and that SLC NAND flash memory is incapable of storing more than one logical data page in one physical page of memory.

Two-state/level operation of MLC (later called pseudo-SLC) was disclosed as early as 2002. (Sechen ¶ 49; U.S. Patent No. 6,456,528 to Chen for "Selective" Operation of a Multi-State Non-Volatile Memory System in a Binary Mode" ["Chen '528," Ex. 1040] [one-bit *mode* of writing only one logical data page into one MLC physical page of memory]). This mode of MLC use, applying the MLC memory circuitry and pulsed/phased writing, has inferior performance and endurance relative to "real" SLC. A SanDisk suite of patents (incorporating by reference among others, Chen '528) disclosed lower-density (pSLC) mode use of MLC modules through partitioning and configuration for multiple purposes, including faster processing for caching writes and error management (e.g., U.S. Patent No. 8,634,240 to Gavens et al., published Apr. 28, 2011 ["Gavens," Ex. 1045]; U.S. Patent No. 8,806,301 to Yu et al., published Apr. 14, 2011 [Ex. 1046], explained at Sechen ¶¶ 53-56).

D. Known Hybrid Use of SLC and MLC NAND Flash Modules with Strategies of Preferential Mapping, Wear Leveling and **Error Management**

Because of the compression of its threshold levels and its multiple passes of writing, MLC NAND flash, less costly per bit of information stored, was wellknown to wear more quickly (have less "endurance") but perform more slowly than SLC NAND flash. (Sechen ¶¶ 40-42.) Thus, it was proposed as early as 2008 to use hybrid systems of **SLC modules** and **MLC modules** in which more **frequently written**/updated (to logical locations) **data**, such as system data, user directories, and other user files accessed more frequently) would be written **preferentially to** a more robust **SLC module** while less frequently updated data such as user data would be written to the MLC module. (Sechen ¶ 46; Nelson Duann, SLC & MLC Hybrid (Silicon Motion Flash Memory Summit, Santa Clara, CA, Aug. 12, 2008) ["Duann," Ex. 1034]; U.S. Patent No. 8,078,794 to Lee et al., published Sept. 4, 2008 ["Lee '794," Ex. 1041].)

This **SLC module preference** was applied in 2008-09 to a variety of **wear leveling** techniques to avoid premature failure of a system by some components reaching their endurance limits before others. (Sechen ¶ 47-48 and 58-60; Sutardja, U.S. Patent Appl. Pub. No. 2008/0140918, "Hybrid Non-Volatile Sold State Memory System" ["Sutardja," Ex. 1042]; Moshayedi, U.S. Patent Appl. No. 2009/00327591, "SLC-MLC Combination Flash Storage Device" ["Moshayedi," Ex. 1043].)

Additional tools or techniques were known in the art before the priority date to avoid premature failure by applying **error management** near the end of life of the system with **preferential writing to SLC** upon determining failure of some

"data integrity test" at an MLC location. (Sechen ¶¶ 53-56 and 58-61, e.g., Gavens (Ex. 1046.)

The availability to the POSITA of these preferential writing to SLC techniques to avoid premature failure make obvious the base claim 1 of the '298 patent. (Sechen ¶ 62, Sections X(A), XI(A) and XII(A).)

#### **THE '298 PATENT: Specification** V.

The core disclosed system of known MLC NAND flash and SLC NAND flash modules is described as such, multiple times in the specification. (E.g., 4:51-56, 6:36-46; Sechen ¶ 69.) Fig. 4 shows a physical memory device module including two banks each including 8+ MLC flash memory modules and 2+ SLC NAND flash memory modules). A controller "coupled" to the MLC and SLC modules performs L2P/FTL functions essential for NAND flash operation and also performs common wear leveling. (3:65-4:4; Sechen  $\P$  70 and 72.) Only two "embodiments" are features that are optional for hybrid NAND flash memory systems.

The first, "data integrity test" feature is shown as the NAND flash method steps of Figs. 3a and 3b, largely, but not perfectly, explained in the text (5:55-6:23). Dr. Sechen identifies (¶ 71) ambiguities as to what is compared in the test as "stored data" and "retained data."

The second, feature is functionally explained in two sentences that describe what appears to be "wear leveling" by "allocat[ing] 'hot' blocks i.e., those blocks that receive frequent writes, into the SLC NAND flash memory module 28, while allocating 'cold' blocks; i.e., those blocks that only receive infrequent writes, into the MLC NAND flash memory module 26." (6:24-35 [emphasis added].) Dr. Sechen notes (¶ 73) various ambiguities, including its unclear reference to logical or physical blocks.

#### VI. The Challenged Claims of the '298 Patent (37 C.F.R. § 42.104(b)(1):

Claim 1 (7:6-8:9). In this "system for storing data" (7:8) the first two elements of physical MLC and SLC non-volatile memory ("NVM") modules (7:9-10 and 7:11-12) are "coupled" to a third element of a controller (7:13-15) defined by four functions that reflect with widely varying faithfulness DETAILED DESCRIPTION "embodiments." Controller function a) (7:16-25) corresponds to the FTL/L2P functions admitted in the BACKGROUND (2:30-3:13) and reviewed at Sechen paragraphs 70 and 72. Controller function b) (7:26-33) is recited as a severe abbreviation or abstraction of the DETAILED DESCRIPTION of the Figs. 3a and 3b data integrity test (5:55-6:23) reviewed at Sechen paragraph 71. Controller functions c) and d) are recited in a rearrangement of terms and concepts of the two-sentence DETAILED DESCRIPTION of apparent wear leveling (6:24-35) reviewed at Sechen paragraph 73. The Examiner found controller function d), "allocation" of "those blocks that receive the most frequent writes" by "transfer" to the SLC module, to be the sole point of invention. (Sechen ¶¶ 76-81, citing June 17,

2014, Office Action at 4 and 7-8 [Ex. 1006 at 42 and 45-46] [limitations through controller function b) anticipated by Gorobets '179, controller function c) obvious in view of Segal ]and Sept. 2, 2014, Notice of Allowability at 2 [Ex. 1006 at 80].)

**Dependent Claims:** Claims 2 and 3 limit the system of claim 1 to a minimum quanta of addresses to one block and one page respectively, without specifying logical or physical. Claims 4-10 limit the system of claim 1 to MLC and SLC NVM modules of NAND flash and alternative technologies. Claim 11 limits the system of claim 1 to transfer of content on a periodic basis.

In view of the literal claims and disclosure of the '298 patent, the accompanying prior art references and supporting declaration of Dr. Sachen (Ex. 1002), Petitioner respectfully requests cancellation of the Challenged Claims as summarized (pursuant to 37 C.F.R. § 42.104(b)(1), -(2), -(4) and -(5)) in the following table.

| Grounds                                                                                                                                                                 | Exhibits                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Ground 1: Claims 1-11 are unpatentable under U.S.C. § 103 as obvious over Gavens and incorporated disclosures in view of a POSITA's knowledge of NAND flash technology. | 1001, 1002, 1003, 1039, 1040, 1041,<br>1042, 1043, 1045, 1049, 1050, 1051,<br>1053, 1054, 1055 |

| Ground 2: Claims 1-11 are unpatentable under U.S.C. § 103 as obvious over Moshayedi in view of a POSITA's knowledge of NAND flash technology. | 1001, 1002, 1042, 1043, 1045, 1053,<br>1054, 1055 |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Ground 3: Claims 1-11 are unpatentable under U.S.C. § 103 as obvious over Sutardja in view of a POSITA's knowledge of NAND flash technology.  | 1001, 1002, 1042, 1043, 1045, 1053,<br>1054, 1055 |

# VII. Person of Ordinary Skill in the Art

A person of ordinary skill in the art at the time of the claimed inventions would have a bachelor's degree in computer engineering, electrical engineering, computer science, or a closely related field, along with at least two years of experience in the design, development, implementation, or management of memory devices and systems. A person with an advanced degree in a relevant field, such as computer or electrical engineering, would require less experience in the development and use of memory devices and systems. As is common, one could obtain equivalent knowledge and perspective from other life experiences as well. (Sechen ¶ 60-61.)

#### **VIII. 37 C.F.R. § 42.104(b)(3): CLAIM CONSTRUCTION**

Under 37 C.F.R. § 42.100(b), claims in an *inter partes* review proceeding are construed using the same claim construction standard that is used to construe claims in a civil action. This includes "construing the claim in accordance with the ordinary and customary meaning of such claim as understood by one of ordinary skill in the art and the prosecution history pertaining to the patent," id. The standard for claim construction is set forth in *Phillips v. AWH Corp.*, 415 F.3d 1303 (Fed. Cir. 2005).

The terms "MLC non-volatile memory modules" and "SLC non-volatile memory module" (7:9 and 7:11) have distinct, established, customary meanings for a POSITA (Section IV *supra* and Sechen Section V) where "memory" and "module" also have distinct meanings:

- "MLC memory modules" means "modules comprising MLC nonvolatile memory" where

- "MLC non-volatile memory" means "non-volatile memory cells arranged with circuitry capable of storing multiple logical pages in a single physical page of cells" and

- "SLC memory module" means "module comprising SLC non-volatile memory" where

- "SLC non-volatile memory" means "non-volatile memory cells arranged with circuitry incapable of storing multiple logical pages in a single physical page of cells"

Dr. Sechen explained (¶ 90) why a POSITA would only understand "SLC" and "MLC" to refer to distinct NAND flash memory circuity. Most tellingly, despite his knowledge of use of MLC in 2-state *mode*, corroborated by his Information Disclosure Statements submitted with the original application, <sup>6</sup> Dr. Rao chose to describe and claim his invention as a system with distinct, known MLC and SLC memory modules, "adapted" to two operational features – but not 2-state *mode* operation of only one MLC memory. In addition to explicit references to distinct modules (e.g., 4:51-56, 6:36-46, Fig. 4), Dr. Rao incorporated Rao '916 (Ex. 1004), his proposal to operate a known SLC memory module (Figs. 6a and 8 [100K p-e cycle endurance]) in a purportedly new way.

"Blocks": Petitioner maintains its position in the court litigation that the term is indefinite as to whether it refers to logical or physical blocks (Sechen ¶¶ 73 and 90) but will show here that the recited limitations are met under either construction.

<sup>&</sup>lt;sup>6</sup> (Ex. 1006 at 26-36, notably Taehee Cho et al., *A Dual-Mode NAND Flash Memory:* 1-Gb Multilevel and High-Performance 512-Mb Single Level Modes, 36 IEEE J. Solid State Circuits 1700, 1700 (Nov. 2001) [Ex. 1068] and Ken Takeuchi, *A Multipage Cell Architecture for High-Speed Programming Multilevel NAND Flash Memories*, 33 IEEE J. Solid-State Circuits 1228, 1230 Figs. 5-7 (Aug. 1998) [Ex. 1069])

"Controller": Petitioner maintains its position in the court litigation that the term is indefinite for, among other things, failing to provide necessary structure or algorithms, but will show that the recited functions are met by the art.

"Data Integrity Test": Petitioner maintains its position in the court litigation that this term (across multiple patents) means "a test that compares stored data to retained data." As noted by Dr. Sechen (¶ 87), the claim recitation of that test is defective. To the extent understandable, the art discloses the claimed use of the test.

\* \* \* \* \* \* \*

*Grounds for Review Under 37 C.F.R. § 42.104(b)(4)-(5)):*

# IX. <u>GROUND 1</u>: The Challenged Claims Are Obvious Over Gavens, Including Incorporated References, in View of Knowledge of the POSITA

The Challenged Claims are obvious under KSR Int'l Co. v. Teleflex Inc., 550 U.S. 398 (2007) because there is no gap between the hybrid SLC-MLC NAND flash system "adapted" to perform ordinary, necessary L2P/FTL functions and optional functions of directing data to the SLC module upon failure of a data integrity test or for wear leveling. Starting with a Gavens NAND flash system with multiple alternative error management operations including directing data to SLC, a POSITA would be motivated to use that system consistently with known wear leveling operations together meeting the Challenged Claim limitations directed to avoiding premature system failure.

### A. Claim 1 Is Obvious Over Gavens, Including Incorporated References, in View of Knowledge of the POSITA.

(Sechen ¶ 96): Gavens (Ex. 1045), among the SanDisk portfolio and incorporating by reference others of that portfolio,<sup>7</sup> is a published reference that discloses a complete multi-modal NAND flash system with the ordinary L2P/FTL function of its controller, a variety of post-write read error detection and management schemes, and the capability of and compatibility for employing other known tools (disclosed in incorporated documents and exemplified in [Sechen ¶¶ 58-61] used to avoid premature NAND system failure.

\_

<sup>&</sup>lt;sup>7</sup> See, e.g., U.S. Patent No. 6,456,528 to Chen ("Chen '528"), Ex. 1040, incorporated by reference at Gavens 16:29-40; U.S. Patent Appl. Pub. No. 2011/0153912 ("Gorobets '912"), Ex. 1049, incorporated by reference at Gavens 20:53-59; U.S. Patent No. 5,930,167 to Lee et al. ("Lee '167"), Ex. 1050, incorporated by reference at Gavens 17:57-67; U.S. Patent Appl. Pub. No. 2010/0172180, to Paley et al. ("Paley"), Ex. 1051, incorporated by reference at Gavens 8:41-42. Hereinafter, it should be understood that reference to a specific portion of any of the above reference, as if the incorporated document was explicitly contained in Gavens.

(Sechen ¶ 97): Since the 2001 (*e.g.*, Cho, Ex. 1039) emergence of MLC and recharacterization of previously established NAND flash as SLC, hybrid MLC memory modules and SLC memory modules have availed of the endurance advantages of SLC. (*E.g.*, Lee '794 [Ex. 1041], Sutardja [Ex. 1042], and Moshayedi [Ex. 1043]). Many implementations involve partitioning and configuration of some MLC blocks for one-level (two states) or pseudo-SLC (pSLC) operation. As reviewed at [Sechen ¶ 49] and in Gavens itself (*e.g.*, 12:6-10) the 2-state mode of operation enjoys superior endurance compared to MLC in normal mode – though not as superior as "real" SLC memory which uses different circuitry. It would be obvious to a POSITA to use a "real" SLC module for the purposes contemplated in Gavens. Gavens and its incorporated references, in view of the knowledge of the POSITA, disclose the limitations recited in claim 1:

# 1. [1a] at least one MLC non-volatile memory module comprising a plurality of individually erasable blocks;

(Sechen ¶ 101): Gavens' memory chip 100 "includes a memory array 200 of memory cells with each cell capable of being configured as a multi-level cell ("MLC") (8:19-21). The memory array may be organized in erasable blocks erased together in a "flash" operation (Fig. 6, 11:4-20). Thus, Gavens discloses in memory chip 100 (Fig. 1 (100), 8:13-21) discloses claim element [1a].

### 2. [1b] at least one SLC non-volatile memory module comprising a plurality of individually erasable blocks;

(Sechen ¶ 102): Gavens discloses, as a base system for multiple operational embodiments, "[a] first portion has each memory cell storing one bit of data and [a] second portion has each memory cell storing more than one bit of data" (4:32-34, 12:6-8 [memory operating in 1-bit mode "binary" or "SLC" memory]). It is explained that the first portion, being "configured as lower density storage[,] . . . operates with a wider margin of error than that of the second portion" (18:16-20, also 12:6-10, 21:6-9). As explained in [Sechen ¶ 96], it would be obvious to a POSITA to substitute a "real" SLC flash memory module for the Gavens first portion, with a similar, if not wider margin of error than binary mode operation of MLC (see [Sechen ¶ 49]) and achieve similar, if not better results with the same NAND flash controller Fig. 1(102) with great expectation of success. Gavens (4:32-34, 12:6-8), in view of the knowledge of the POSITA's knowledge of NAND flash, discloses the obvious use in the claimed system of claim element [1b].