1

INTEL\_GREENTHREAD00016467

# SILICON PROCESSING FOR THE VLSI ERA

**VOLUME 1:**

PROCESS TECHNOLOGY

**Second Edition**

STANLEY WOLF Ph.D.

RICHARD N. TAUBER Ph.D.

### LATTICE PRESS

Sunset Beach, California

#### DISCLAIMER

This publication is based on sources and information believed to be reliable, but the authors and Lattice Press disclaim any warranty or liability based on or relating to the contents of this publication.

Published by:

#### LATTICE PRESS

Post Office Box 340

Sunset Beach, California 90742, U.S.A.

Cover design by Roy Montibon, New Archetype Publishing, Los Angeles, CA.

Copyright @ 2000 by Lattice Press.

All rights reserved. No part of this book may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system without written permission from the publisher, except for the inclusion of brief quotations in a review.

Library of Congress Cataloging in Publication Data Wolf, Stanley and Tauber, Richard N.

Silicon Processing for the VLSI Era Volume 1: Process Technology

Includes Index

1. Integrated circuits-Very large scale integration. 2. Silicon. I. Title

ISBN 0-9616721-6-1

98765432

PRINTED IN THE UNITED STATES OF AMERICA

## **DETAILED TABLE OF CONTENTS**

| PREFACE<br>Prologue                                                                                                                                                                                                                                                       |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| I. SILICON: SINGLE-CRYSTAL GROWTH & WAFER PREPARATION                                                                                                                                                                                                                     |   |

| 1.1 TERMINOLOGY OF CRYSTAL STRUCTURE, 1 1.2 THE MANUFACTURE OF SINGLE-CRYSTAL SILICON, 5 1.2.1 From Raw Material to Electronic Grade Polysilicon 1.3 CZOCHRALSKI (CZ) CRYSTAL GROWTH, 8                                                                                   |   |

| <ul> <li>1.3.1 Czochralski Crystal Growth Sequence</li> <li>1.3.2 Incorporation of Impurities into the Crystal (Normal Freezing)</li> <li>1.3.3 Modifications Encountered to Normal Freezing in CZ Growth</li> <li>1.3.4 Czochralski Silicon Growing Equipment</li> </ul> |   |

| 1.3.4.1 Furnace 1.3.4.2 Crystal Pulling Mechanism 1.3.4.3 Ambient Control 1.3.4.4 Control System                                                                                                                                                                          |   |

| 1.3.5 Analysis of Czochralski Silicon in Ingot Form 1.3.5.1 Oxygen & Carbon Measurements in Si Using IR Absorbance Spectroscopy 1.4 FLOAT-ZONE SINGLE-CRYSTAL SILICON, 20                                                                                                 |   |

| 1.5 FROM INGOT TO FINISHED WAFER: SLICING; ETCHING; POLISHING, 22<br>1.6 SPECIFICATIONS OF SILICON WAFERS FOR ULSI, 25                                                                                                                                                    |   |

| 1.6.1 Electrical Specifications 1.6.2 Mechanical/Dimensional Specifications 1.6.3 Chemical/Structural Specifications                                                                                                                                                      |   |

| 1.6.4 Surface/Near Surface Specifications 1.7 THE ECONOMICS OF SILICON WAFERS, 29 1.8 TRENDS IN SILICON CRYSTAL GROWTH AND ULSI WAFERS, 31                                                                                                                                |   |

| REFERENCES, 32<br>Problems, 34<br>2. Crystalline defects and gettering                                                                                                                                                                                                    | 3 |

| 2.1 CRYSTALLINE DEFECTS IN SILICON, 36 2.1.1 Point Defects                                                                                                                                                                                                                | J |

| <ul><li>2.1.2 One-Dimensional Defects (Dislocations)</li><li>2.1.3 Area Defects (Stacking Faults)</li><li>2.1.4 Volume Defects</li></ul>                                                                                                                                  |   |

| 2.1.4.1 Classical Homogeneous 3-D Nucleation Theory 2.1.4.2 Nucleation of Volume Defects in Silicon Ingots                                                                                                                                                                |   |

35

- 2.2 INFLUENCE OF DEFECTS ON DEVICE PROPERTIES, 53

- 2.2.1 Leakage Currents in pn Junctions

- 2.2.2 Gate Oxide Quality

ix

CONTENTS 2.2.3 Wafer Resistance to Warpage 2.3 CHARACTERIZATION OF CRYSTAL DEFECTS, 55 2.4 OXYGEN IN SILICON, 57 2.5 GETTERING, 58 2.5.1 Basic Gettering Pinciples 2.5.2 Extrinsic Gettering 2.5.3 Intrinsic Gettering 2.5.4 Gettering with Oxygen Precipitates 2.5.5 Summary of Gettering REFERENCES, 67 PROBLEMS, 69 3. VACUUM TECHNOLOGY FOR ULSI APPLICATIONS 70 3.1 FUNDAMENTAL CONCEPTS OF GASES AND VACUUMS, 70 3.2 PRESSURE UNITS, 71 3.3 VACUUM PRESSURE RANGES, 72 3.3.1 Mean Free Path and Gas Flow Regimes 3.4 THE LANGUAGE OF GAS/SOLID INTERACTIONS, 73 3.5 TERMINOLOGY OF VACUUM PRODUCTION AND PUMPS, 75 3.5.1 Vacuum Pump Types 3.5.2 Pumping Speed and Conductance 3.5.3 Throughput 3.6 ROUGH PUMPS. 81 3.6.1 Oil-Sealed Rotary Mechanical Pumps 3.6.2 Vacuum Pump Oils for Semiconductor Processing 3.6.3 Roots Pumps 3.6.4 Dry Mechanical Pumps 3.7 HIGH VACUUM PUMPS I: CRYOGENIC PUMPS, 87 3.7.1 Cryopump Operation 3.7.2 Cryopump Regeneration 3.8 HIGH VACUUM PUMPS II: TURBOMOLECULAR PUMPS, 92 3.9 TOTAL PRESSURE MEASUREMENT, 95 3.9.1 Capacitance Manometers 3.9.2 Thermocouple Gauges 3.9.3 Pirani Gauges 3.9.4 Ionization (High Vacuum) Gauges 3.10 MEASUREMENTS OF PARTIAL PRESSURE: Residual Gas Analyzers, 98 3.10.1 Operation of Residual Gas Analyzers (RGA) 3.10.2 RGAs and Non-High Vacuum Applications: Differential Pumping 3.10.3 Interpretation of RGA Spectra 3.10.4 RGA Specification List REFERENCES, 102 PROBLEMS, 103

104

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>4.1 THIN FILM GROWTH, 105</li> <li>4.1.1 Thin Film Nucleation</li> <li>4.1.2 The Structure of Thin Films</li> <li>4.2 MECHANICAL PROPERTIES OF THIN FILMS, 108</li> <li>4.2.1 Adhesion</li> <li>4.2.2 Stress in Thin Films</li> <li>4.2.3 Other Mechanical Properties</li> <li>4.3 ELECTRICAL PROPERTIES OF METALLIC THIN FILMS, 113</li> <li>4.3.1 Measurement of the Electrical Properties of Thin Films</li> <li>4.3.2 Electrical Transport in Thin Films</li> </ul> |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | REFERENCES, 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PROBLEMS, 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5. CONTAMINATION CONTROL AND CLEANING TECHNOLOGY FOR ULSI                                                                                                                                                                                                                                                                                                                                                                                                                        | 119 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.1 TYPES OF CONTAMINATION IN IC FABRICATION, 119 5.2 SOURCES OF CONTAMINATION IN IC PROCESSING, 120 5.3 THE EFFECTS OF CONTAMINATION ON ULSI DEVICES, 121 5.4 CONTAMINATION PREVENTION MEASURES, 122 5.4.1. Cleanroom Design and Minienvironments                                                                                                                                                                                                                               |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul><li>5.4.2 Gowning Procedures</li><li>5.4.3 Ultrapure Chemicals</li><li>5.4.4 De-Ionized (DI) Water</li><li>5.4.5 Machine-Design and Wafer Handling Techniques</li></ul>                                                                                                                                                                                                                                                                                                      |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>5.4.6 Process Modifications</li> <li>5.5 WAFER CLEANING TECHNIQUES FOR ULSI, 128</li> <li>5.5.1 Wet-Chemical Removal of Film Contaminants</li> <li>5.5.1.1 FEOL Wet-Cleaning - RCA Clean</li> </ul>                                                                                                                                                                                                                                                                     |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.5.1.2 Modifications to the RCA Clean 5.5.1.3 Ozone-containing Water 5.5.1.4 Wet Cleaning of Metal-Coated Wafers (BEOL) 5.5.1.5 Spray Processing 5.5.2 Vapor-Phase and Dry Cleaning 5.5.2.1 Vapor-Phase Cleans 5.5.2.2 Ozone/UV Dry Cleans                                                                                                                                                                                                                                      |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>5.5.3 Photoresist Removal</li> <li>5.6 PARTICLE REMOVAL, 134</li> <li>5.6.1 Vibrational Scrubbing (Ultrasonic and Megasonic)</li> <li>5.6.2 Particle Removal by Brush Scrubbing</li> <li>5.6.3 Particle Removal by Liquid Jet spraying</li> </ul>                                                                                                                                                                                                                       |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul><li>5.6.4 Particle Removal by Cryosol Spray Techniques</li><li>5.6.5 Particle Removal by DUV-Laser Irradiation</li><li>5.7 RINSING AND DRYING WAFERS, 139</li><li>5.7.1 Rinsing</li></ul>                                                                                                                                                                                                                                                                                    |     |

| COSTA CONTRACTOR ACTIONS AND A |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

4. BASICS OF THIN FILMS

D

xii CONTENTS 5.7.2 Wafer Drying after Rinse 5.7.2.1 Spin-Dryers 5.7.2.2 Isopropyl-Alcohol (IPA) Vapor Dryers 5.7.2.3 Hot DI-Water Drying 5.7.2.4 Marangoni Drying 5.8 PARTICLE DETECTION ON WAFER SURFACES, 143 5.8.1 Automatic Laser Particle Counters for Detecting Particles on Wafers 5.8.2 Automatic Defect Classification (ADC) REFERENCES, 146 PROBLEMS, 148 6. CHEMICAL VAPOR DEPOSITION of AMORPHOUS & POLYCRYSTALLINE FILMS 149 6.1 BASIC ASPECTS OF CHEMICAL VAPOR DEPOSITION, 150 6.1.1 Grove's Simplified CVD-Film-Growth Model 6.1.2 Gas Flow and Gas-Phase Mass Transfer 6.1.2.1 Gas Flow in CVD Reactors 6.1.2.2 The Stagnant Layer Model 6.1.2.3 Boundary Layer Theory 6.2 CHEMICAL VAPOR DEPOSITION SYSTEMS, 162 6.2.1 Components of CVD Systems 6.2.1.1 Gas Sources and Delivery Systems for CVD 6.2.1.2 Mass-flow Controllers 6,2.1.3 Heating Sources for CVD Reaction Chambers 6.2.2 Terminology of CVD Reactor Design 6.2.3 Atmospheric Pressure CVD Reactors 6.2.4 Low Pressure Chemical Vapor Deposition Reactors 6.2.4.1 Horizontal-Tube LPCVD Batch Reactors (Hot Wall) 6.2.5 Plasma Enhanced CVD: Physics, Chemistry, & Reactor Designs 6.2.5.1 Parallel-Plate Cold-Wall Batch PECVD Reactors 6.2.5.2 Mini-Batch Radial Cold-Wall PECVD Reactors 6.2.5.3 Single-Wafer Cold-Wall PECVD Reactors 6.3 POLYCRYSTALLINE SILICON: PROPERTIES and CVD METHODS, 180 6.3.1 Properties of Polysilicon Thin Films 6.3.1.1 Physical Structure and Mechanical Properties of Poly-Si 6.3.1.2 Electrical Properties of Polysilicon 6.3.2 Chemical Vapor Deposition of Polysilicon 6.3.2.1 Deposition Parameters 6.3.2.2 Structure of Polysilicon - Deposition Condition Dependence 6.3.3 Doping Techniques for Polysilicon 6.3.3.1 Diffusion Doping of Polysilicon 6.3.3.2 Ion Implantation Doping of Polysilicon 6.3,3.3 In Situ Doping of Polysilicon 6.4 PROPERTIES and DEPOSITION OF CVD SiO2, 189 6.4.1 Chemical Reactions for CVD SiO<sub>2</sub> Formation 6.4.1.1 Low-Temperature Silane-Based CVD SiO2 6.4.1.2 Medium-Temperature LPCVD TEOS SiO2

225

CONTENTS 6.4.1.3 Low-Temperature PECVD TEOS 6.4.1.4 Ozone TEOS 6.4.2 Step Coverage of As-Deposited CVD SiO<sub>2</sub> Films 6.4.3 CVD & Applications of Undoped and Doped SiO<sub>2</sub> Films 6.4.3.1 Undoped CVD SiO2 6.4.3.2 Phosphosilicate Glass (PSG) 6.4.3.3 Borophosphosilicate Glass (BPSG) 6.5 PROPERTIES AND CHEMICAL VAPOR DEPOSITION OF SILICON NITRIDE, 202 6.6 OTHER DIELECTRIC FILMS DEPOSITED BY CVD, 206 6.6.1 Silicon Oxynitrides 6.7 CVD OF METALS, SILICIDES, AND NITRIDES FOR ULSI APPLICATIONS, 207 6.7.1 CVD of Tungsten (W) 6.7.1.1 CVD Tungsten Chemistry 6.7.1.2 Blanket CVD W and Etchback 6.7.2 Chemical Vapor Deposition of Tungsten Silicide (WSi<sub>x</sub>) 6.7.3 CVD of Titanium Nitride (TiN) 6.7.4 CVD of Aluminum REFERENCES, 220 PROBLEMS, 224 7 SILICON EPITAXIAL GROWTH and SILICON ON INSULATOR 7.1 THE DEVICE APPLICATIONS OF EPITAXY, 226 7.1.1. Why Do We Use CMOS Epitaxial Wafers? 7.2 GROWTH OF EPITAXIAL LAYERS, 228 7.2.1 Atomistic Model of Film Growth 7.3 CHEMICAL REACTIONS USED IN SILICON EPITAXY, 230 7.4 PROCESS CONSIDERATIONS FOR EPITAXIAL DEPOSITION, 233 7.4.1 Silicon Precursors 7.4.2 Doping of the Epitaxial Films 7.4.3 Intentional Doping 7.4.4 Unintentional Doping (Autodoping and Solid State Diffusion) 7.5 DEFECTS IN EPITAXIAL FILMS, 238 7.5.1 Wafer Preparation 7.5.2 Defects Induced During Epitaxial Deposition 7.5.3 Pattern Shift, Distortion, and Washout

S 149

7.6 LOW-TEMPERATURE EPITAXY PROCESSES, 243 7.7 SELECTIVE EPITAXIAL GROWTH (SEG), 245 7.8 EPITAXIAL DEPOSITION EQUIPMENT, 247

7.9 CHARACTERIZATION OF EPITAXIAL FILMS, 251

7.9.1 Optical Inspection of Epitaxial Film Surfaces

7.9.2 Electrical Characterization

7.9.3 Epitaxial Film Thickness Measurements

7.9.4 Infrared Reflectance Measurement Techniques

7.9.4.1 ASTM Technique of Epi Layer Thickness Measurement with IR Reflectance

xiv CONTENTS 7.9.5 Fourier-Transform Infrared (FTIR) Spectroscopy 7.10 SILICON-ON-INSULATORS (SOI), 256 7.10.1 Silicon-on-Sapphire (SOS) 7.10.2 SIMOX 7.10.3 Wafer Bonding REFERENCES, 261 PROBLEMS, 264 8. THERMAL OXIDATION OF SINGLE-CRYSTAL SILICON 265 8.1 THE PROPERTIES OF SILICA GLASSES, 267 8.2 OXIDATION KINETICS: THE DEAL-GROVE MODEL, 268 8.2.1 The Deal-Grove (or Linear-Parabolic) Model 8.3 FACTORS WHICH AFFECT THE ONE-DIMENSIONAL OXIDATION RATE, 276 8.3.1 Crystal Orientation Effects on Oxide Growth Rates 8.3.2 Dopant Effects on Oxidation Growth Rates 8.3.3 Water Effects During Dry Oxidation 8.3.4 The Dependence of Oxidation Rates on Chlorine 8.3.5 Effect of Pressure on Oxidation Rates 8.3.5.1 High Pressure Oxidation (HIPOX): 8.3.5.2 Low Pressure Oxidation 8.4 THE INITIAL OXIDATION STAGE AND THE GROWTH OF THIN OXIDES, 284 8.4.1 Experimental Results for Thin Oxide Growth 8.4.2 Growing Thin Oxides 8.5 THE NATURE OF THE Si-SiO2 INTERFACE, 288 8.5.1 Fixed Oxide Charge 8.5.2 Mobile Ionic Charge 8.5.3 Interface Trap Charge 8.5.4 Oxide Trapped Charge 8.6 STRESS IN SILICON DIOXIDE, 296 8.7 DOPANT IMPURITY REDISTRIBUTION DURING OXIDATION, 296 8.8 OXIDATION OF POLYSILICON, 298 8.9 THE OXIDATION OF SILICON NITRIDE, 299 8.10 THERMAL NITRIDATION OF SILICON AND SILICON DIOXIDE, 299 8.11 TWO-DIMENSIONAL OXIDE-GROWTH EFFECTS, 300 8.11.1 Birds Beak Encroachment 8.11.2 LOCOS Induced Gate Thinning 8.11.3 Trench Corner Rounding 8.11.4 Gate Birds Beak 8.12 OXIDATION SYSTEMS, 303 8.12.1 Thermal Budget 8.12.2 Thermal Processing Equipment (Tools) 8.12.3 Furnaces 8.12.4 Horizontal Furnaces 8.12.5 Vertical Furnaces 8.12.6 Anatomy of a Vertical Furnace 8.12.7 Fast-Ramp Furnaces

CONTENTS

8.12.8 Rapid Thermal Processing

8.12.9 RTP Systems

8.12.10 High Pressure Oxidation (HIPOX) Systems

8.13 THICKNESS MEASUREMENTS OF OXIDE FILMS, 314

8.13.1 Optical Measurements of Oxide Film Thickness

8.13.2 Electrical Measurement of Oxide Film Thickness

8.13.3 Physical Thickness Measurement of Oxide Films

8.14 TRENDS IN THIN OXIDE GROWTH, 317

8.14.1 Limitations of Silicon Dioxide

8.14.2 Reliability Limits for Thin Oxides

8.14.3 Fowler Nordheim (F-N) Tunneling

8.14 4 Alternative Gate Insulator Materials for MOSFETs

REFERENCES, 320

PROBLEMS, 322

5

#### 9. DIFFUSION in SILICON

324

9.1 THE MATHEMATICS OF DIFFUSION, 325

9.1.1 Fick's First Law

9.1.2 Fick's Second Law

9.1.3 Solutions to Fick's Second Law

9.1.3.1 Chemical Pre-Deposition

9.1.3.2 Drive-In Diffusion9.1.3.3 Drive-In From An Ion Implantation Predeposition

9.1.4 Concentration Dependence of the Diffusion Coefficient

9.2 DEFECTS AND DOPANT DIFFUSION, 322

9.2.1 Point Defects in Silicon

9.2.2 Temperature Dependence of the Diffusion Coefficient Under Intrinsic Conditions

9.2.3 Intrinsic Diffusion Coefficients

9.2.4 Fast Diffusers in Silicon

9.3 ATOMISTIC MODELS OF DIFFUSION, 336

9.4 DIFFUSION MODELLING, 339

9.4.1 SUPREM III:

9.4.2 SUPREM III Models for B, As, P, and Sb Diffusion

9.4.3 Modeling Intrinsic Diffusion

9.4.3.1 Boron

9.4.3.2 Arsenic

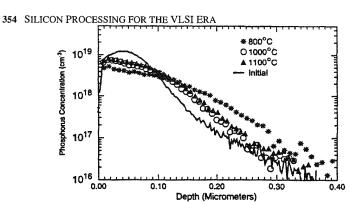

9.4.3.3 Phosphorus

9.4.3.4 Antimony

9.4.4 Modeling Extrinsic Diffusion

9.4.5 Modeling Diffusion with SUPREM IV

9.5 DIFFUSION IN POLYCRYSTALLINE SILICON, 346

9.6 DIFFUSION IN SILICON DIOXIDE, 347

9.6.1 Boron Penetration of Thin Gate Oxides

9.7 ANOMALOUS DIFFUSION EFFECTS, 348

9.7.1 Electric Field Enhancement

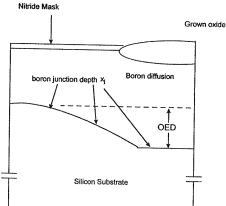

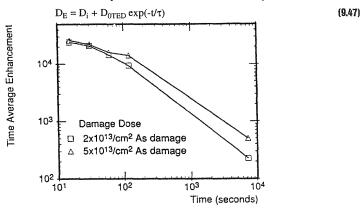

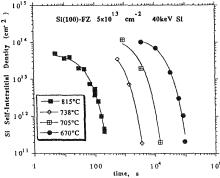

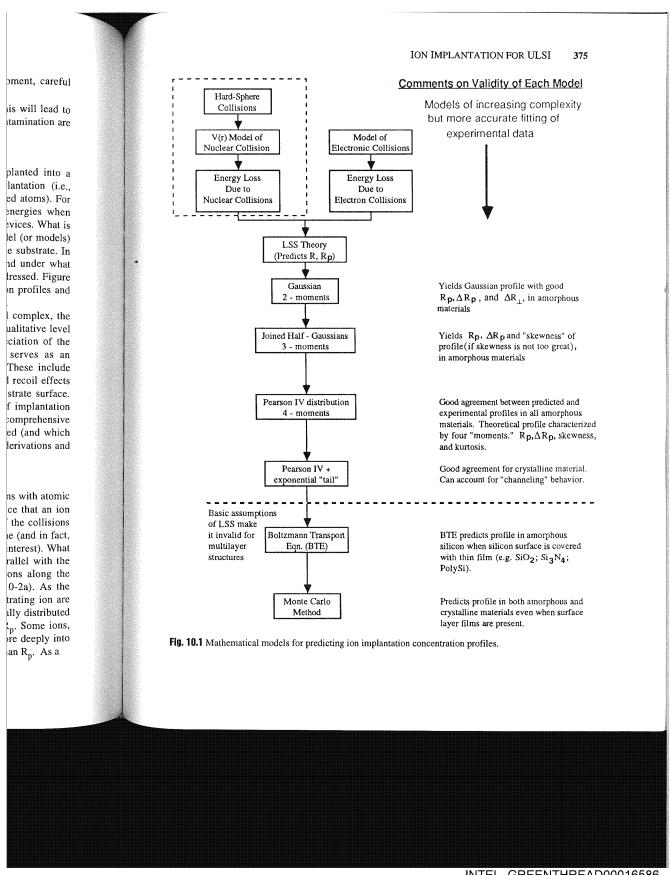

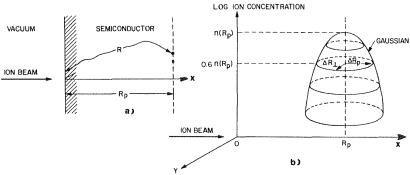

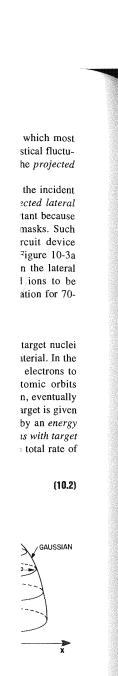

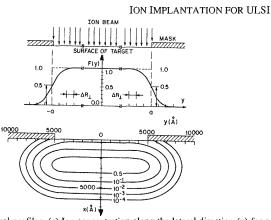

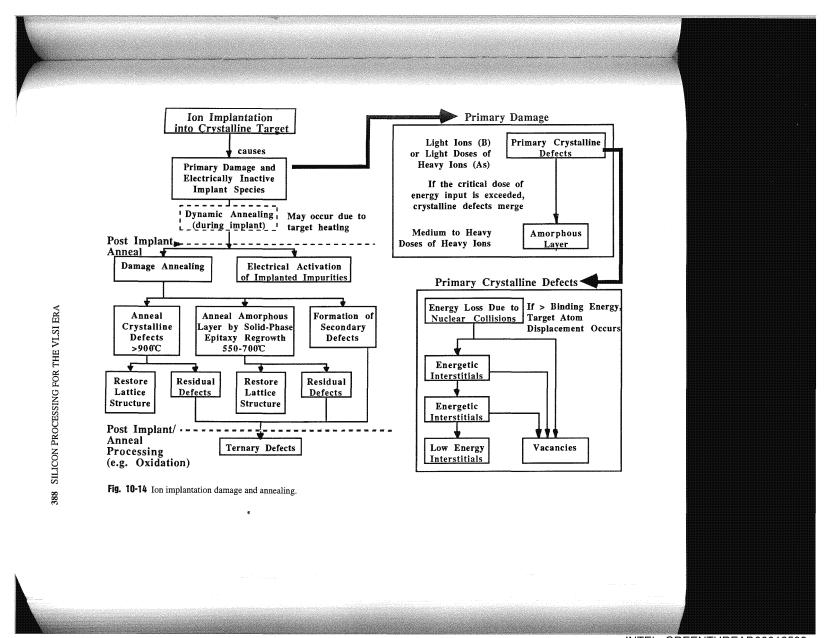

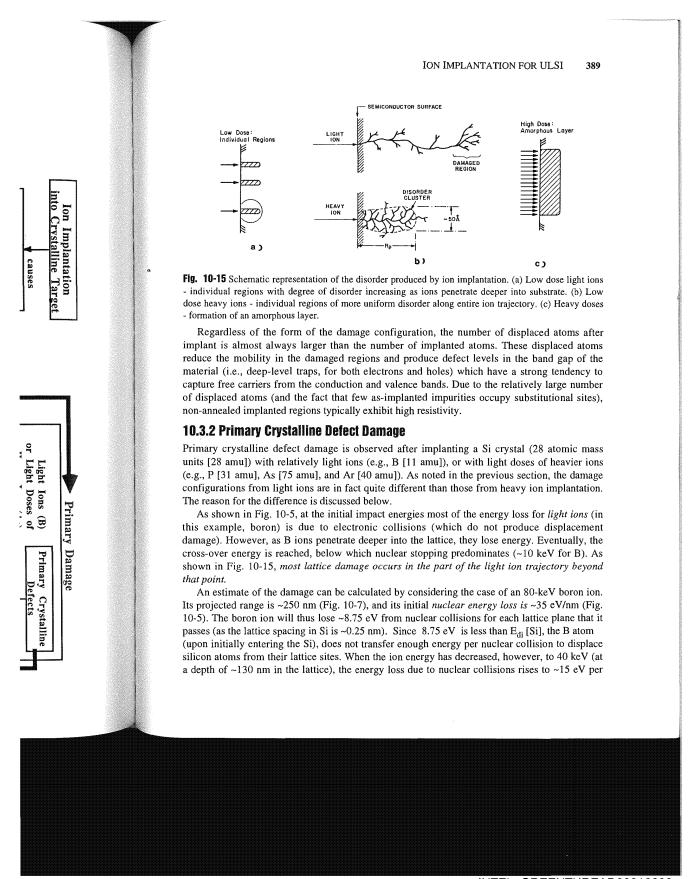

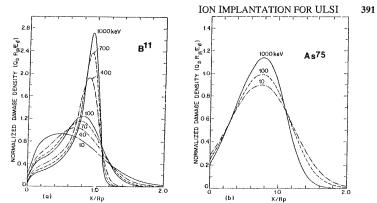

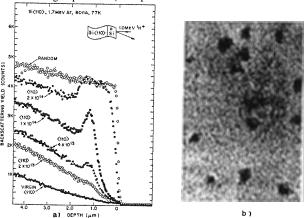

xvi CONTENTS 9.7.2 Emitter Push Effect 9.7.3 Lateral Diffusion Under Oxide Windows 9.7.4 Oxidation-Enhanced Diffusion (OED) 9.7.5 Transient Enhanced Diffusion (TED) 9.8 DIFFUSION SYSTEMS AND DIFFUSION SOURCES, 357 9.8.1 Advanced Diffusion Technologies 9.8.1.1 Rapid Vapor Doping (RVD) 9.8.1.2 Gas Immersion Laser Doping (GILD) 9.9 MEASUREMENT TECHNIQUES FOR DIFFUSED LAYERS, 359 9.9.1 Sheet Resistance Measurements 9.9.2 Capacitance-Voltage (C-V) Measurements 9.9.3 Spreading Resistance Profiling (SRP) 9.10 JUNCTION DEPTH MEASUREMENTS: PHYSICAL TECHNIQUES, 363 9.10.1 Angle Lap and Stain 9.10.2 Groove and Stain 9.10.3 Secondary Ion Mass Spectroscopy 9.10.4 Two-Dimensional Depth Profiling REFERENCES, 367 PROBLEMS, 370 10. ION IMPLANTATION for ULSI 371 10.1 ADVANTAGES (AND PROBLEMS) OF ION IMPLANTATION, 372 10.1.1 Advantages 10.1.2 Problems/Limitations of Ion Implantation 10.2 IMPURITY PROFILES OF IMPLANTED IONS, 374 10.2.1 Definitions Associated with Ion Implantation Profiles 10.2.2 Theory of Ion Stopping 10.2.3 Models for Implantation Profiles in Amorphous Solids 10.2.3.1 Higher Moment Distributions for Implant Profiles in Amorphous Material 10.2.4 Implanting Into Single Crystal Materials: Channeling 10.2.5 Calculating Implantation Profiles: Boltzmann Transport Equation and Monte Carlo Approaches 10.2.5.1 Monte Carlo Calculations 10.3 ION IMPLANTATION DAMAGE ACCUMULATION & ANNEALING IN SILICON, 386 10.3.1 Implantation Damage in Silicon 10.3.2 Primary Crystalline Defect Damage 10.3.3 Amorphous Layer Damage 10.3.4 Electrical Activation and Implantation Damage Annealing 10.3.4.1 Electrical Activation of Implanted Impurities 10.3.4.2 Annealing of Primary Crystalline Damage 10.3.4.3 Annealing of Amorphous Layers 10.3.4.4 Dynamic Annealing Effects

10.3.4.5 Diffusion of Implanted Impurities

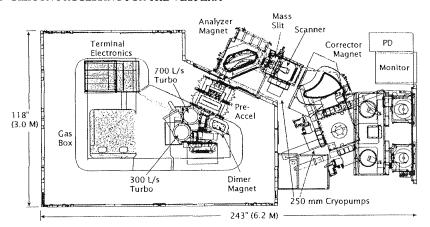

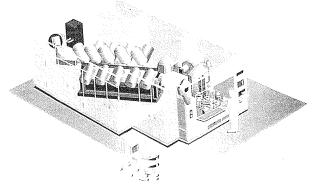

#### 10.4 ION IMPLANTATION EQUIPMENT, 396

10.4.1 Components of an Ion Implantation System

10.4.2 Ion Implanter Types

10.4.2.1 Medium-Current Implanters

10.4.2.2 High-Current Implanters

10.4.2.3 Low-Energy Implanters

10.4.2.4 High-Energy Implanters

10.4.2.5 High-Angle Implanters

10.4.3 Ion Implantation Equipment System Limitations

10.4.3.1 Elemental and Particulate

10.4.3.2 Dose Monitoring Inaccuracies due to Beam Charge-state

10.4.3.3 Implantation Mask Problems

10.4.3.4 Wafer Charging During Implantation

10.4.3.5 Machine-to-Machine Dose Matching

10.4.3.6 "Scan Lock-Up" and Scanned-beam Machines

10.4.3.7 Micro-Uniformity Dose Errors

10.4.4 Ion Implantation Safety Considerations

#### 10. 5 CHARACTERIZATION OF ION IMPLANTATION, 412

10.5.1 Measurement of Implantation Dose and Dose Uniformity

10.5.1.1 Implantation Dose Measurements

10.5.1.2 Implantation Dose Uniformity and Diagnosis of Implanter

10.5.2 Measurement of Implantation Depth Profiles

10.5.3 Measurement of Implantation Damage and Annealing Efficacy

#### 10.6 EXAMPLES OF ION IMPLANTATION PROCESS APPLICATIONS, 417

10.6.1 Selecting Masking Layer Materials and Thickness

10.6.2 Implanting Through Surface Layers

10.6.3 Threshold-Voltage Control in MOS Devices

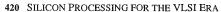

10.6.4. Shallow Junction Formation by Ion Implantation

10.6.5 High-Energy Implantation

10.6 6 Fabrication of SOI materials

10.6.7 New Techniques For Doping

10.6.7.1 Molecular Ions

10.6.7.2 Plasma Doping or Plasma Immersion Ion Implantation

10.6.7.3 Laser Doping

REFERENCES, 428

PROBLEMS, 432

#### 11. ALUMINUM THIN FILMS AND PHYSICAL VAPOR DEPOSITION IN ULSI 434

11.1 ALUMINUM THIN FILMS IN ULSI, 435

11.2 SPUTTER DEPOSITION FOR ULSI, 438

11.2.1 Introduction to Glow Discharge Physics

11.2.2 The Creation of Glow Discharges

11.2.3 Structure of Self-Sustaining Glow Discharges and Their Dark Spaces

1

386

xviii CONTENTS 11.2.4 Obstructed Glow Discharges & Dark-Space Shielding 11.3 THE PHYSICS OF SPUTTERING, 443 11.3.1 The Billiard Ball Model of Sputtering 11.3 2 Sputter Yield 11.3.3 Selection Criteria for Process Conditions and Sputter Gas 11.3.4 Secondary Electron Production for Sustaining the Discharge 11.3.5 Sputter Deposited Film Growth 11.3.6 Species that Strike the Wafer During Film Deposition 11.4 RADIO-FREQUENCY (RF) GLOW DISCHARGES, 450 11.5 MAGNETRON SPUTTERING, 456 11.5.1 Magnetron Sputter Sources for ULSI 11.5.1.1 Evolution of Planar Circular Sputtering Sources 11.5.1.2 Deposition Rate and Thickness Uniformity with Circular Planar Magnetrons: 11.6 VLSI AND ULSI SPUTTER DEPOSITION EQUIPMENT, 461 11.6.1 The Components of a Generic Sputtering System 11.6.1.1 Sputtering Targets 11.6.1.2 Vacuum Pumps for Sputtering Systems 11.6.1.3 Power Supplies for Sputtering Systems 11.6.1.4 The Gas Supply for Sputtering Systems 11.6.2 Commercial Sputtering Systems for 125-mm and 150-mm Wafers 11.6.3 Commercial Sputtering Systems for 200-mm Wafers 11.7 PROCESS CONSIDERATIONS IN SPUTTER DEPOSITION, 468 11.7.1 Sputter Deposition of Alloy Films 11.7.2 The Effects on the Sputter Process of the Transport of the Vaporized Atoms Between the Target and the Substrate 11.7.3 Wafer Heating During Sputter Deposition 11.7.4 Faceting and Trenching 11.7.5 Particle Generation in Sputtering Processes 11.7.6 Reactive Sputtering 11.8 STEP COVERAGE & VIA/CONTACT HOLE FILLING BY SPUTTERING, 475 11.8.1 Sputter Deposition of Barrier Layer Films into Contact Holes and Vias 11.8.1.1 Sputter Deposition with Collimators 11.8.1.2 Long-Throw Collimated sputtering 11.8.1.3 Ionized Magnetron Sputter Deposition 11.9 FUTURE TRENDS IN SPUTTER DEPOSITION PROCESSES, 483 11.10 METAL FILM THICKNESS MEASUREMENT. 483 REFERENCES. 485 PROBLEMS, 487 12. LITHOGRAPHY I: OPTICAL PHOTORESIST and PROCESS TECHNOLOGY 488 12.1 BASIC PHOTORESIST TERMINOLOGY, 488 12.2 PHOTORESIST MATERIAL PARAMETERS, 490 12.2.1 Resolution

- 12.2.1.1 Resolution Contrast

- 12.2.1.2 Resolution Swelling, Proximity Effects, and Resist Thickness

- 12.2.2 Sensitivity

- 12.2.3 Etch Resistance and Thermal Stability

- 12.2.4 Adhesion

- 12.2.5 Solids Content and Viscosity

- 12.2.6 Particulates and Metals Content

- 12.2.7 Flash Point and TLV Rating

- 12.2.8 Process Latitude and Consistency

- 12.2.9 Shelf-Life

- 12.3 OPTICAL PHOTORESIST MATERIAL TYPES, 500

- 12.3.1 Positive Optical Photoresists

- 12.3.2 Negative Optical Photoresists

- 12.3.3 Chemically-Amplified Deep-UV Resists

- 12.3.4 Multilayer Resist Processes

- 12.3.4.1 Si-CARL Process

- 12.3.5 Contrast Enhancement Layers

- 12.3.6 Silylation-Based Processes for Surface Imaging

- 12.3.6.1 DESIRE

- 12.3.6.2 PRIME

- 12.3.7 The Predicted Role of Multilayer and Surface Imaging Technologies

- 12.4 PHOTORESIST PROCESSING, 510

- 12.4.1 Resist Processing: Dehydration Baking and Priming

- 12.4.2 Resist Processing: Spin Coating

- 12.4.3 Resist Processing: Soft-Bake

- 12.4.4 Resist Processing: Exposure

- 12.4.4.1 Standing Waves

- 12.4.4.2 Linewidth Variation as Resist Crosses Steps

- 12.4.4.3 Swing Curves and CD Variation with Resist Thickness

- 12.4.2.4 Reflective Notching

- 12.4.2.4 Dyed Photoresists

- 12.4.2.6 Anti-Reflective Coatings (ARCs)

- 12.4.2.7 Bottom Anti-Reflective Coatings (BARCs)

- 12.4.2.8 Top Anti-Reflective Coatings (TARs)

- 12.4.5 Resist Processing: Post-Exposure Bake

- 12.4.6 Resist Processing: Development 12.4.7 Resist Processing: After-Develop Inspection

- 12.4.7.1 Linewidth Variation and Control

- 12.4.7.2 Linewidth Measurements

- 12.4.8 Resist Processing: Post-Development-Bake

- 12.4.9 Resist Processing: Photostabilization of Resists

- 12.5 PHOTORESIST PROCESSING SYSTEMS, 538

REFERENCES, 541

PROBLEMS, 544

188

CONTENTS 13. LITHOGRAPHY II: OPTICAL ALIGNERS and PHOTOMASKS 545 13.1 THE HISTORY (AND FUTURE) OF MICROLITHOGRAPHY, 546 13.2 BASICS OF OPTICAL SCIENCE FOR MICROLITHOGRAPHY, 548 13.2.1 Basic Terminology of Plane Waves of Light 13.2.2 Diffraction, Numerical Aperture, and Resolution 13.2.2.1 Resolution of the Optical System 13.2.2.2 Resolution - The Rayleigh Criterion 13.2.2.3 Resolution - The Optical Grating 13.2.2.4 Resolution - Fourier Optics Perspective 13.2.2.5 Coherence in Optical Systems 13.2.2.6 Resolution - Modulation Transfer Function 13.2.2.7 Resolution - Impact of the Depth of Focus: 13.2.2.8 A General Resolution Criterion - The Focus-Exposure Process Window: 13.2.3 Resolution Enhancement Techniques Involving the Stepper Optical System 13.2.3.1 Off-Axis Illumination: 13.2.3.2 Multiple Exposures Through Focus (FLEX) 13.3 PATTERN REGISTRATION, 582 13.3.1 Definition of Alignment and Overlay 13.3.2 Interfield and Intrafield Overlay Errors 13.3.3 Interfield Errors 13.3.4 Intrafield Errors 13.3.5 Overlay Metrology 13.4 OPTICAL LITHOGRAPHY EXPOSURE SYSTEMS, 588 13.4.1 Light Sources and Illumination Systems for Optical Lithography 13.4.1.1 Mercury Are Lamps 13,4,1.2 The Arc-Lamp Illumination System 13.4.1.3 Excimer Laser DUV light Sources 13.5 OPTICAL PROJECTION SYSTEMS, 595 13.5.1 1:1 Scanning Projection Aligners 13.5.2 Reduction Step-and-Repeat Projection Aligners (Reduction Steppers) 13.5.3 Non-Reduction Step-and-Repeat Projection Aligners (1X Steppers 13.5.4 Step-and-Scan Projection Systems 13.5.5 Stepper Wafer Handling System 13.5.6 Temperature, Vibration, and Environmental Control of Steppers 13.6 ALIGNMENT SYSTEMS IN STEPPERS, 605 13.6.1 Off-Axis Alignment Systems 13.6.2 Through-the-Lens Alignment Systems 13.6.3 Alignment Marks and Their Detection 13.6.4 Alignment Strategies 13.7 MECHANICAL ASPECTS OF STEPPER WAFER STAGES, 610 13.7.1 Wafer Stage Positioning and Wafer Chuck Design 13.7.2 Automatic Focussing Systems in Steppers 13.7.3 Automatic Leveling Systems

15

| 1 | 3  | R | M  | ſΔ  | SK       | AND  | RETICL | $\mathbf{F}$ | FAR | RI | $(C \Delta)$ | TION    | 615  |

|---|----|---|----|-----|----------|------|--------|--------------|-----|----|--------------|---------|------|

| 1 | э. | 0 | 10 | בעו | $\sigma$ | AIND | KEIICL | ъ            | FAE | 7  | L.A          | IIIVIN. | 01.7 |

13.8.1 Terminology and History of Photomasks

13.8.2 Fabrication of Photomasks and Reticles

13.8.2.1 Glass Quality and Preparation

13.8.2.2 Glass Coating (Chrome)

13.8.2.3 Mask Imaging (Resist Application and Processing)

13.8.2.4 Pattern Generation

13.8.3 Mask and Reticle Defects and Their Detection and Repair

13.8.3.1 Repairing Defects in Masks and Reticles

13.8.4 Pellicles

13.8.4.1 Inspecting Masks and Reticles with Pellicles Attached

13.8.5 Critical Dimension and Registration Inspection of Masks and Reticles

13.8.6 Storage, Transport, and Loading of Reticles into the Stepper

13.8.7 Optical Proximity Correction (OPC)

13.8.8 Phase Shift Masks (PSM)

13.9 MICROLITHOGRAPHY TRENDS, 635

13.9.1 The Limits of Optical Lithography

13.9.2 Non-Optical Microlithographic Technologies

13.9.2.1 Electron Beam Direct-Write Lithography

13.9.2.2 Electron Beam Projection Lithography (SCALPEL)

13.9.2.3 Extreme Ultra-Violet Reflective Projection Lithography (EUV)

13.9.2.4 Proximity X-Ray Lithography

13.9.2.5 Ion-Beam Projection Lithography

REFERENCES, 650

PROBLEMS, 654

#### 14. DRY ETCHING FOR VLSI

655

14.1 THE TERMINOLOGY OF ETCHING, 656

14.1.1 Bias, Tolerance, Etch Rate, and Anisotropy

14.1.2 Selectivity, Over-Etch, and Feature Size Control

14.1.3 Determining the Required Selectivity with Respect to Mask Materials,  $S_{\mbox{fm}}$

14.1.4 Determining Required Selectivity With Respect to Substrate,  $S_{fs}$

14.1.5 Combined Impact of the Requirements of Anisotropy and Selectivity

14.1.6 Loading Effects and Microloading

14.2 TYPES OF DRY-ETCHING PROCESSES, 666

14.3 BASIC PHYSICS AND CHEMISTRY OF PLASMA ETCHING, 667

14.3.1 The Reactive-Gas Glow Discharge

14.3.2 Electrical Aspects of Glow Discharges

14.3.3 Heterogeneous (Surface) Reaction Considerations

14.3.4 Parameter Control in Plasma Processes

14.4 ETCHING SILICON & SILICON DIOXIDE IN FLUOROCARBON PLASMAS, 673

14.4.1 The Fluorine-to-Carbon-Ratio Model

14.5 ANISOTROPIC ETCHING AND CONTROL OF EDGE PROFILE, 678

xxii CONTENTS 14.6 DRY-ETCHING VARIOUS TYPES OF MATERIALS IN ULSI APPLICATIONS, 681 14.6.1 Silicon Dioxide (SiO<sub>2</sub>) 14.6.1.1 Shaping the Sidewlls of Contact Holes and Vias by Dry-Etching 14.6,1.2 Etching 0.25 µm (and Smaller) Contact Holes and Aspect-Ratio Dependent Etching Effects (ARDE) 14.6.1,3 Via Veil Removal After Via Etching 14.6.2 Silicon Nitride 14.6.3 Polysilicon 14.6.4 Refractory Metal Silicides and Polycides 14.6.5 Aluminum and Aluminum Alloys 14.6.6 Organic Films 14.7 PROCESS MONITORING AND END POINT DETECTION, 696 14.7.1 Laser Interferometry and Laser Reflectance 14.7.2 Optical Emission Spectroscopy 14.8 DRY-ETCH EQUIPMENT CONFIGURATIONS, 698 14.8.1 Batch Commercial Dry-Etch System Configurations 14.8.1.1 Barrel Etchers 14.8.1.2 Parallel Electrode (Planar) Reactors 14.8.1.3 Cylindrical Batch Etch Reactors (Hexode Etchers) 14.8.2 Single-Wafer Etchers 14.8.2.1 Single-Wafer Parallel Plate Reactors 14.8.2.2 Magnetic-Enhanced Reactive Ion Etchers (MREIE) 14.8.2.3 Downstream Etchers 14.8.3 High-Density Plasma Sources 14.8.3.1 ECR Plasma Sources 14.8.3.2 Helicon Plasma Sources 14.8.3.3 Inductive (or Transformer) Coupled Plasma Sources 14.8.3.4 Helical-Resonator Plasma Sources 14.8.3.5 High Density Plasma Sources in ULSI Fabrication 14.8.3.6 Electrostatic Chucks 14.9 MISCELLANEOUS PROCESSING ISSUES RELATED TO DRY-ETCHING, 711 14.9.1 Plasma Etching Safety Considerations 14.9.2 Contamination Arising from Dry-Etch Processes 14.9.3 Damage Arising from Dry-Etch Processes 14.9,3.1 Oxide Damage During Polysilicon or Metal Etch Processes REFERENCES, 715 PROBLEMS, 718 15. MULTILEVEL INTERCONNECTS for ULSI 719 15.1 THE NEED FOR MULTILEVEL-INTERCONNECT TECHNOLOGY, 719 15.1.1 Interconnect Limitations of ULSI 15.1.1.1 Functional Density 15.1.1.2 Propagation Delay

31

15.1.2 Problems Associated with Multilevel-Interconnect Processes

15.1.3 Terminology of Multilevel-Interconnect Structures

15.2 MATERIALS FOR MULTILEVEL INTERCONNECT TECHNOLOGIES, 724

15.2.1 Conductor Materials for Multilevel Interconnects

15.2.1.1 Requirements of VLSI Conductor Materials

15.2.2 Dielectric Materials for Multilevel Interconnects

15.2.2.1 Requirements of Dielectric Layers in Multilevel Interconnects

15.3 PLANARIZATION OF INTERLEVEL DIELECTRIC LAYERS, 727

15.3.1 Terminology of Planarization in Multilevel Interconnects

15.3.1.1 Degree of Planarization

15.3.1.2 The Need for Dielectric Planarization

15.3.1.3 The Price of Increasing the Degree of Dielectric Planarization

15.3.1.4 Design Rules Related to Intermetal Dielectric-Formation and Planarization

15.3.2 Step-Height Reduction of Underlying Topography

15.3.2.1 Provide a Semi-Planar Surface over Local-Interconnect Levels

15.3.2.2 CVD SiO2 and Bias-Sputter Etchback

15.3.3 Planarization through Sacrificial-Layer Etchback

15.3.3.1 Sacrificial-Etchback Process Problems

15.4 DOUBLE-LEVEL-METAL (DLM) INTERCONNECTS FOR 1-μm CMOS, 739

15.5 CHEMICAL MECHANICAL POLISHING (CMP), 741

15.5.1 The History of CMP 15.5.2 Modeling the Mechanisms of CMP

15.5.2.1 Metal CMP Mechanisms

15.5.2.2 Silicon Dioxide CMP Mechanisms

15.5.2.3 CMP of Low-k Dielectrics

15.5.3 CMP Equipment

15.5.3.1 CMP Polishing Tools

15.5.3.2 CMP Consumables (Polishing Pads)

15.5.3.3 CMP Consumables (Slurries)

15.5.3.4 Slurry Distribution Systems

15.5.3.5 Endpoint Detection

15.5.3.6 Cleaning Issues in CMP

15.5.3.7 CMP Metrology

15.5.3.8 CMP Polisher Tool Reliability

15.5.3.9 CMP Systems and Process Integration

15.5.4 Miscellaneous Problems of CMP

15.5.4.1 Dishing

15.5.4.2 Thickness Non-Uniformity Within a Wafer After CMP

15.5.4.3 Economic Considerations: Throughput and Cost of Ownership

15.6 METAL DEPOSITION AND VIA FILLING, 770

15.6.1 Conventional Approach to Contact and Via Fabrication

15.6.2 Advanced Via Processing (Vertical Vias and Complete Filling of Vias by Metal)

15.6.3 Processing Techniques that Allow for Vertical Vias

15.6.3.1 CVD-W Plugs

15.6.3.2 Filling Vias with Al Deposited by Sputtering

15.6.3.3 Filling Vias by Electroplating of Cu

15.7 TRIPLE-LEVEL-METAL (TLM) INTERCONNECTS FOR 0.5-μm CMOS, 779

719

xxiv CONTENTS 15.8 COPPER FOR ULSI INTERCONNECTS, 779 15.8.1 Process Integration Issues of Cu 15.8.2 CVD of Copper (Cu) 15.8.3 Electroplating and Electroless-Plating of Copper 15.9 SPIN-ON GLASS (SOG), 785 15.9.1 SOG Process Integration: 15.9.2 The Etchback SOG Process 15.9.3 The Non-Etchback SOG Process 15.10 LOW-k DIELECTRICS, 791 15.10.1 Process Integration Issues of Low-k Dielectrics 15.10.2 First Generation Low-k Dielectrics (2.8 < k < 3.5)15.10.3 Second-Generation Low-k Dielectrics (2.5 < k < 2.8) 15.10.3.1  $2^{nd}$ -Gen Spin-On Dielectrics with 2.5 < k < 2.815.10.3.2  $2^{nd}$  Gen-CVD Dielectrics with 2.5 < k < 2.815.10.4 Ultra-Low-k Dielectrics (k < 2.0) 15.11 HIGH-DENSITY-PLASMA CVD (HDP-CVD) OF DIELECTRIC FILMS, 795 15.12 DAMASCENE AND DUAL-DAMASCENE INTERCONNECT STRUCTURES, 797 15.13 DAMASCENE INTERCONNECT STRUCTURE FOR 0.25 μm CMOS, 799 REFERENCES 801 PROBLEMS 806 16. CMOS PROCESS INTEGRATION 807 16.1 INTRODUCTION TO CMOS TECHNOLOGY, 807 16.1.1 Historical Evolution of CMOS 16.1.2 The Operation of CMOS Inverters 16.2 PROCESS SEQUENCES FOR CMOS:1.2 μm-0.5 μm GENERATIONS, 816 16.2.1 Starting Material 16.2.2 Formation of Wells and Channel Stops: 16.2.3 Definition of Active and Field Regions 16.2.4 Threshold-Adjust Implantation Step 16.2.5 Gate Oxide Growth 16.2.6 Polysilicon Deposition and Patterning 16.2.7 Formation of Source/Drain Regions 16.2.8 Pre-metal Oxide Deposition and Contact Formation 16.2.9 Metal Deposition and Patterning 16.2.10 Intermetal Dielectric Deposition and Via Patterning 16.2.11 Metal 2 Deposition and Patterning 16.2.12 Passivation Layer and Pad Mask 16.3 PROCESS FLOW FOR 0.25 μm CMOS, 828 16.3.1 Starting Material 16.3.2 Formation of the Shallow-Trench-Isolation Structure 16.3.3 Formation of Retrograde Wells and Carrying Out of V<sub>T</sub>-Adjust Implants 16.3.4 Formation of the Gate Oxide 16.3.5 Formation of the Gate-Stack Structures

7

807

C. ARRHENIUS RELATIONSHIPS, 877

INDEX

INTEL\_GREENTHREAD00016486

879

#### **PREFACE SECOND EDITION**

This second edition of Silicon Processing for the VLSI Era: Volume 1 - Process Technology follows the 1986 publication of the first edition. More than 20,000 volumes of that version were sold, attesting to its widespread acceptance throughout the microelectronics community. Professionals and students of this vibrant technology should find the new edition equally useful.

Many new processes and materials have been incorporated into IC fabrication in the fifteen years since the first edition was written. The new materials and processes covered in the second edition include: 300-mm wafers, DUV lithography, chemically-amplified resists, high-energy ion implantation, high-density plasma sources for CVD and etching, step-and-scan aligners, chemical-mechanical polishing, dual-damascene interconnects, copper metallization, and low-k dielectrics. Altogether the material of our book comprises more than 900 pages, 600 illustrations, and 1500 references (with over half of the citations from 1996 to 1999). It also includes those topics from the first edition that are still in use.

The effort of writing and producing this new edition was predominantly carried out by Stanley Wolf. He revised eight chapters (Chaps. 1, 2, 3, 4, 6, 11, 12, and 14), and entirely wrote the five new ones (Chaps. 5, 13, 15, 16, and 17). Three chapters were revised by Richard N. Tauber (Chaps. 7, 8, and 9), and Michael Current revised Chap. 10.

Valuable input to Stanley Wolf was also provided by many persons. Foremost of these were R. N. Tauber and C. A. Wolf. They each carefully read the entire manuscript and offered extensive editorial assistance (Tauber: primarily technical, and Wolf: grammatical). Others who provided important technical assistance and critical reviews were: Jerry Healey, Richard Cohen, Chris Mack, Bruce Smith, Robert Simonton, Dennis Hess, Moshe Preil, Wilbur Krussell, Bob Climo, Kathleen Perry, Peter Loewenhardt, and Donald Smith. Roy Montebin, of Vox Mundi, designed the book's cover.

Stanley Wolf, Ph.D.

Professor Emeritus, Department of Electrical Engineering, CSULB

I would also like to acknowledge the support of my former colleagues at Applied Materials for their helpful discussions and for kindly providing some of the figures used herein: Chris Fulmer, Gary Miner, Gary Xing, Kelly Truman, Majeed Foad, Norma Riley, Parvin Katebi, and Satheesh Kuppurao.

In addition, I would like to thank the following persons for providing additional background material and figures used in this textbook: Al Geise - SVG/Thermco; Clyve Hayzelden -KLA/Tencor; Gerhardt Kneissal - ADE; Jim Cable - Peregrine Semiconductor; Pat Shanks -Semitool; Sang-Shin Kim - GaSonics; and Terry Ma - Avant!/TMA.

Richard N. Tauber, Ph.D.

Consultant to the Microelectronics Industry

Clovis, California

xxvii

#### PREFACE TO THE FIRST EDITION

SILICON PROCESSING FOR THE VLSI ERA is a text designed to provide a comprehensive and up-to-date treatment of this important and rapidly changing field. The text consists of three volumes of which this book is the first, subtitled, Process Technology. Volume 2, subtitled, Process Integration was published in 1990. Volume 3, subtitled The Submicron MOSFET was published in 1995. In this first volume, the individual processes employed in the fabrication of silicon VLSI circuits are covered in depth (e.g., epitaxial growth, chemical vapor and physical vapor deposition of amorphous and polycrystalline films, thermal oxidation of silicon, diffusion, ion implantation, microlithography, and etching processes). In addition, chapters are also provided on technical subjects that are common to many of the individual processes, such as vacuum technology, the properties of thin films, and CMOS process integration. The topics covered in the book are listed in more detail in the Table of Contents.

The purpose of writing this text was to provide professionals involved in the microelectronics industry with a single source that offers a complete overview of the technology associated with the manufacture of silicon integrated circuits. Most other texts on the subject are available only in the form of specialized books (i.e., that treat just a small subset of all of the processes), or in the form of edited volumes (i.e., books in which a group of authors each contribute a small portion of the contents). Such edited volumes typically suffer from a lack of unity in the presented material from chapter-to-chapter, as well as an uneven writing style and level of presentation. In addition, in multi-disciplinary fields (such as microelectronic fabrication), it is difficult for most readers to follow technical arguments in such books, especially if the information is presented without defining each technical "buzzword" as it is first introduced. In our book, we hope to overcome such drawbacks by treating the subject of VLSI fabrication from a unified and more pedagogical viewpoint, and by being careful to define technical terms when they are first used. The result is intended to be a user friendly book for workers who have come to the semiconductor industry after having been trained in but one of the many traditional technical disciplines.

An important technical breakthrough has occurred in book publishing that the authors also felt could be exploited in creating a unique book on silicon processing. That is, revolutionary electronic publishing techniques became available in the mid-1980's, and these can cut the time required to produce a published book from a finished manuscript. The task traditionally took 15-18 months, but can be now reduced to less than 4 months. If traditional techniques are used to produce books in such fast-breaking fields as VLSI fabrication, these books automatically possess a built-in obsolescence, even upon being first published. The authors took advantage of these rapid production techniques, and were able to successfully meet the reduced productiontime schedule. As a result, it was possible to include information contained in technical journals and conferences within four months of the book's publication date. Most other books on silicon processing undergo such 15-18 month production cycles. This is the first book on the subject where such time-delay effects have been eliminated from the production process!

INTEL GREENTHREAD00016489

eral of the Electronics Systems Group and the Microelectronics Center of TRW are warmly thanked nore for providing a supportive environment, conducive to producing such an intensive technical ble. project. They made available technical literature and other resources to the authors, especially S. ers, Wolf, who was able to avail himself of this generosity while writing during a Sabbatical leave tion from his teaching duties at California State University, Long Beach. Roy Montibon and Donald able Strout of New Archetype Publishing, Inc., Los Angeles, CA designed the cover. Finally, we s of wish to thank Shirley Rome, Carrol Ann Wolf, and Barbara Tauber for typing the manuscript. id of cted Stanley Wolf and Richard N. Tauber y. In and o by P.S. Additional copies of the book can be obtained from: n the LATTICE PRESS ted P.O. Box 340 acher Sunset Beach, CA, 90742 f this

t,

and

from at the ıp-toi, Dr. ıpany erials. inner: 3, and 5 was

et and **nation** ts and rticles forms, of this /, and rs and √arren views. ailable upport rt and ment

An order form, for your convenience, is provided on the final leaf of the book.

INTEL\_GREENTHREAD00016490

#### **PROLOGUE**

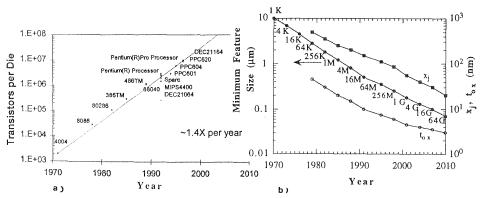

Since the invention of the first integrated circuit in 1960, there has been an ever-increasing density of devices manufacturable on semiconductor substrates. Silicon technology has remained the dominant force in integrated circuit fabrication and is likely to retain this position in the foreseeable future. The number of devices manufactured on a single chip exceeded the generally accepted definition of very large scale integration, or VLSI (i.e., more than 100,000 devices per chip) in the mid-1970's (Fig. 1a). By 1986 this number had grown to over 1 million devices per chip, and by 2000 had exceeded 1 billion devices per chip (e.g., the 1 GB DRAM). This increasing device count has been accompanied by a shrinking minimum feature size (Fig. 1b), which is expected to be smaller than 0.18  $\mu$ m by 2000. Progress in ULSI manufacturing technology seems likely to continue to proceed in this manner. Further reductions in the unit cost per function, and in the power-delay product of ULSI devices, are projected. The entire saga of IC fabrication represents a remarkable application of scientific knowledge to the requirements of technology. This book represents an enthusiastic report on the state-of-the-art of ULSI silicon processing, as practiced at the time of its publication.

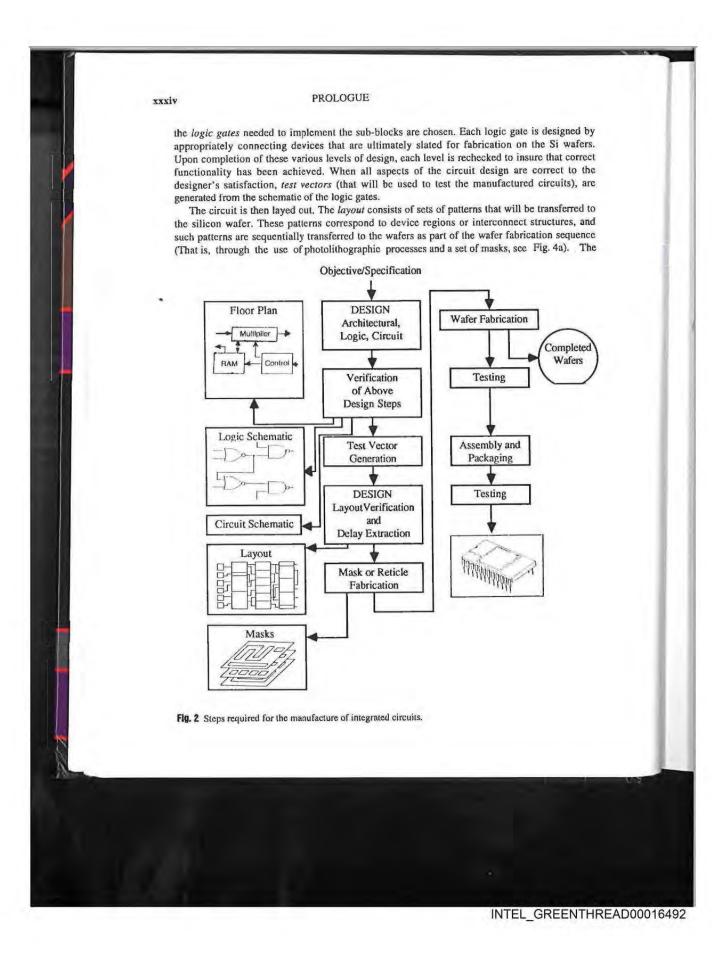

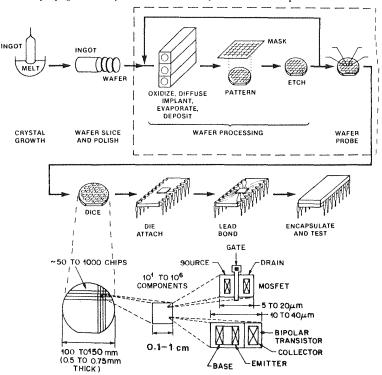

Figure 2 illustrates the sequence of steps that occurs in the course of manufacturing an integrated circuit. These steps can be grouped into two phases: 1) the *design phase*; and 2) the *fabrication phase* (Fig. 3). While this book is concerned only with the fabrication phase of this undertaking, it is also useful to briefly outline the steps of the design phase here. This provides the context which allows readers to perceive the role of silicon processing within the totality of integrated circuit manufacturing. Readers wishing to explore steps of the design phase in detail are referred to other technical literature, including the texts listed in References. 1, 2 and 3.

The desired functions and necessary operating specifications of the circuit are initially decided upon in the *design phase*. The chip is designed from the "top down." That is, the required large *functional blocks* are first identified. Next, their *sub-blocks* are defined, and finally

Fig. 1 (a) Increase in the number of transistors per microprocessor chip versus year of introduction, for a variety of microprocessor designs. 4 (© IEEE 1998) (b) Predictions of the decrease in minimum device feature size, junction depth, and gate oxide thickness versus time on integrated circuits, according to the SIA National Technology Roadmap for Semiconductors.

xxxii

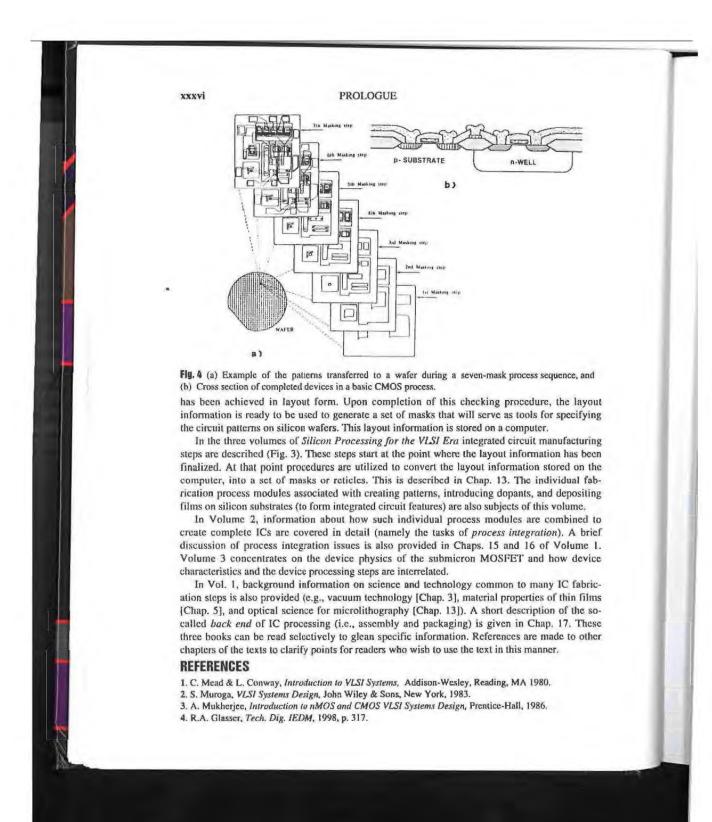

PROLOGUE xxxv

result of each pattern-transfer step is a set of features created on the wafer surface. These features are generally either in the form of: a) an etched opening in a film (or region of the substrate), or b) a patterned feature of a film present on the surface (e.g., an interconnect line or pad). After the openings (or *windows*) are created by the pattern transfer step, either controlled quantities of dopant are added to the silicon substrate through the openings, another layer is deposited that makes contact to the underlying layer through the opening. In either case, device regions and structures that interconnect device regions, are produced by the patterning processes and associated fabrication steps. A cross-section of a completed device is shown in Fig. 4b.

by

rs.

ect

the

are

1 to

and

nce

The

While the circuit is designed from the "top down," creation of the layout proceeds from the "bottom up." A variety of typical devices (e.g., transistors and resistors) are first layed out. Then, a set of cells representing the required primitive logic gates are created by interconnecting appropriate devices. Next, sub-blocks are generated by connecting these logic gates, and finally the functional blocks are layed out by connecting the sub-blocks. Additional items required by the circuit design are also incorporated during the layout process (e.g., power busses, clocklines, and input-output pads). The completed layout is then subjected to a set of design rule checks and propagation delay simulations to verify that correct implementation of the circuit

Fig. 3 The wafer fabrication process sequence of integrated circuits.

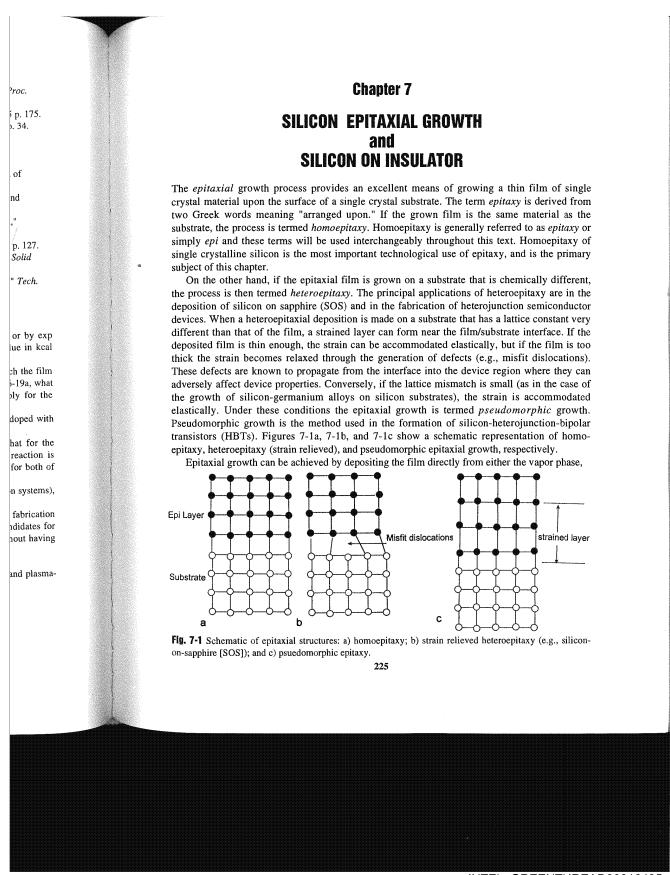

#### 226 SILICON PROCESSING FOR THE VLSI ERA

the liquid phase, or the solid phase. These techniques are termed *vapor-phase epitaxy* (VPE), *liquid-phase epitaxy* (LPE), and *solid-phase epitaxy* (SPE), respectively. VPE is the predominant method used in silicon processing, since it provides a means of achieving excellent control of the film thickness, impurity concentration, and crystalline perfection. A disadvantage of VPE is that it is requires relatively high temperatures (800–1150°C) in order to realize the necessary crystalline perfection. Such high-temperature processing can lead to the occurrence of *out-diffusion* and *autodoping*. These phenomena place a limitation on the ability to control the doping level in the epi layer and are discussed in detail in Section 7.4.4 of this chapter.

LPE has found its widest use producing epitaxial layers of III-V compounds (e.g., GaAs and InP). LPE, however, occurs during the re-freezing of molten layers of silicon on a silicon surface during the laser melting GILD process (see Chap. 9). SPE occurs during the crystalline re-growth that takes place during the low-temperature annealing of amorphous layers formed as a result of damage during high-dose ion implantation (see Chap. 10).

This chapter covers: 1) device applications of epitaxy; 2) fundamentals of epitaxial film growth; 3) epitaxial process considerations, including silicon precursors and doping effects; 4) defects in epitaxial layers; 5) pattern effects; 6) low-temperature epitaxy; 7) selective epitaxy; 8) epitaxial film characterization; and 9) silicon on insulators (SOI). The fundamentals of the kinetics and gas dynamics of CVD (epitaxial growth is a CVD process) are covered in detail in Chapter 6. In this chapter only the relevant results are repeated.

#### 7.1 THE DEVICE APPLICATIONS OF EPITAXY

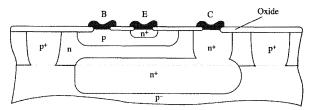

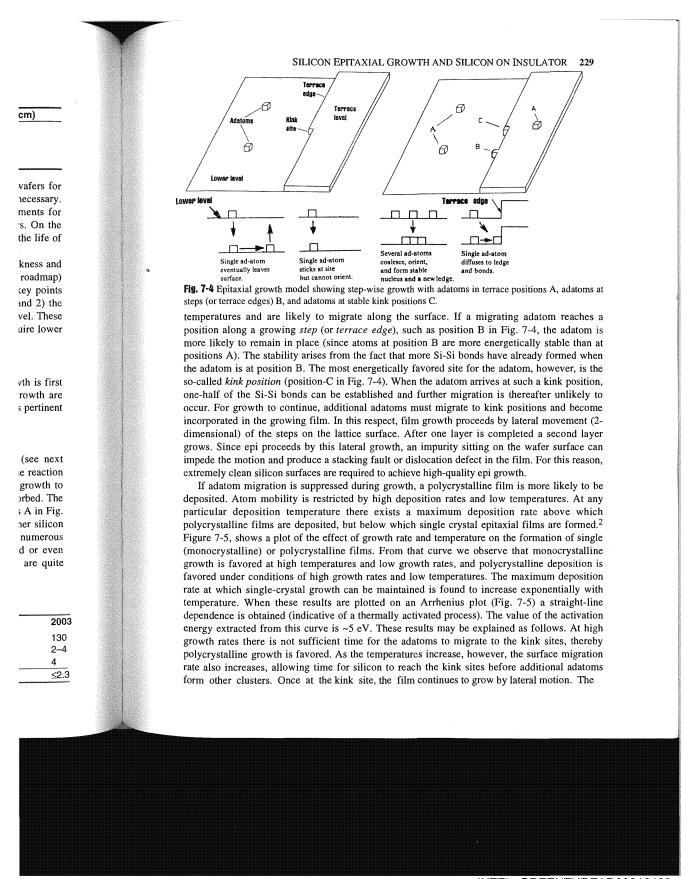

In the early days of semiconductor fabrication, epitaxial deposition was used to improve the performance of bipolar transistors that were then commonly used. By growing a lightly doped n-type epitaxial layer over a heavily doped n\* substrate the bipolar device could be optimized for high breakdown voltage of the collector-substrate junction, while preserving a low collector resistance. The low collector resistance was required to improve the device operating speeds at moderate currents. Figure 7-2 depicts a cross-section of a high-speed oxide-isolated bipolar transistor showing the presence of the epitaxial layer. A key feature of bipolar epitaxy is that the film is deposited over patterned, n\*-doped diffused layers called buried layers or sub-collectors. BiCMOS devices are also be fabricated in epitaxial films deposited over buried layers.

More recently, epitaxial processes have been used to fabricate CMOS integrated circuits. In CMOS circuits the complete device is built in a thin  $(2-4 \ \mu m)$ , lightly-doped p-type (or in some cases, intrinsic) epitaxial layer that is deposited over a uniformly heavily  $p^*$ -doped substrate. Figure 7-3 shows a cross section of a twin-well CMOS device depicting the epi layer.

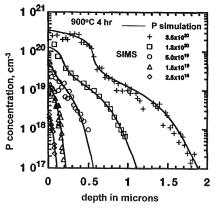

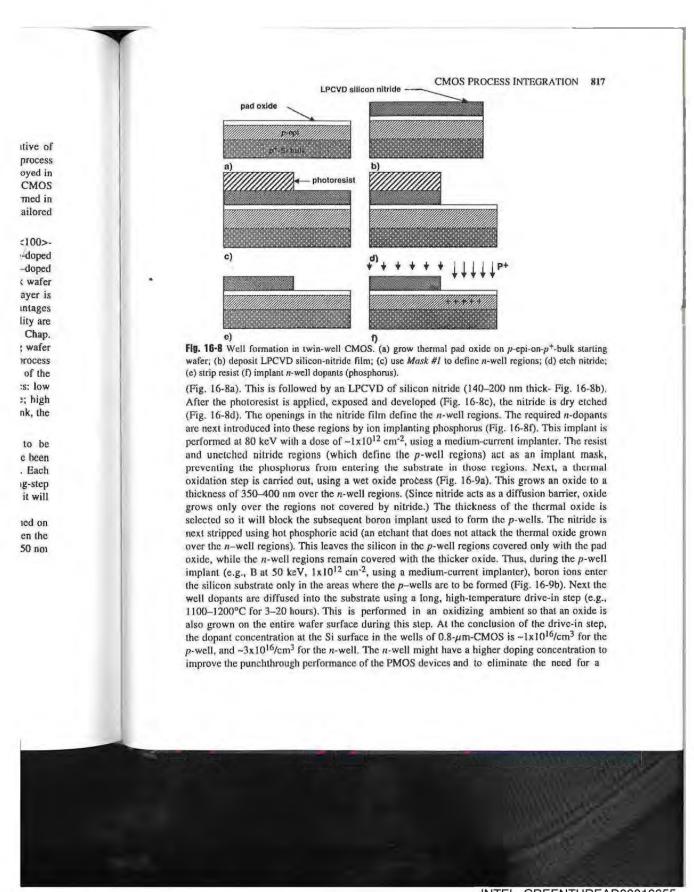

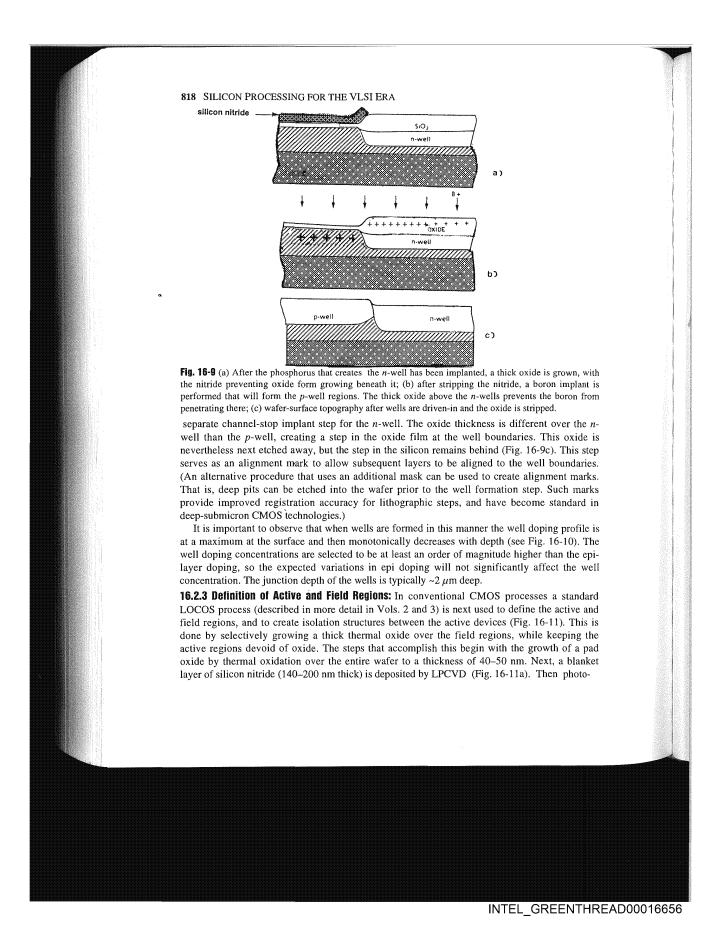

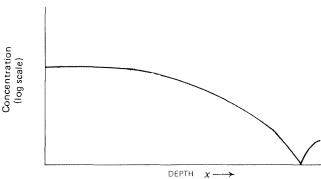

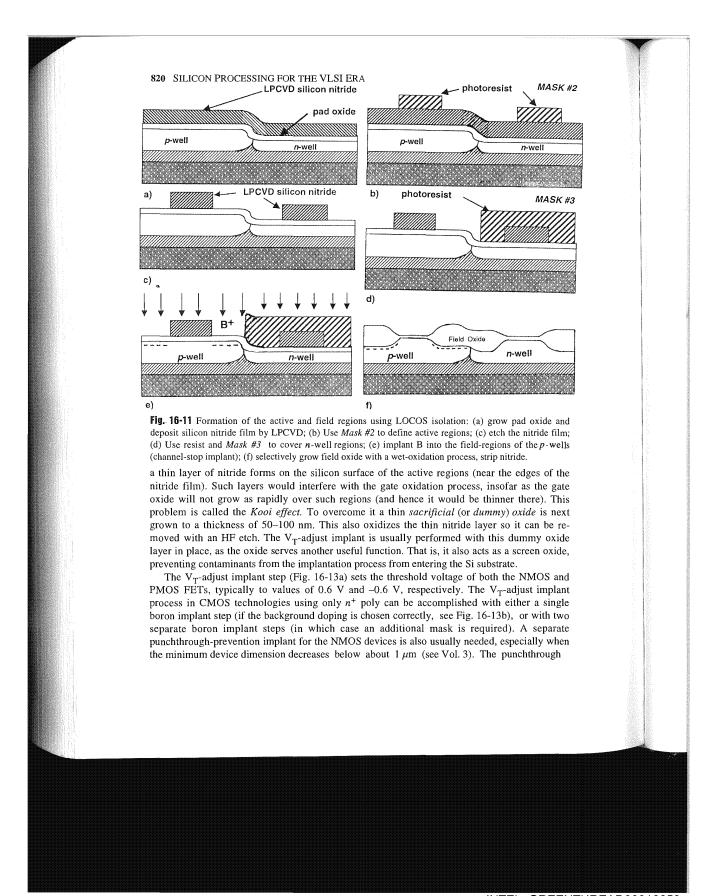

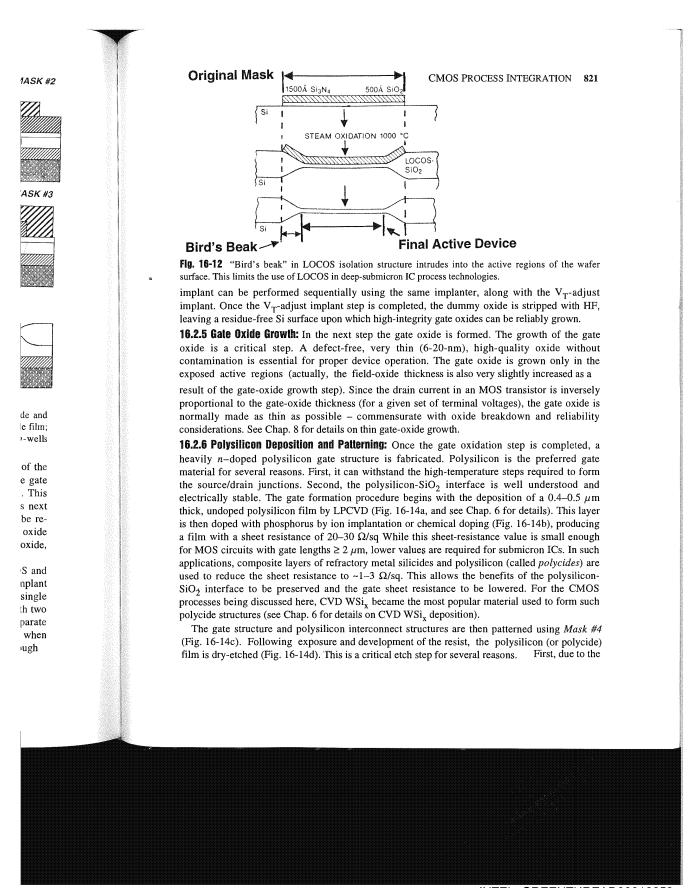

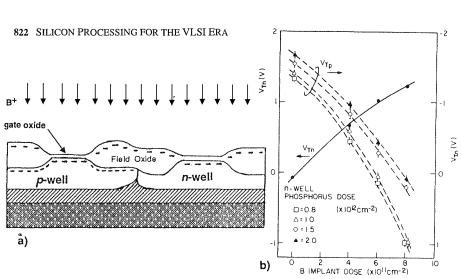

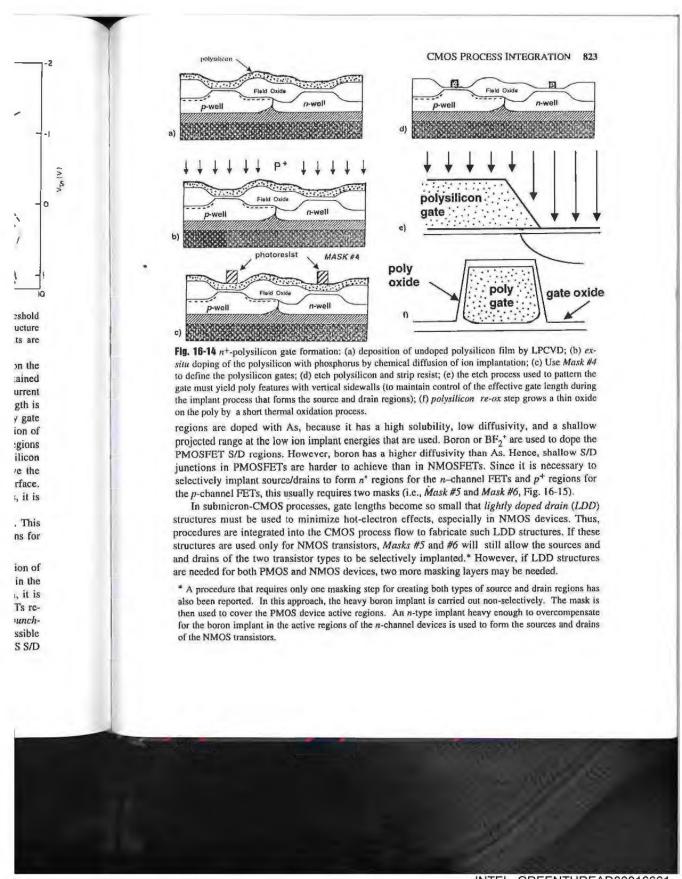

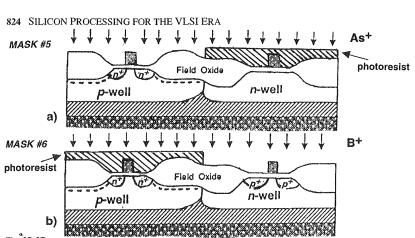

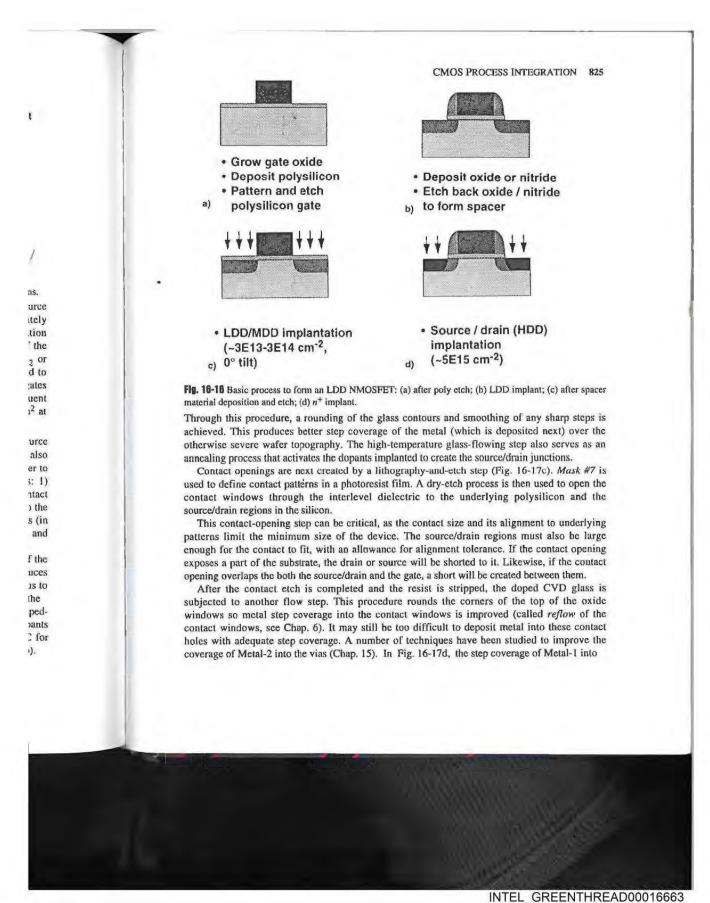

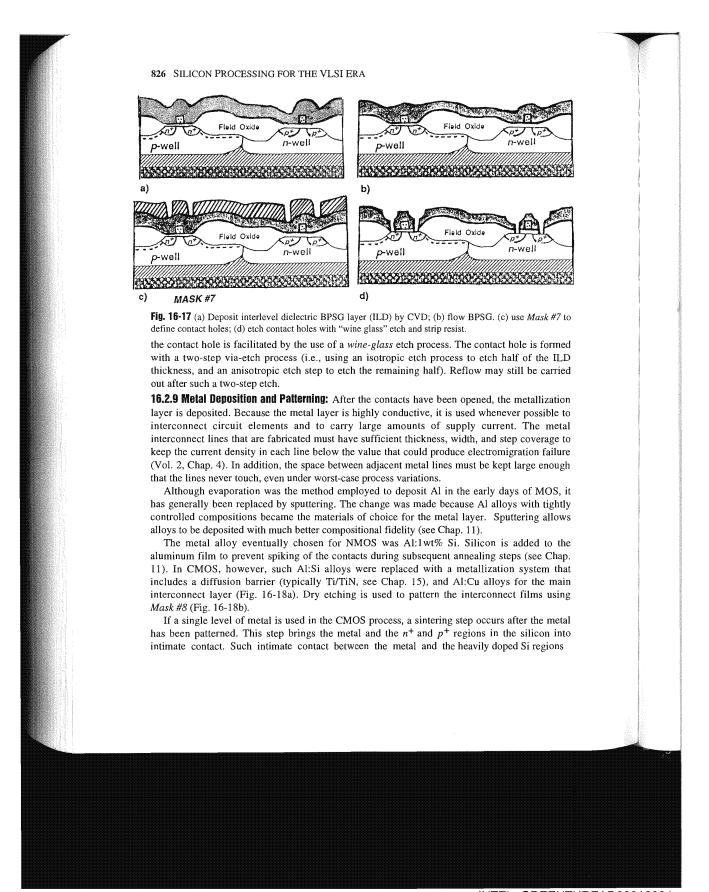

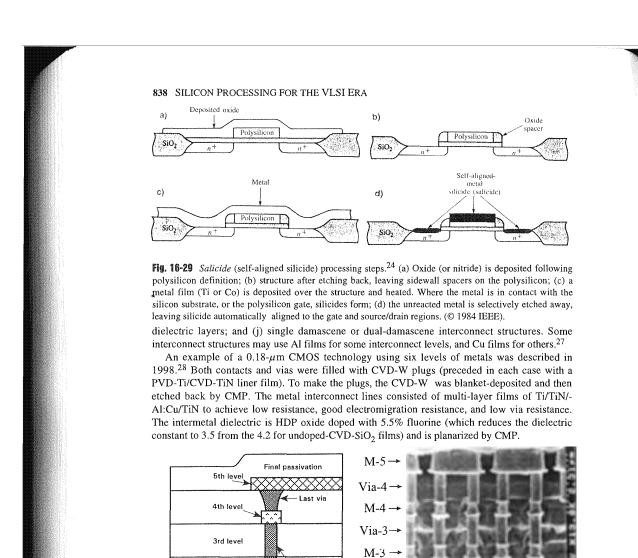

**Fig. 7-2** Cross-section of a bipolar transistor built in an epitaxial layer. The light line indicates the boundary of the deposited n-type epi layer. Note that the n<sup>+</sup>-buried layer extends into the epi layer as a result of autodoping and out-diffusion.