ONSEMI EXHIBIT 1008B, Page 2

# Silicon Processing

for the VLSI Era Volume 1 – Process Technology

By STANLEY WOLF and RICHARD N. TAUBER

"Arguably the best available text on the subject"

IEEE Transactions on Education

"The authors of this volume, have succeeded admirably. The book is a uniquely valuable reference for the professional microelectronic engineer....Volume 2 of this text will be eagerly awaited." Semiconductor Science and Technology

"Well organized, and presented in a logical and clear fashion. Lucid writing style, with abundant and well-placed illustrations...Overall, an excellent book on silicon processing...I highly recommend it! IEEE Circuits and Devices Magazine

TABLE of CONTENTS - Ch. 1 Silicon: Single-Crystal Growth and Wafering; Ch. 2 Crystalline Defects, Thermal Processing; and Gettering; Ch. 3 Vacuum Technology for VLSI Applications; Ch. 4 Basics of Thin Films; Ch. 5 Silicon Epitaxial Film Growth; Ch. 6 Chemical Vapor Deposition of Amorphous and Polycrystalline Films; Ch. 7 Thermal Oxidation of Single-Crystal Silicon; Ch. 8 Diffusion in Silicon; Ch. 9 Ion Implantation for VLSI; Ch. 10 Aluminum Thin Films and Physical Vapor Deposition in VLSI; Ch. 11 Refractory Metals and Their Silicides in VLSI; Ch.12 Lithography I: Optical Photoresists-Material Properties and Process Technology; Ch. 13 Lithography II: Optical Aligners and Photomasks; Ch. 14 Advanced Lithography: E-Beam and X-Ray; Ch. 15 Wet Processing: Cleaning, Etching and Lift-Off; Ch. 16 Dry Etching for VLSI; Ch. 17 Material Characterization Techniques for VLSI Fabrication; Ch. 18 Structured Approach to Design of Experiments for Process Optimization.

1986 LATTICE PRESS 660 pp. ISBN 0-9616721-3-7

Order using form on last page of this book

### CONTENTS

### PREFACE

| VLSI AND ULSI                                                                                                                                                                                                                                                                                                                       | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 PROCESS INTEGRATION 5                                                                                                                                                                                                                                                                                                           |    |

| <ul> <li>1.1.1 Process Sequence Used to Fabricate an Integrated-Circuit MOS Capacitor, 5</li> <li>1.1.2 Specifying a Process Sequence, 6</li> <li>1.1.3 Levels of Process Integration Tasks, 7</li> </ul>                                                                                                                           |    |

| 1.2 PROCESS-DEVELOPMENT AND PROCESS-INTEGRATION ISSUES 8                                                                                                                                                                                                                                                                            |    |

| REFERENCES 11                                                                                                                                                                                                                                                                                                                       |    |

| CHAP. 2 - ISOLATION TECHNOLOGIES FOR INTEGRATED CIRCUITS                                                                                                                                                                                                                                                                            | 12 |

| 2.1 BASIC ISOLATION PROCESSES FOR BIPOLAR ICs 13                                                                                                                                                                                                                                                                                    |    |

| 2.1.1 Junction Isolation, 13 2.1.1.1 Junction Isolation in the SBC Process 2.1.1.2 Collector-Diffusion Isolation                                                                                                                                                                                                                    |    |

| 2.2 BASIC ISOLATION PROCESS FOR MOS ICS (LOCOS ISOLATION) 17                                                                                                                                                                                                                                                                        |    |

| <ul> <li>2.2.1 Punchthrough Prevention between Adjacent Devices in MOS Circuits, 20</li> <li>2.2.2 Details of the Semirecessed Oxide LOCOS Process, 20</li> <li>2.2.2.1 Pad-Oxide Layer.</li> <li>2.2.2.2 CVD of Silicon Nitride Layer.</li> <li>2.2.2.3 Mask and Etch Pad-Oxide/Nitride Layer to Define Active Regions.</li> </ul> |    |

viii CONTENTS

- 2.2.2.4 Channel-Stop Implant.

- 2,2,2,5 Problems Arising from the Channel-Stop Implants.

- 2.2.2.6 Grow Field Oxide.

- 2.2.2.7 Strip the Masking Nitride/Pad-Oxide Layer.

- 2.2.2.8 Regrow Sacrificial Pad Oxide and Strip (Kooi Effect).

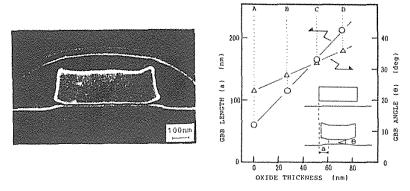

- 2.2.3 Limitations of Conventional Semi-Recessed Oxide LOCOS for Small-Geometry ICs, 27

### 2.3 FULLY RECESSED OXIDE LOCOS PROCESSES 28

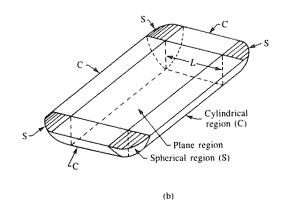

2.3.1 Modeling the LOCOS Process, 31

# 2.4 ADVANCED SEMIRECESSED OXIDE LOCOS ISOLATION PROCESSES 31

- 2.4.1 Etched-Back LOCOS, 31

- 2.4.2 Polybuffered LOCOS, 32

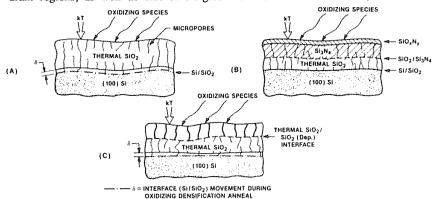

- 2.4.3 SILO (Sealed-Interface Local Oxidation), 33

- 2.4.4 Laterally Sealed LOCOS Isolation, 35

- 2.4.5 Bird's Beak Suppression in LOCOS by Mask-Stack Engineering, 38

- 2.4.6 Planarized SILO with High-Energy Channel-Stop Implant, 38

# 2.5 ADVANCED FULLY RECESSED OXIDE LOCOS ISOLATION PROCESSES 39

- 2.5.1 SWAMI (Sidewall-Masked Isolation Technique), 39

- 2.5.2 SPOT (Self-Aligned Planar-Oxidation Technology), 41

- 2.5.3 FUROX (Fully Recessed Oxide), 41

- 2.5.4 OSELO II, 43

# 2.6 NON-LOCOS ISOLATION TECHNOLOGIES I: (TRENCH ETCH AND REFILL) 45

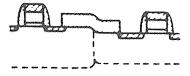

- 2.6.1 Shallow Trench and Refill Isolation, 45

- 2.6.1.1 BOX Isolation.

- 2.6.1.2 Modifications to Improve BOX Isolation.

- 2.6.2 Moderate-Depth Trench and Refill Isolation, 48

- 2.6.2.1 U-Groove Isolation.

- 2.6.2.2 Toshiba Moderate-Depth Trench Isolation for CMOS.

- 2.6.3 Deep, Narrow Trench and Refill, 51

- 2.6.3.1 Reactive Ion Etching of the Substrate.

- 2.6.3.2 Refilling the Trench.

- 2.6.3.3 Planarization after Refill.

CONTENTS

# 2.7 NON-LOCOS ISOLATION TECHNOLOGIES, II: SELECTIVE EPITAXIAL GROWTH (SEG) 58

- 2.7.1 Refill by SEG of Windows Cut into Surface Oxide, 59

- 2.7.2 Simultaneous Single-Crystal/Poly Deposition (SSPD), 60

- 2.7.3 Etching of Silicon Trenches and Refilling with SEG to Form Active Device Regions, 61

- 2.7.4 Selective-Epitaxial-Layer Field Oxidation (SELFOX), 61

- 2.7.5 SEG Refill of Trenches (as an Alternative to Poly Refill), 62

- 2.7.6 Epitaxial Lateral Overgrowth (ELO), 62

# 2.8 MISCELLANEOUS NON-LOCOS ISOLATION TECHNOLOGIES 63

- 2.8.1 Field-Shield Isolation, 63

- 2.8.2 Buried Insulator between Source/Drain Polysilicon (BIPS). 64

# 2.9 SUMMARY: CANDIDATE ISOLATION TECHNOLOGIES FOR SUBMICRON DEVICES 65

- 2.9.1 Basic Requirements of VLSI and ULSI Isolation Technologies, 65

- 2.9.2 The Need for Planarity, 65

- 2.9.3 How the Various Isolation Technologies Meet the Requirements, 66

# 2.10 SILICON-ON-INSULATOR (SOI) ISOLATION TECHNOLOGIES 66

- 2.10.1 Dielectric Isolation, 67

- 2.10.2 Wafer Bonding, 70

- 2.10.3 Silicon-on-Sapphire (SOS), 72

- 2.10.4 Separation by Implanted Oxygen (SIMOX), 72

- 2.10.5 Zone-Melting Recrystallization (ZMR), 75

- 2.10.6 Full Isolation by Porous Oxidized Silicon (FIPOS), 76

- 2.10.7 Novel SOI CMOS Processes with Selective Oxidation and Selective Epitaxial Growth, 77

#### REFERENCES 79

| CHAP. | 3 | *** | CONTA | CT  | TECHNOLOGY  | AND        |      |    |

|-------|---|-----|-------|-----|-------------|------------|------|----|

|       |   |     | LOCAL | INT | TERCONNECTS | <b>FOR</b> | VLSI | 84 |

# 3.1 THE ROLE OF CONTACT STRUCTURES IN DEVICE AND CIRCUIT BEHAVIOR 84

3.1.1 Contact Structures in Planar MOSFETs and Bipolar Transistors, 85

### 3.2 THEORY OF METAL-SEMICONDUCTOR CONTACTS 87

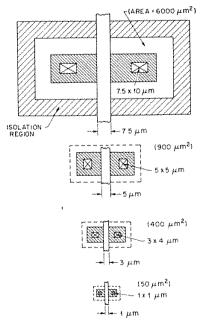

# 3.3 EXTRACTING VALUES OF SPECIFIC CONTACT RESISTIVITY FROM MEASUREMENTS 91

- 3.3.1 Extraction of the Specific Contact Resistivity from an Ideal Contact Structure, 92

- 3.3.2 Current Flow in Actual Contact Structures, 93

- 3.3.3 Contact Structures Used to Extract pc, 94

- 3.3.4 Procedure for Accurately Extracting pc from CBKR Test Structures, 97

- 3.3.5 Reported Values of pc for Various Contact Structures, 100

- 3.3.6 Use of a Simple Contact-Chain Structure to Monitor Contact Resistance, 101

# 3.4 THE EVOLUTION OF CONVENTIONAL METAL-TO-SILICON CONTACTS 101

- 3.4.1 The Basic Process Sequence of Conventional Ohmic-Contact Structures to Silicon, 102

- 3.4.2 Additional Details Concerning the Processing Steps, 103

- 3.4.2.1 Formation of the Heavily Doped Regions in the Silicon.

- 3.4.2.2 Formation of Contact Openings (Etching).

- 3.4.2.3 Sidewall Contouring of the Contact Holes by Reflow.

- 3.4.2.4 Sidewall Contouring by Etching.

- 3.4.2.5 Deposition.

- 3.4.2.6 Metal Deposition and Patterning.

- 3.4.2.7 Sintering the Contacts.

- 3.4.3 Aluminum-Silicon Contact Characteristics, 111

- 3.4.3.1 The Kinetics of the Al-Si Interface During Sintering.

- 3.4.4 Use of Aluminum-Silicon Alloys to Reduce Junction Spiking, 116

- 3.4.5 Platinum Silicide-to-Silicon Contacts, 117

- 3.4.5.1 Process Sequence Used to Form PtSi-Si Contacts.

- 3.4.5.2 Limitations of the PtSi-Si Contact Structure.

CONTENTS

#### 3.5 DIFFUSION BARRIERS 121

- 3.5.1 Theory of Diffusion Barrier Layers, 121

- 3.5.2 Materials Used as Diffusion Barriers, 124

- 3.5.2.1 Sputter-Deposited Titanium-Tungsten (Stuffed Barrier).

- 3.5.2.2 Polysilicon (Sacrificial Barrier).

- 3.5.2.3 Titanium (Sacrificial Barrier).

- 3.5.2.4 Titanium Nitride (Passive Barrier).

- 3.5.2.5 CVD Tungsten.

- 3.5.2.6 Experimental Diffusion Barrier Materials.

### 3.6 MULTILAYERED OHMIC-CONTACT STRUCTURES TO SILICON 131

- 3.6.1 Al-Ti:W-PtSi-Si Contacts, 132

- 3.6.2 Al-TiN-Ti-Si Contacts, 132

- 3.6.3 Mo-Ti:W-Si and Mo-Ti-Si Contacts. 134

#### 3.7 SCHOTTKY-BARRIER CONTACTS 134

# 3.8 THE IMPACT OF THE INTRINSIC SERIES RESISTANCE ON MOS TRANSISTOR PERFORMANCE 137

- 3.8.1 The Impact of R<sub>s</sub> on MOSFET Performance, 137

- 3.8.2 Estimates of R<sub>sh</sub>, R<sub>sp</sub>, R<sub>ac</sub>, and R<sub>co</sub>, 138

- 3.8.3 Impact of R<sub>s</sub> on Device Characteristics, 142

- 3.8.4 Summary of the Impact of Intrinsic Series- Resistance Effects on MOSFET Performance, 142

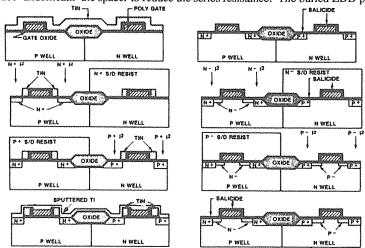

# 3.9 ALTERNATIVE (SELF-ALIGNED) CONTACT STRUCTURES FOR ULSI MOS DEVICES 143

- 3.9.1 Self-Aligned Silicide Contacts, 144

- 3.9.1.1 Self-Aligned Titanium Silicide Contacts.

- 3.9.1.2 Self-Aligned Cobalt Silicide Contacts.

- 3.9.1.3 Measuring r<sub>C</sub> of Self-Aligned Silicide Contacts.

- 3.9.2 Buried-Oxide MOS Contact Structure (BOMOS), 153

### 3.10 FORMATION OF SHALLOW JUNCTIONS AND THEIR IMPACT ON CONTACT FABRICATION 154

- 3.10.1 Conventional Shallow-Junction Formation, 154

- 3.10.2 Alternative Approaches to Forming Shallow Junctions, 155

- 3.10.3 Impact of Shallow Junctions on Contact Formation, 160

| ii | CONTENTS |

|----|----------|

|    |          |

| XII  | CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.11 | BURIED CONTACTS AND LOCAL INTERCONNECTS 16                                                                                                                                                                                                                                                                                                                                                                   | 60  |

|      | 3.11.1 Butted Contacts and Buried Contacts, 160 3.11.2 Local Interconnects, 162 3.11.2.1 Selectively Formed TiSi <sub>2</sub> . 3.11.2.2 Ti:W over CoSi <sub>2</sub> . 3.11.2.3 TiN Formed over TiSi <sub>2</sub> . 3.11.2.4 Dual-Doped Polysilicon LI with Diffused Source/Drain Junctions. 3.11.2.5 CVD W-Clad Polysilicon LI.                                                                             |     |

| REF  | ERENCES                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| СН   | AP. 4 - MULTILEVEL INTERCONNECT<br>TECHNOLOGY FOR VLSI AND ULSI                                                                                                                                                                                                                                                                                                                                              | 176 |

| 4.1  | EARLY DEVELOPMENT OF INTERCONNECT TECHNOLOGY FOR INTEGRATED CIRCUITS 176                                                                                                                                                                                                                                                                                                                                     |     |

|      | <ul> <li>4.1.1 Interconnects for Early Bipolar ICs, 176</li> <li>4.1.2 Interconnects in Silicon-Gate NMOS ICs, 178</li> <li>4.1.3 Evolution of Interconnects for Bipolar ICs, 179</li> <li>4.1.4 Evolution of Interconnects for CMOS ICs, 180</li> </ul>                                                                                                                                                     |     |

| 4.2  | THE NEED FOR MULTILEVEL INTERCONNECT TECHNOLOGIES 180                                                                                                                                                                                                                                                                                                                                                        |     |

|      | <ul> <li>4.2.1 Interconnect Limitations of VLSI, 181</li> <li>4.2.1.1 Functional Density.</li> <li>4.2.1.2 Propagation Delay.</li> <li>4.2.1.3 Ease of Design and Gate Utilization for ASICs and Wafer Scale Integration.</li> <li>4.2.1.4 Cost.</li> <li>4.2.2 Problems Associated with Multimetal Interconnect Processes,</li> <li>4.2.3 Terminology of Multilevel Interconnect Structures, 188</li> </ul> |     |

| 4.3  | MATERIALS FOR MULTILEVEL INTERCONNECT TECHNOLOGIES 189                                                                                                                                                                                                                                                                                                                                                       |     |

|      | 4.3.1 Conductor Materials for Multilevel Interconnects, 189 4.3.1.1 Requirements of Conductor Materials Used for VLSI Interconn 4.3.1.2 Local Interconnect Conductor Materials (Polysilicon, Metal-Si                                                                                                                                                                                                        |     |

CONTENTS xiii

- 4.3.1.3 Aluminum Metallization.

- 4.3.1.4 Tungsten and Other Conductor Materials for VLSI Interconnects.

- 4.3.2 Dielectric Materials for Multilevel Interconnects, 194

- 4.3.2.1 Requirements of Dielectric Layers in Multilevel Interconnects.

- 4.3.2.2 Poly-Metal Interlevel Dielectric (PMD) Materials.

- 4.3.2.3 CVD SiO<sub>2</sub> Films as Intermetal Dielectrics.

- 4.3.2.4 Low-Temperature-TEOS SiO<sub>2</sub> Films as Intermetal Dielectrics.

- 4.3.2.5 Other Materials and Deposition Processes Used to Form Intermetal Dielectrics.

### 4.4 PLANARIZATION OF INTERLEVEL DIELECTRIC LAYERS 199

- 4.4.1 Terminology of Planarization in Multilevel Interconnects, 199

- 4.4.1.1 Degree of Planarization.

- 4.4.1.2 The Need for Dielectric Planarization.

- 4.4.1.3 The Price that Must be Paid as the Degree of Dielectric Planarization is Increased.

- 4.4.1.4 Design Rules Related to Intermetal Dielectric-Formation and Planarization Processes.

- 4.4.2 Step Height Reduction of Underlying Topography as a Technique to Alleviate the Need for Planarization, 208

- 4.4.2.1 Provide Substrate Topography that is Completely Planar.

- 4.4.2.2 Provide a Planar Surface over Local Interconnect Levels.

- 4.4.2.3. Minimize the Thickness of the Metal 1 Layer.

- 4.4.2.4 Achieve Smoothing of Steps in DM1 by Sloping the Sidewalls of Metal-1 Lines.

- 4.4.3 Deposition of Thick CVD SiO<sub>2</sub> Layers and Etching Back Without a Sacrificial Layer, 211

- 4.4.4 Oxide Spacers, 212

- 4.4.5 Polyimides as Intermetal Dielectrics, 214

- 4.4.6 Planarizing by Use of Bias-Sputtered SiO2, 217

- 4.4.7 CVD SiO<sub>2</sub> and Bias-Sputter Etchback, 220

- 4.4.8 Planarization by Sacrificial Layer Etchback, 222

- 4.4.8.1 Degree of Planarization Achieved by Sacrificial Etchback.

- 4.4,8,2 Advantages of the Sacrificial Etchback Process.

- 4.4.8.3 Sacrificial Etchback Process Problems.

- 4.4.8.4 Alternative Sacrificial Etchback Processes.

- 4.4.9 Spin-On Glass (SOG), 449

- 4.4.9.1 SOG Process Integration.

- 4.4.9.2 The Etchback SOG Process.

- 4.4.9.3 The Non-Etchback SOG Process.

- 4.4.10 Electron-Cyclotron-Resonance Plasma CVD, 237

- 4.4.11 Chemical-Mechanical Polishing, 238

xiv CONTENTS

### 4.5. METAL DEPOSITION AND VIA FILLING 240

- 4.5.1 Conventional Approach to Via Fabrication and Formation of Metalto-Metal Contacts through the Vias, 240

- 45.1.1 Design Rules of Multilevel Metal Systems which are Impacted by Conventional Via Processing Limitations.

- 4.5.2 Advanced Via Processing (Vertical Vias and Complete Filling of Vias by Metal), 244

- 4.5.2.1 Increases in Packing Density Resulting from Advanced Via Process Technology.

- 4.5.3 Processing Techniques which Allow Vertical Vias to be Implemented, 245

- 4.5.3.1 Required Degree of Via Filling by Plugs.

- 4.5.4 CVD W Techniques for Filling Vertical Vias and Contact Holes, 245

- 4.5.4.1 General Information on the CVD Tungsten Process.

- 4.5.4.2 Blanket CVD W and Etchback.

- 4.5.4.3 Selective CVD W.

- 4.5.5 Other CVD Via Filling Processes, 253

- 4.5.5.1 Blanket CVD Polysilicon and Etchback for Contact Hole Filling.

- 4.5.5.2 Selective Deposition of Poly.

- 4.5.5.3 Selectively Formed Silicide Contact Plugs.

- 4.5.5.4 CVD Aluminum.

- 4.5.6 Alternatives to CVD for Filling of Vias, 254

- 4.5.6.1 Bias Sputtering of Al to Achieve Complete Filling of Via Holes.

- 4.5.6.2 Laser Planarization of Al Films.

- 4.5.6.3 Contact Hole and Via Filling by Selective Electroless Metal Deposition.

- 4.5.7 Pillar Formation as an Alternative to Filling Contact Holes and Vias, 258

### 4.6 FILLED GROOVES IN A DIELECTRIC LAYER 259

# 4.7 MANUFACTURING YIELD AND RELIABILITY ISSUES OF VLSI INTERCONNECTS 260

- 4.7.1 Factors Which Impact Manufacturing Yield, 261

- 4.7.2 Multilevel Interconnect-Related Yield Issues, 261

- 4.7.3 General Reliability Issues Associated with IC Interconnects, 264 4.7.3.1 Electromigration.

- 4.7.3.2 Electromigration at the Contacts.

- 4.7.3.3 Stress-Induced Metal Cracks and Voids.

- 4.7.3.4 Corrosion.

- 4.7.4 Reliability Issues Associated with Multilevel Interconnects, 268

#### CONTENTS

| 4.7.4.1 | Hillock Fo | rmation | and P   | revention | Measures |

|---------|------------|---------|---------|-----------|----------|

| 4742    | Dielectric | Void Re | liahili | tv Proble | ms.      |

### 4.8 PASSIVATION LAYERS 273

### 4.9 SURVEY OF MULTILEVEL METAL SYSTEMS 276

- 4.9.1 Bipolar Double-Level Metal Systems, 276

- 4.9.2 CMOS Double-Level-Metal Systems, 277

- 4.9.2.1 Non-Planarized DLM (2.0 μm CMOS).

- 4,9.2,2, Non-Planarized DLM: CVD-W Metal (2.0-\mu NMOS).

- 4.9.2.3 Resist Etchback, Bias-Sputtered SiO<sub>2</sub>, and SOG DLM for 1.5 μm CMOS.

- 4.9.2.4 Non-Sacrificial Layer Etchback DLM (1.0-μm CMOS).

- 4.9.2.5 Alternative CMOS DLM Process with Ti:W/Mo as Metal 1.

- 4.9.2.6 DLM Processes for Submicron CMOS.

- 4.9.3 Three-Level Metal Systems, 283

- 4.9.4 Four-Level Metal Systems, 285

### 4.10 SUMMARY OF MULTILEVEL INTERCONNECT TECHNOLOGY REQUIREMENTS FOR VLSI 286

REFERENCES 287

# CHAP. 5 - MOS DEVICES AND NMOS PROCESS INTEGRATION

298

### 5.1 MOS DEVICE PHYSICS 298

- 5.1.1 The Structure and Device Fundamentals of MOS Transistors, 298

- 5.1.2 The Threshold Voltage of the MOS Transistor, 301

- 5.1.3 Impact of Source-Body Bias on V<sub>T</sub> (Body Effect), 304

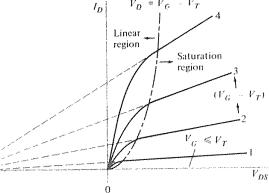

- 5.1.4 Current-Voltage Characteristics of MOS Transistors. 305

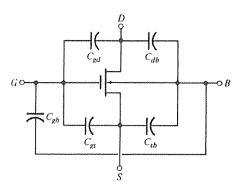

- 5.1.5 The Capacitances of MOS Transistors, 307

# 5.2 MAXIMIZING DEVICE PERFORMANCE THROUGH DEVICE DESIGN AND PROCESSING TECHNOLOGY 307

- 5.2.1 Output Current (ID) and Transconductance ( $g_{m}$ ), 308

- 5.2.2 Controlling the Threshold Voltage through Process and Circuit-Design Techniques, 309

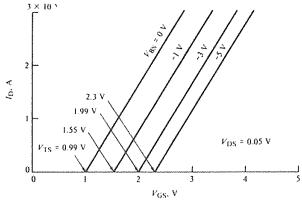

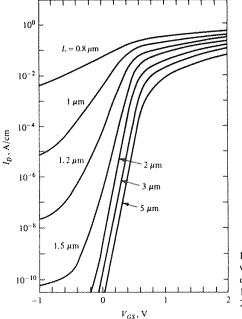

- 5.2.3 Subthreshold Currents (IDst when VG < IVTI), 311

- 5.2.4 Switching Speed, 313

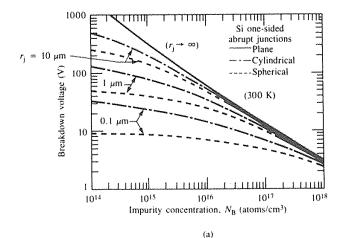

- 5.2.5 Junction Breakdown Voltage (Drain-to-Substrate), 313

- 5.2.6 Gate-Oxide Breakdown Voltage, 314

- 5.2.7 High Field-Region Threshold-Voltage Value, 315

# 5.3 THE EVOLUTION OF MOS TECHNOLOGY (PMOS AND NMOS) 315

- 5.3.1 Aluminum-Gate PMOS, 316

- 5.3.2 Silicon-Gate MOS Technology, 318

- 5.3.3 Reduction of Oxide-Charge Densities, 319

- 5.3.4 Ion Implantation for Adjusting Threshold Voltage, 321

- 5.3.5 Isolation Technology for MOS, 323

- 5.3.6 Short-Channel Devices, 323

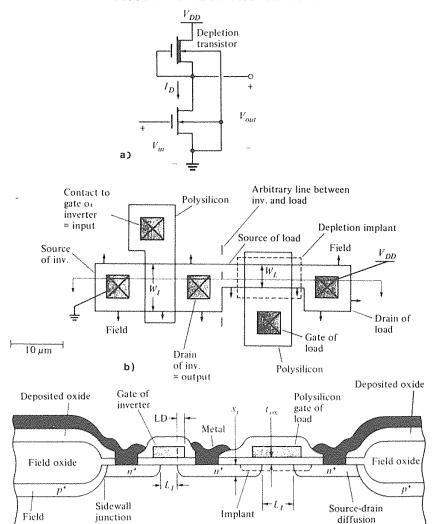

# 5.4 PROCESS SEQUENCE FOR FABRICATING NMOS INVERTERS WITH DEPLETION-MODE LOADS 324

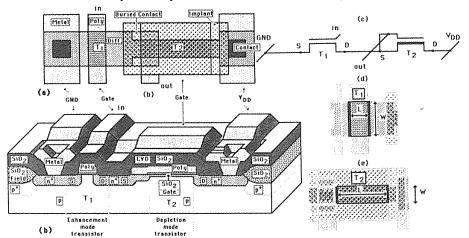

- 5.4.1 Operation of an NMOS Inverter with a Depletion-Mode Load, 324

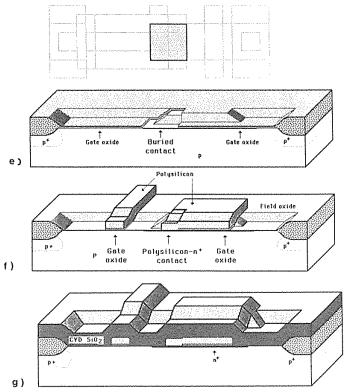

- 5.4.2 Process Sequence of a Basic E-D NMOS IC Technology, 327

- 5.4.2.1 Starting Material.

- 5.4.2.2 Active Region and Field Region Definitions.

- 5.4.2.3 Gate-Oxide Growth and Threshold-Voltage Adjust Implant

- 5.4.2.4 Polysilicon Deposition and Patterning.

- 5.4.2.5 Formation of the Source and Drain Regions.

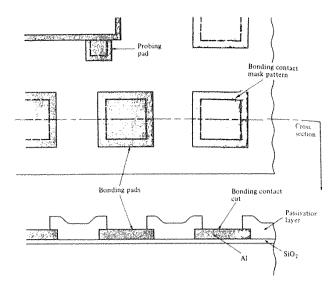

- 5.4.2.6 Contact Formation.

- 5.4.2.7 Metallization Deposition and Patterning.

- 5.4.2.8 Passivation Layer and Pad Mask,

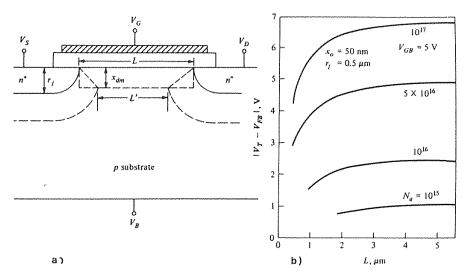

# 5.5 SHORT-CHANNEL EFFECTS AND HOW THEY IMPACT MOS PROCESSING 338

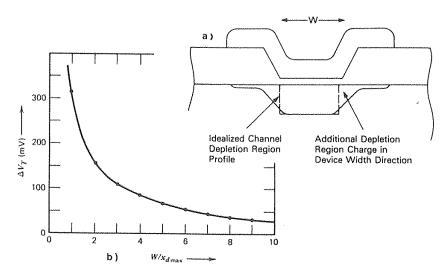

- 5.5.1 Effect of Gate Dimensions on Threshold Voltage, 338

- 5.5.1.1 Short Channel Threshold Voltage Effect.

- 5.5.1.2 Narrow Gate-Width Effect on Threshold Voltage.

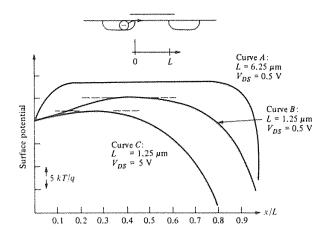

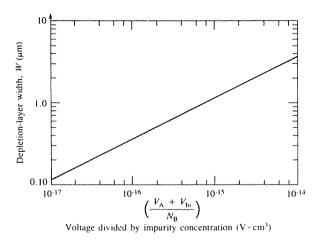

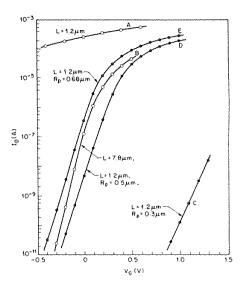

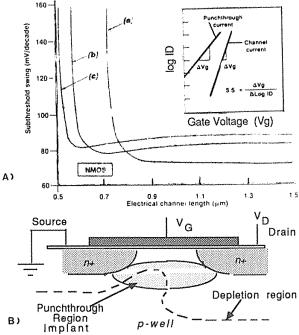

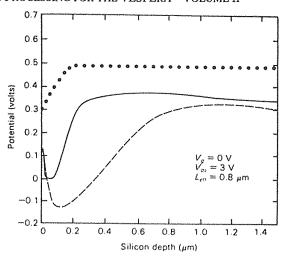

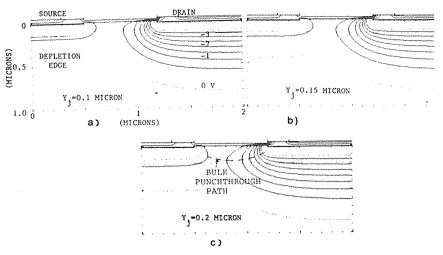

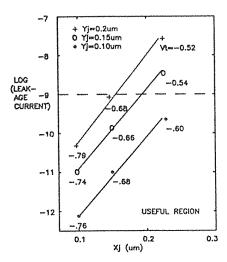

- 5.5.2 Short-Channel Effects on Subthreshold Currents (Punchthrough and Drain-Induced Barrier Lowering), 341

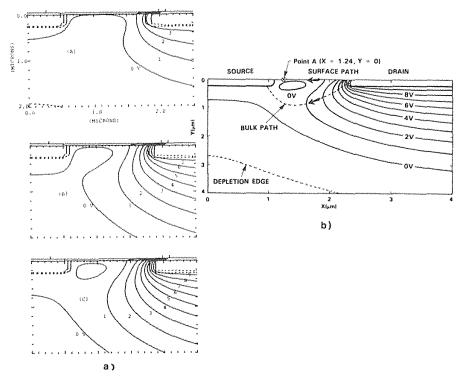

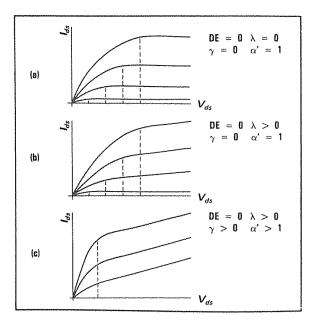

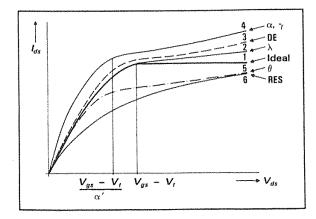

- 5.5.3 Short-Channel Effects on I-V Characteristics, 343

- 5.5.4 Summary of Short-Channel Effects on the Fabrication of MOS ICs, 346

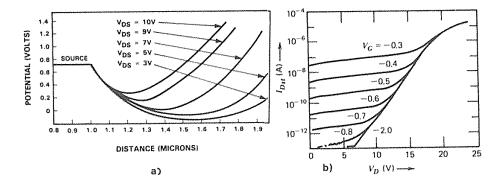

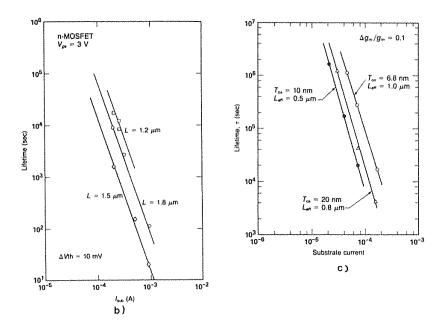

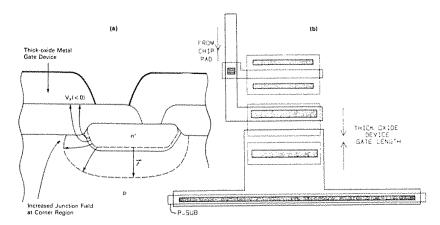

### 5.6 HOT-CARRIER EFFECTS IN MOSFETS 348

5.6.1 Substrate Currents Due to Hot Carriers, 349

vii

|     | CONTENIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | XVI |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

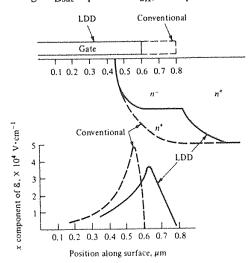

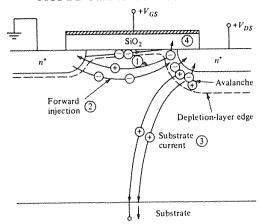

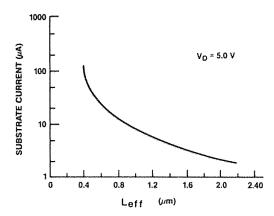

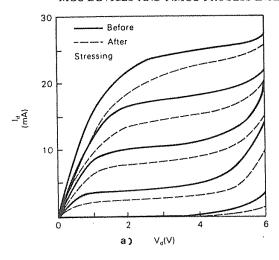

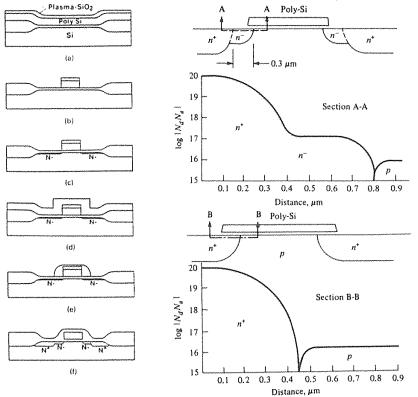

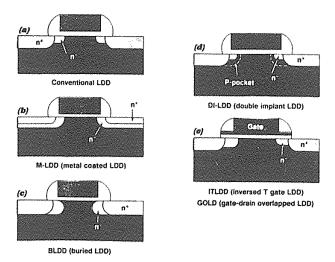

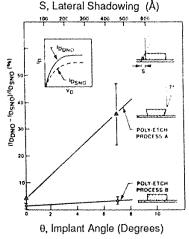

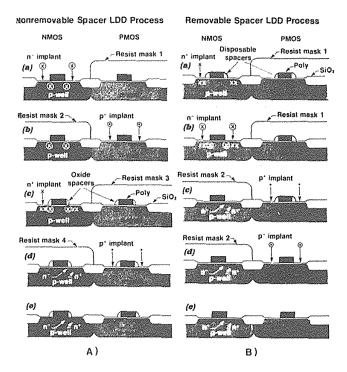

|     | <ul> <li>5.6.2 Hot-Carrier Injection into the Gate Oxide, 350</li> <li>5.6.3 Device-Performance Degradation Due to Hot-Carrier Effects,</li> <li>5.6.4 Techniques for Reducing Hot-Carrier Degradation, 354</li> <li>5.6.5 Lightly Doped Drains, 354</li> <li>5.6.5.1 Drain Engineering for Optimum LDD Structures.</li> <li>5.6.5.2 Asymmetrical Characteristics of LDD MOSFETs.</li> <li>5.6.6 The Impact of IC Processing on Hot-Carrier Device Degradation, 361</li> <li>5.6.7 Hot-Carrier Effects in PMOS Transistors, 362</li> <li>5.6.8 Gate-Induced Drain-Leakage Current, 363</li> </ul> | 352 |

| REF | ERENCES 363                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

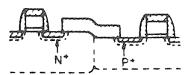

| СН  | AP. 6 - CMOS PROCESS INTEGRATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 368 |

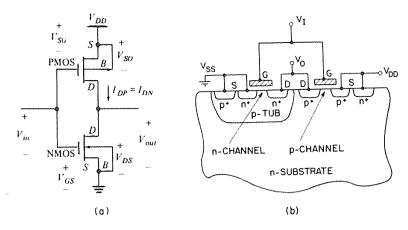

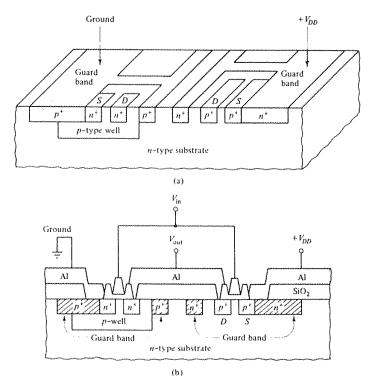

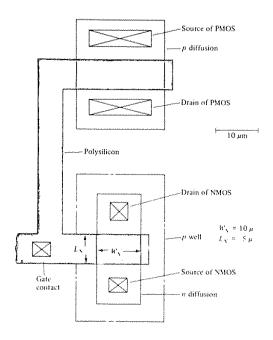

| 6.1 | INTRODUCTION TO CMOS TECHNOLOGY 368                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

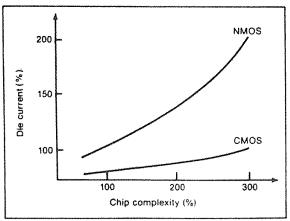

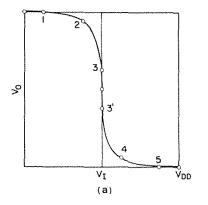

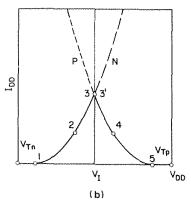

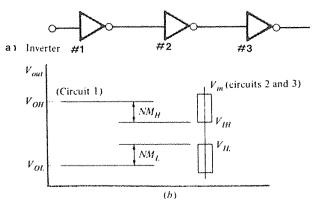

|     | <ul> <li>6.1.1 The Power-Dissipation Crisis of VLSI and How CMOS Came to Rescue, 368</li> <li>6.1.2 Historical Evolution of CMOS, 370</li> <li>6.1.3 Operation of CMOS Inverters, 373</li> <li>6.1.4 Advantages (and Disadvantages) of Modern CMOS Technologies, 376</li> <li>6.1.4.1 Device/Chip Performance Advantages.</li> <li>6.1.4.2 Reliability Advantages of CMOS.</li> <li>6.1.4.3 Circuit Design Advantages of CMOS.</li> <li>6.1.4.4 Cost Analysis of CMOS.</li> <li>6.1.5 Disadvantages of CMOS, 380</li> </ul>                                                                       | the |

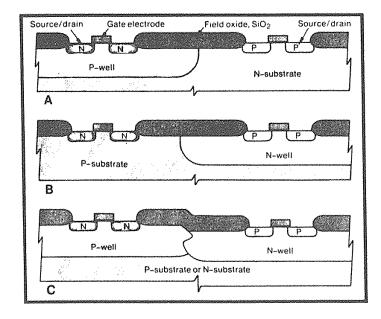

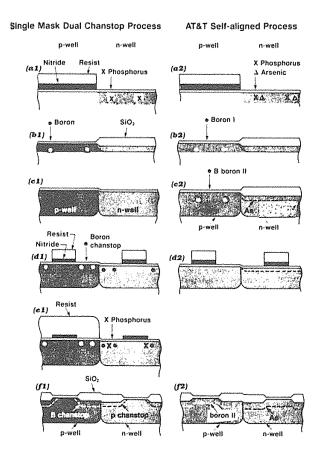

| 6.2 | THE WELL CONTROVERSY IN CMOS 381                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

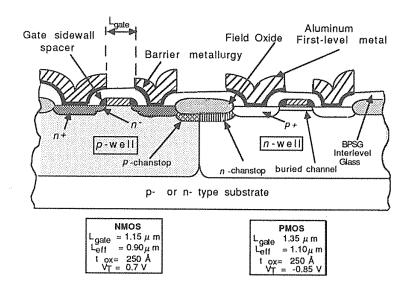

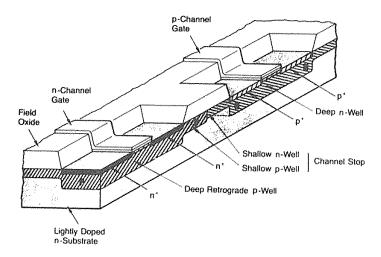

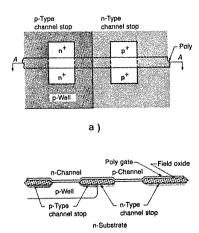

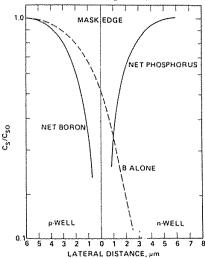

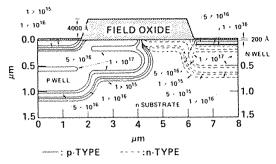

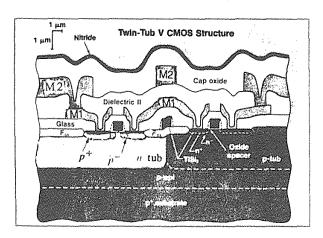

|     | 6.2.1 The Need for Wells in CMOS, 381 6.2.2 p-Well CMOS, 383 6.2.3 n-Well CMOS, 384 6.2.4 CMOS on Epitaxial Substrates, 385 6.2.5 Twin-Well CMOS, 387 6.2.6 Retrograde-Well CMOS, 389 6.2.7 Summary of CMOS Well-Technology Issues, 392                                                                                                                                                                                                                                                                                                                                                           |     |

| 6.3 | p-CHANNEL DEVICES IN CMOS 392                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

6.3.1 PMOS Devices with n+-Polysilicon Gates, 392

6.3.1.1 Punchthrough Susceptibility.

xviii CONTENTS

6.3.2 PMOS Devices with p+-Polysilicon Gates, 397

6.3.3 Gate Materials having Symmetrical Work Functions (with Respect to both NMOS and PMOS Devices), 398

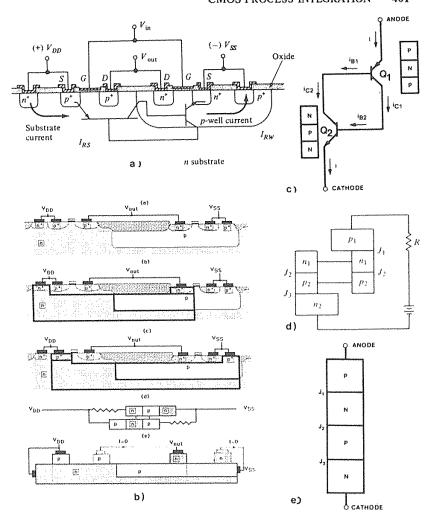

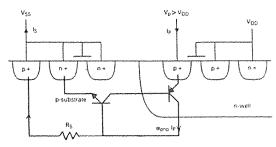

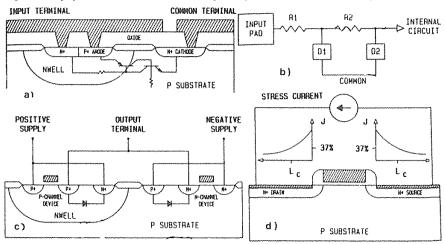

### 6.4 LATCHUP IN CMOS 400

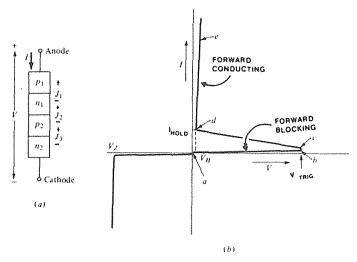

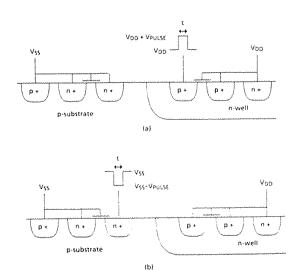

- 6.4.1 Parasitic pnpn Structures in CMOS Circuits, 400

- 6.4.2 Circuit Behavior of pnpn Diodes, 402

- 6.4.3 Device Physics Behavior of pnpn Diodes, 403

- 6.4.4 Summary of Conditions That Must Exist in Order for Latchup to Occur, 406

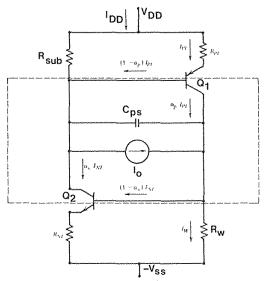

- 6.4.5 Circuit Behavior of Actual pnpn Structures in CMOS Circuits, 406

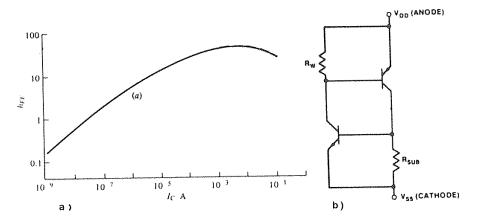

- 6.4.5.1 Value of β in CMOS Vertical Parasitic Bipolar Transistors.

- 6.4.5.2 Value of  $\beta$  in CMOS Lateral Parasitic Bipolar Transistors.

- 6.4.6 Circuit and Device Effects that Induce Latchup, 408

- 6.4.6.1 An external stimulus forward-biases the emitter-base of one transistor, and its collector current then turns-on the second transistor.

- 6.4.6.2 An external stimulus causes current to flow through both bypass resistors, forward-biasing one or both bipolar transistors.

- 6.4.6.3 Current is shunted through one of the parasitic transistors by some degradation mechanism, and the resulting collector current flows through the bypass resistor of the second transistor and turns it on.

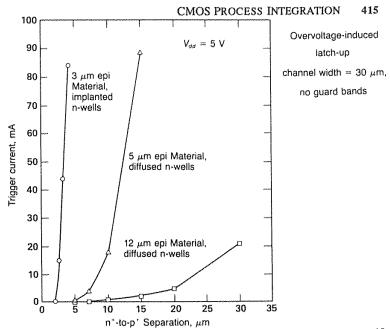

- 6.4.7 Test Methods for Characterizing Latchup, 410

- 6.4.7.1 Modelling Latchup in CMOS Technology.

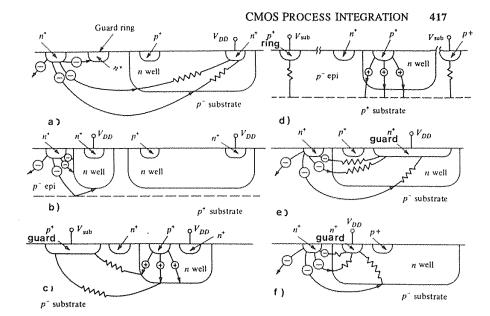

- 6.4.8 Techniques for Reduction

- or Elimination of Latchup Susceptibility, 413

- 6.4.8.1 Processing Techniques that Reduce the Current Gains of the Parasitic Bipolar Transistors.

- 6.4.8.2 Processing Techniques that Reduce R<sub>Sub</sub> and R<sub>w</sub> or Eliminate the pnpn Structure.

- 6.4.8.3 Circuit Layout Techniques used to Decouple Parasitic Bipolar Transistors

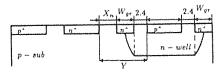

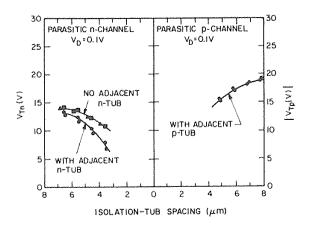

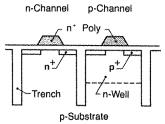

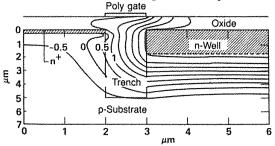

### 6.5 CMOS ISOLATION TECHNOLOGY 419

- 6.5.1 Trench Isolation for CMOS, 425

- 6.5.2 Isolation by Selective-Epitaxial Growth for CMOS, 426

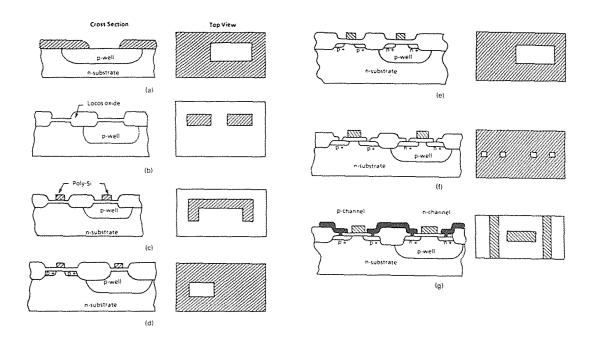

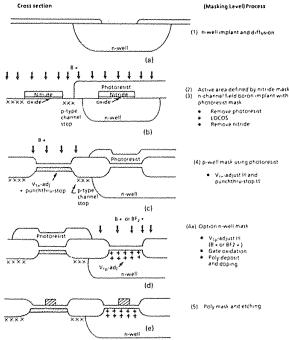

### 6.6 CMOS PROCESS SEQUENCES 428

- 6.6.1 Basic n-Well CMOS Process Sequence. 428

- 6.6.2 Twin-Well CMOS Process Sequence, 431

- 6.6.2.1 Starting Material.

- 6.6.2.2 Forming the Wells and Channel Stops.

| CONTENTS | KiX |

|----------|-----|

|          |     |

| 6.6.2.5 Polysilicon Deposition and Patterning. 6.6.2.6 Formation of the Source/Drain Regions. 6.6.2.7 CVD Oxide Deposition and Contact Formation. 6.6.2.8 Metal 1 Deposition and Patterning. 6.6.2.9 Intermetal Dielectric Deposition/Planarization and Via Patterning. 6.6.2.10 Metal 2 Deposition and Patterning. 6.6.2.11 Passivation Layer Deposition and Patterning.                                                                  | 3.  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.7 MISCELLANEOUS CMOS TOPICS 441                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| <ul> <li>6.7.1 Electrostatic Discharge Protection for CMOS, 441</li> <li>6.7.1.1 Diode Protection.</li> <li>6.7.1.2 Node-to-Node Punchthrough.</li> <li>6.7.1.3 Gate-Controlled Breakdown Structure.</li> <li>6.7.1.4 pnpn-Diode ESD Protection for Advanced CMOS Circuits.</li> <li>6.7.2 Power Supply Voltage Levels for Future CMOS, 446</li> <li>6.7.3 Low-Temperature CMOS, 446</li> <li>6.7.4 Three-Dimensional CMOS, 447</li> </ul> |     |

| REFERENCES 447                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| CHAPTER 7 - BIPOLAR AND                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| BICMOS PROCESS INTEGRATION                                                                                                                                                                                                                                                                                                                                                                                                                 | 453 |

| 7.1 BIPOLAR TRANSISTOR STRUCTURES<br>FOR INTEGRATED CIRCUITS 453                                                                                                                                                                                                                                                                                                                                                                           |     |

| <ul> <li>7.1.1 The Transistor Action 454</li> <li>7.1.1.1 Basic Bipolar Transistor Physics.</li> <li>7.1.1.2 Bipolar Transistor Current Gain.</li> <li>7.1.2 Integrated-Circuit Transistor Stuctures 458</li> </ul>                                                                                                                                                                                                                        |     |

| 7.2 DIGITAL CIRCUITS USING BIPOLAR TRANSISTORS 459                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 7.2.1 Basic Bipolar-Transistor Inverter Circuits 459 7.2.2 Bipolar Digital-Logic-Circuit Families 460                                                                                                                                                                                                                                                                                                                                      |     |

| 7.3 MAXIMIZING BIPOLAR TRANSISTOR PERFORMANCE THROUGH DEVICE DESIGN & PROCESSING TECHNOLOGY                                                                                                                                                                                                                                                                                                                                                | 464 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

6.6.2.3 Active and Field Region Definition.

6.6.2.4 Gate Oxide Growth and Threshold Voltage Adjustment.

- 7.3.1 Current Gain 464

- 7.3.2 Early Voltage 466

- 7.3.3 High-Level Injection Effects (Kirk Effect) 467

- 7.3.4 Operating-Voltage Limits in Bipolar Transistors 468

- 7.3.4.1 Reachthrough Breakdown.

- 7.3.4.2 Punchthrough Breakdown.

- 7.3.4.3 Breakdown Voltage and High-Level Injection Limits in Advanced Bipolar Transistors.

- 7.3.5 Parasitic Series Resistances in Bipolar Transistors 472

- 7.3.5.1 Collector Series Resistance, RC.

- 7.3.5.2 Base Series Resistance, R<sub>B</sub>.

- 7.3.5.3 Base-Spreading Resistance, R<sub>R2</sub> (and Emitter Current Crowding).

- 7.3.5.4 Emitter Series Resistance, R<sub>F</sub>.

- 7.3.6 Parasitic Junction Capacitances in Bipolar Transistors 475

- 7.3.6.1 Storage Capacitances in Bipolar Transistors.

- 7.3.7 Bipolar Transistor Unity-Gain Frequency, f 477

- 7.3.8 First Order npn Device Design 477

- 7.3.9 Switching Speed Behavior in Bipolar ICs 478

- 7.3.9.1 Propagation-Delay Time Calculation in Bipolar Transistors.

- 7.3.9.2 Propagation Delay in Digital MOS versus Digital Bipolar Circuits.

- 7.3.9.3 General Switching Speed Behavior of Digital Bipolar Circuits.

# 7.4 NON-OXIDE-ISOLATED BIPOLAR npn TRANSISTOR STRUCTURES 482

7.4.1 Triple-Diffused (3D) Process 483

#### 7.5 STANDARD-BURIED-COLLECTOR PROCESS 483

- 7.5.1 Characteristics of *npn* Transistors Fabricated with the Standard-Buried-Collector (SBC) Process 483

- 7.5.1.1 Limitations of Junction-Isolated SBC Transistors for VLSI Circuits.

- 7.5.2 Standard-Buried-Collector Process Flow 486

- 7.5.2.1 Starting Material.

- 7.5.2.2 Buried Layer Formation.

- 7.5.2.3 Epitaxial Growth.

- 7.5.2.4 Formation of Isolation Regions.

- 7.5.2.5 Deep-Collector Contact Formation (Optional).

- 7.5.2.6 Base Region Formation.

- 7.5.2.7 Emitter Region Formation.

- 7.5.2.8 Contact and Interconnect Layer Formation.

- 7.5.2.9 Washed Emitters.

- 7.5.2.10 Schottky Contacts.

#### 7.6 OXIDE-ISOLATED BIPOLAR TRANSISTORS 498

# 7.7 ADVANCED BIPOLAR TRANSISITOR STRUCTURES FOR VLSI AND ULSI 500

### 7.8 ADVANCED EMITTER STRUCTURES 501

- 7.8.1 Polysilicon Emitters 501

- 7.8.1.1 Models that Describe Polysilicon-Emitter Behavior.

- 7.8.1.2 Process Technology for Polysilicon-Emitter Fabrication.

- 7.8.2 Heterojunction Bipolar Transistors (HBTs) 506

#### 7.9 SELF-ALIGNED BIPOLAR STRUCTURES 510

- 7.9.1 Double-Polysilicon Self-Aligned Structures 510

- 7.9.1.1 Limitations of Double-Polysilicon SA Structures.

- 7.9.1.2 Current-Gain Degradation Due to Sidewall Injection in SA Bipolar Structures.

- 7.9.1.3 Link-Up Region Formation.

- 7.9.2 Single-Polysilicon Self-Aligned Bipolar Structures 516

- 7.9.3 Sidewall-Base-COntact Structures (SICOS) 520

#### 7.10 TRENCH-ISOLATED BIPOLAR TRANSISTORS 522

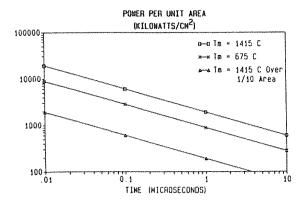

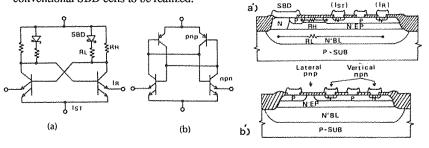

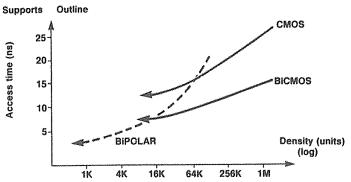

#### 7.11 BICMOS TECHNOLOGY 523

- 7.11.1 Device and Circuit Advantages of BiCMOS 524

- 7.11.1.1 Comparison of BiCMOs and CMOS Propagation Delay Times.

- 7,11,1,2 Power Consumption of BiCMOS versus CMOS Gates.

- 7.11.1.3 Capability of Providing Either TTL or ECL Outputs From a BiCMOS Chip.

- 7.11.1.4 Process Complexity Increases Associated with BiCMOS.

- 7.11.1.5 Extending Process Equipment Life by Fabricating BiCMOS.

### 7.12 CLASSIFICATION OF BICMOS TECHNOLOGIES 529

- 7.12.1 Digital BiCMOS Technology 531

- 7.12.1.1 Low-Cost Digital BiCMOS Technology.

- 7.12.1.2 High-Performance Digital BiCMOS.

- 7.12.1.3 Device-Design Issues Related to Optimizing a High-Performance Digital Modified-Twin-Well BiCMOS Process.

- 7.12.1.4 An Example Process Sequence for Fabricating High-Performance 5-V Digital BiCMOS ICs.

- 7.12.2 Process Integration of Analog/Digital BiCMOS 543

- 7.12.2.1 Process-Integration Issues of Medium-Voltage Analog BiCMOS.

- 7.12.2.2 An Example of an Analog/Digital BiCMOS Process.

| x | X | i | i |  |

|---|---|---|---|--|

|   |   |   |   |  |

| CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.12.3 BiCMOS Applications 551 7.12.3.1 Digital Logic Circuits and Gate Arrays. 7.12.3.2 Interface Driver Circuits. 7.12.3.3 BiCMOS SRAMs. 7.12.3.4 Analog/Digital Applications. 7.13 Trends in BiCMOS Technology 556                                                                                                                                                                                                                                                           |

| 7.13 COMPLEMENTARY BIPOLAR (CB) TECHNOLOGY 557                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| REFERENCES 560                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

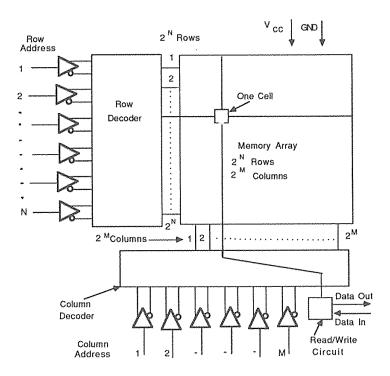

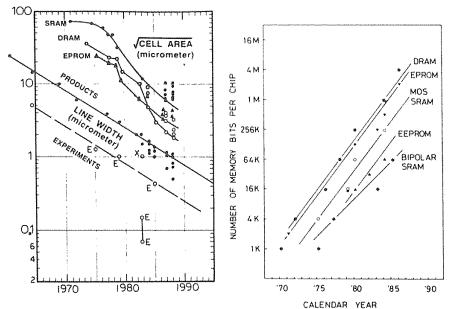

| CHAP. 8 - SEMICONDUCTOR MEMORY PROCESS INTEGRATION 557                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.1 TERMINOLOGY OF SEMICONDUCTOR MEMORIES 557                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <ul> <li>8.1.1 Random-Access and Read-Only Memories (RAMs and ROMs) 568</li> <li>8.1.2 Semiconductor-Memory Architecture 568</li> <li>8.1.3 Semiconductor-Memory Types 570</li> <li>8.1.4 Read Access Times and Cycle Times in Memories 571</li> <li>8.1.5 Recently Introduced On-Chip Peripheral Circuits 571</li> <li>8.1.6 Logic-Memory Circuits 571</li> </ul>                                                                                                              |

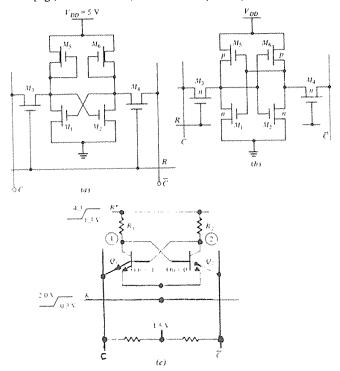

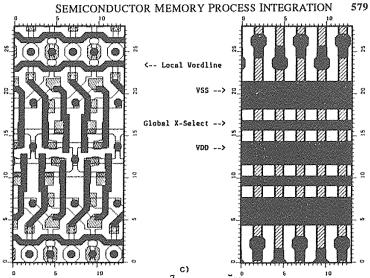

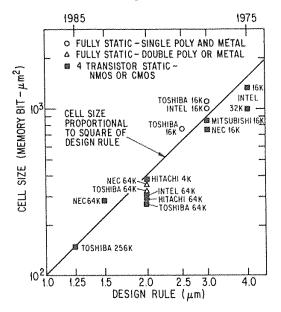

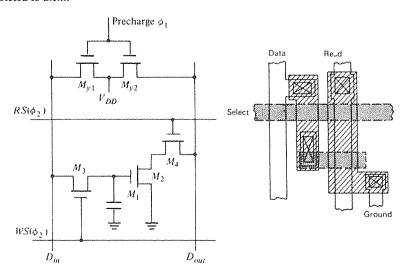

| 8.2 STATIC RANDOM-ACCESS MEMORIES (SRAMS) 572                                                                                                                                                                                                                                                                                                                                                                                                                                   |

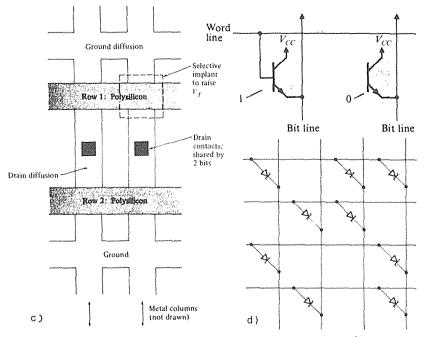

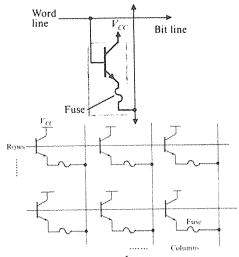

| 8.2.1 MOS SRAMs 575 8.2.1.1 Circuit Operation of MOS SRAM Cells. 8.2.1.2 SRAM Processing and Cell Layout Issues. 8.2.1.3. High-Valued Polysilicon Load-Resistors for MOS SRAMs 8.2.2 Bipolar and BiCMOS SRAMS 584 8.2.2.1 BiCMOS SRAMs.                                                                                                                                                                                                                                         |

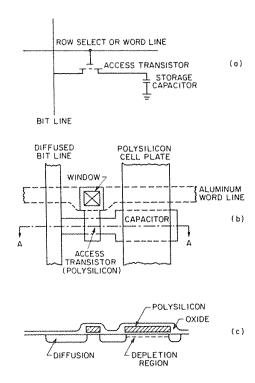

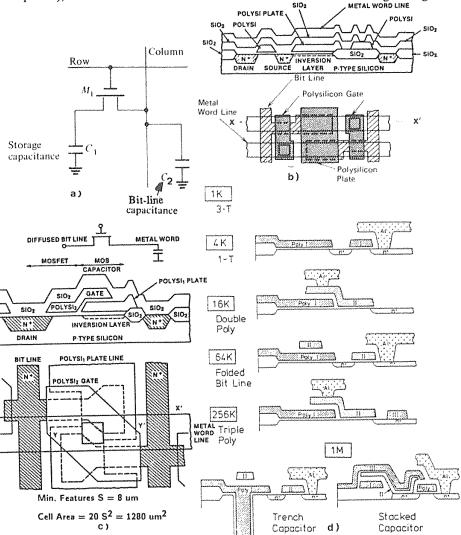

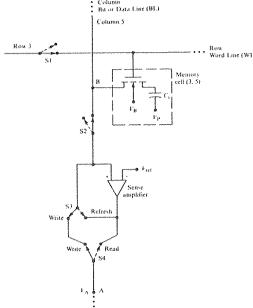

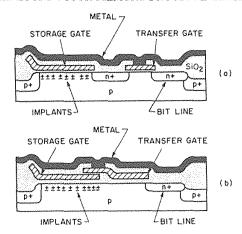

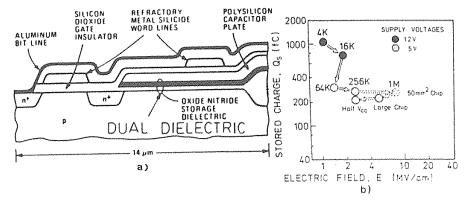

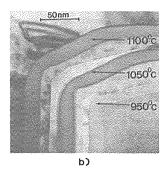

| 8.3 DYNAMIC RANDOM ACCESS MEMORIES (DRAMS) 587                                                                                                                                                                                                                                                                                                                                                                                                                                  |

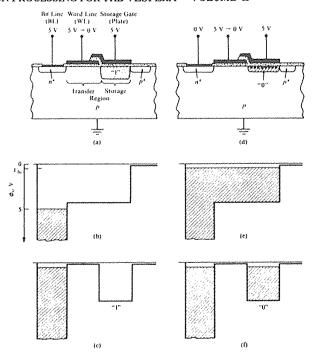

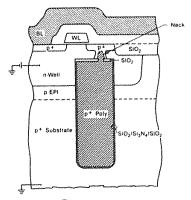

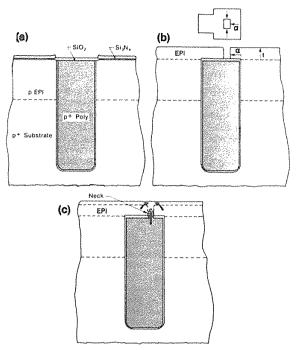

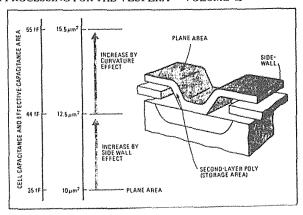

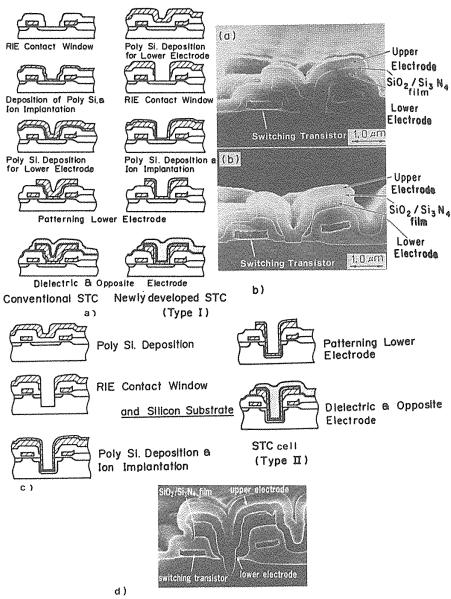

| <ul> <li>8.3.1 Evolution of DRAM Technology 587</li> <li>8.3.1.1 One-Transistor DRAM Cell Design.</li> <li>8.3.1.2 Operation of the One-Transistor DRAM Cell.</li> <li>8.3.1.3 Writing, Reading, and Refreshing DRAM Cells.</li> <li>8.3.1.4 Quantity of Charge Stored on DRAM Cells and Their Capacitance.</li> <li>8.3.1.5 High-Capacity (Hi-C) DRAM Cells.</li> <li>8.3.1.6 CMOS DRAMs.</li> <li>8.3.2 Design and Economic Constraints on Advanced DRAM Cells 597</li> </ul> |

CONTENTS xxiii

#### **CONTENTS**

- 9.1.4.2 Phenomenological versus Physical Models.

- 9.1.4.3 Gridding.

- 9.1.4.4 Interfacing One Simulator with Another.

### 9.2 ONE-DIMENSIONAL PROCESS SIMULATORS 653

- 9.2.1 SUPREM III (Stanford University PRocess Engineering Model III) 655

- 9.2.1.1 The Basic Operation and Capabilities of SUPREM III.

- 9.2.1.2 Additional Comments on the Use of SUPREM III.

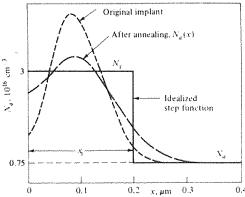

- 9.2.2 SUPREM III Models: Ion Implantation 658

- 9.2.3 SUPREM III Models: Diffusion in Silicon and SiO<sub>2</sub>, and Segregation Effects at the Si/SiO<sub>2</sub> Interface 663

- 9.2.3.1 Diffusion Models Used in SUPREM III.

- 9.2.3.2 Modeling Low Impurity-Concentration (Intrinsic) Diffusion in Silicon.

- 9.2.3.3 Modeling High-Impurity Concentration (Extrinsic) Diffusion in Silicon.

- 9.2.3.4 Oxidation-Enhanced Diffusion Modeling in SUPREM III.

- 9.2.3.5 Dopant Segregation Effects at the Si-SiO<sub>2</sub> Interface and Diffusion in SiO<sub>2</sub>.

- 9.2.4 SUPREM III Models: Thermal Oxidation of Silicon

in One-Dimension 669

- 9.2.4.1 High Dopant-Concentration Cases.

- 9.2.4.2 Modeling Other Factors Which Impact the Oxide Growth Rate.

- 9.2.4.3 Accuracy of Modeling Oxide Growth with SUPREM III.

- 9.2.5 SUPREM III Models: Epitaxial Growth 674

- 9.2.6 SUPREM III Models: Deposition, Oxidation, and Material Properties of Polysilicon Films 675

- 9.2.7 Creating a SUPREM III Input File 677

- 9.2.8 PREDICT 679

# 9.3 INTRODUCTION TO 2-DIMENSIONAL PROCESS SIMULATORS 680

9.3.1 Classes of 2-Dimensional Process Simulators 683

# 9.4 TWO-DIMENSIONAL DOPING-PROFILE AND OXIDATION PROCESS SIMULATORS 684

- 9.4.1 SUPRA (Stanford University PRocess Analysis Program) 684

- 9.4.1.1 SUPRA Ion Implantation Models.

- 9.4.1.2 SUPRA Diffusion Models.

- 9.4.1.3 SUPRA Oxidation Models.

- 9.4.1.4 SUPRA Epitaxial Model.

- 9.4.1.5 SUPRA Input File.

- 9.4.2 SUPREM IV 687

CONTENTS XXV

| 9.4.2.1 | SUPREM        | IV | Models | of Diffusion. |

|---------|---------------|----|--------|---------------|

| 9.4.2.2 | <b>SUPREM</b> | IV | Models | of Oxidation. |

- 9.4.2.3 SUPREM IV Models of Ion Implantation, Epitaxy, Deposition, and Etching.

- 9.4.2.4 SUPREM IV Input File Format.

- 9.4.2.5 Comparison of SUPRA and SUPREM IV for 2-D Process Simulation.

- 9.4.3 Two-Dimensional Simulation of Thermal Oxidation 690

- 9.4.3.1 Empirical Models of 2-D Thermal Oxidation.

- 9.4.3.2 Physical-Based Models of 2-D Thermal Oxidation.

#### 9.5 TWO-DIMENSIONAL TOPOGRAPHY SIMULATORS 696

# 9.6 SAMPLE (SIMULATION AND MODELING OF PROFILES IN LITHOGRAPHY AND ETCHING) 697

- 9.6.1 Simulating Optical Lithography Processes with SAMPLE 697

- 9.6.1.1 Optical Imaging Subprogram.

- 9.6.1.2 Resist Exposure Subprogram.

- 9.6.1.3 Resist Development Subprogram.

- 9.6.2 Simulating Etching and Deposition with SAMPLE 706

- 9.6.3 Creating Input Files for SAMPLE 708

### 9.7 OTHER 2-D TOPOGRAPHY SIMULATORS 710

- 9.7.1 PROLITH 710

- 9.7.2 DEPICT 710

- 9.7.3 PROFILE 711

- 9.7.4 SIMBAD 713

- 9.7.5 SIMPL (Simulated Programs from the Layout) 714

- 9.7.6 SIMPL-DIX 716

- 9.7.7 Manufacturing-Based Process Simulators 718

#### 9.8 DEVICE SIMULATORS 718

- 9.8.1 Simulation of MOS Device Characteristics under Subthreshold and Linear Operation (GEMINI) 719

- 9.8.2 Simulation of MOS Device Under All dc Operating Conditions (MINIMOS, CADDET, CANDE) 719

- 9.8.3 Bipolar Device Simulators (SEDAN, BIPOLE) 720

- 9.8.4 Combined MOS and Bipolar Device Simulators (PICSES, SIFCOD, PADRE, and FIELDAY) 721

| xxvi Contents                                                |     |

|--------------------------------------------------------------|-----|

| 9.9 CIRCUIT SIMULATORS AND ELECTRICAL PARAMET EXTRACTORS 723 | TER |

| 9.10 FUTURE CHALLENGES IN PROCESS SIMULATION                 | 723 |

| REFERENCES 724                                               |     |

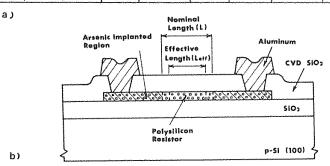

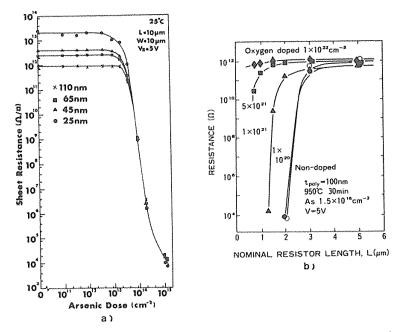

| APPENDIX A IC RESISTOR FABRICATION                           | 731 |

| APPENDIX B PROPERTIES OF SILICON AT 300 °K                   | 737 |

| APPENDIX C PHYSICAL CONSTANTS                                | 738 |

| NDEX                                                         | 730 |

### LIST OF TECHNICAL REVIEWERS

Each of the chapters was reviewed for technical correctness. The following persons graciously undertook the review task for the chapters indicated:

| Chapter | 2 | Dr. Joseph R. Monkowski        | Dr. Haiping Dun                |

|---------|---|--------------------------------|--------------------------------|

| *       |   | Lam Research Corp CVD Division | Intel Corp.<br>Santa Clara, CA |

|         |   | Fremont, CA                    |                                |

| Chapter | 3 | Dr. Robert S. Blewer<br>Sandia National Laboratories | Dr. Stan Swirhun<br>Honeywell SSPL<br>Bloomington, MN |

|---------|---|------------------------------------------------------|-------------------------------------------------------|

|         |   | Albuquerque, NM                                      | Bloomington, MN                                       |

| Chapter | 4 | Dr. Farhad K. Moghadam | Dr. Terry Herndon        |

|---------|---|------------------------|--------------------------|

| *       |   | Intel Corp.            | MIT - Lincoln Laboratory |

|         |   | Santa Clara, CA        | Lexington, MA            |

| Chapter | 5 | Mr. Andrew R. Coulson        |

|---------|---|------------------------------|

| -       |   | TRW Electronic Systems Group |

|         |   | Redondo Beach, CA            |

| Chapter 6 Dr. John Y. Chen Boeing Electronics Seattle, WA | Dr. Samuel T. Wang<br>International CMOS Technology, Inc.<br>San Jose, CA |

|-----------------------------------------------------------|---------------------------------------------------------------------------|

|-----------------------------------------------------------|---------------------------------------------------------------------------|

| Chapter | 8 | Professor Al F. Tasch, Jr University of Texas |

|---------|---|-----------------------------------------------|

|         |   | Austin, TX                                    |

Chapter 9 Dr. Michael Kump Technology Modeling Associates, Inc. Palo Alto, CA

### PREFACE

SILICON PROCESSING FOR THE VLSI ERA is a text designed to provide a comprehensive and up-to-date treatment of this important and rapidly changing field. The text will consist of three volumes, of which this book is the second, subtitled, *Process Integration*. Volume 1, subtitled *Process Technology*, was published in 1986. Volume 3, to be subtitled *Assembly*, *Packaging and Manufacturing Technology* is scheduled for publication in 1993. In Volume 1, the individual processes utilized in the fabrication of silicon VLSI circuits are covered in depth (e.g., epitaxial growth, chemical vapor and physical vapor deposition of amorphous and polycrystalline films, thermal oxidation of silicon, diffusion, ion implantation, microlithography, and etching processes).

In this volume, we undertake to explain how the individual processes described in Volume 1 are combined in various ways to produce silicon integrated circuits. This task is referred to as process integration. The first part of the book deals with subprocess integration; that is, the effort involved in forming circuit structures that can be implemented into a variety of circuit types. These structures include isolation structures (Chap. 2), metal-silicon contacts (Chap. 3), and device-interconnect structures (Chap. 4).

The second part of the book covers the process integration tasks of full-device-type technologies, including *NMOS* (Chap. 5), *CMOS* (Chap. 6), *bipolar* and *BiCMOS* (Chap. 7), and *semiconductor memories* (Chap. 8). Chapter 9 describes the process simulation tools that are available for aiding in the process integration and development efforts.

Volume 3 will cover process control, VLSI manufacturing issues and facilities, contamination and yield, automation, assembly, packaging, and parametric testing.

The purpose of writing this text was to provide professionals involved in the microelectronics industry with a single source that offers a complete overview of the technology associated with the manufacture of silicon integrated circuits. Other texts on the subject are available only in the form of specialized books (i.e., that treat just a small subset of all of the processes), or in the form of edited volumes (i.e., books in which a group of authors each contributes a small portion of the contents).

Such edited volumes typically suffer from a lack of unity in the presented material from chapter-to-chapter, as well as an unevenness in writing style and level of presentation. In addition, in multi-disciplinary fields, such as microelectronic fabrication, it is difficult for most readers to follow technical arguments in such books,

especially if the information is presented without defining each technical "buzzword" as it is first introduced.

In our books such drawbacks are avoided by treating the subject of VLSI fabrication from a unified and more pedagogical viewpoint, and by carefully defining technical terms when they are first introduced. The result is intended to be a user friendly book for workers who have come to the semiconductor industry after having been trained in but one of the many traditional technical disciplines.

An important technical breakthrough has occurred in publishing that the author also felt could be exploited in creating a unique book on silicon processing. That is, revolutionary electronic publishing techniques have recently become available, which can cut the time required to produce a published book from a finished manuscript. This task traditionally took 15-18 months, but can be now reduced to less than 3 months. If traditional techniques are used to produce books in such fast-breaking fields as VLSI fabrication, these books automatically possess a built-in obsolescence, even upon being first published.

We have taken advantage of these rapid production techniques, and have been able to successfully meet the reduced production-time schedule. As a result, information contained in technical journals and conferences which was available within three months of the book's publication date has been included.

Written for the professional, the book belongs on the bookshelf of workers in several microelectronic disciplines. Microelectronic fabrication engineers who seek to develop a more complete perspective of the subject, or who are new to the field, will find it invaluable. Integrated circuit designers, test engineers, and integrated circuit equipment designers, who must understand VLSI processing issues to effectively interface with the fabrication environment, will also find it a uniquely useful reference. The book should also be very suitable as a text for graduate-level courses on silicon processing techniques, offered to students of electrical engineering, applied physics, and materials science. It is assumed that such students already possess a basic familiarity with semiconductor device physics. Problems are included at the end of each chapter to assist readers in gauging how well they have assimilated the material in the text.

The book is an outgrowth of several intensive seminars conducted by the author through the Engineering Extension of the University of California, Irvine. Over one thousand engineers and managers from more than 75 companies and government agencies have enrolled in these short courses since they were first presented in 1984.

A book of this length and diversity would not have been possible without the indirect and direct assistance of many other workers. To begin, virtually all of the information presented in this text is based on the research efforts of a countless number of scientists and engineers. Their contributions are recognized to a small degree by citing some of their articles in the references given at the end of each chapter. The direct help came in a variety of forms, and was generously provided by many people. The text is a much better work as a result of this aid, and the authors express heartfelt thanks to those who gave of their time, energy, and intellect.

Each of the chapters was reviewed after the writing was completed. The engineers and scientists who participated in this review were numerous. The main reviewers are

listed on the page before the preface, and we would like to thank them once again at this point for their contributions. That is, the following professionals (each one an expert in the topic covered by the chapter they reviewed), read an entire chapter for technical correctness, and provided appropriate comments and corrections: Robert S. Blewer, John Y. Chen, Andrew R. Coulson, Haiping Dun, Terry Herndon, Michael Kump, Farhad K. Moghadam, Joseph R. Monkowski, Stan Swirhun, Al F. Tasch, Jr., and Samuel T. Wang. In addition, J. B. Price, of Spectrum CVD, Chris A. Mack, of the National Security Agency, and Sidney Marshall, Editor of Solid State Technology, provided other valuable technical and editorial input. Robert Shier, of VTC Corp., and Jim Cable of TRW also kindly provided the author with timely and valuable technical literature.

The copy editing of the book was undertaken by Mary Nadler, and the clarity and grammatical correctness of the prose owes a great deal to her professional efforts. The aesthetically pleasing graphics of the cover were designed by Roy Montibon of Visionary Art Resources, Inc., Santa Ana, CA.

Stanley Wolf

P.S. Additional copies of the books can be obtained from:

Lattice Press P.O. Box 340-W Sunset Beach, CA, 90742

An order form, for your convenience, is provided on the final leaf of the book.

### CHAPTER 1

### PROCESS INTEGRATION

### FOR VLSI and ULSI

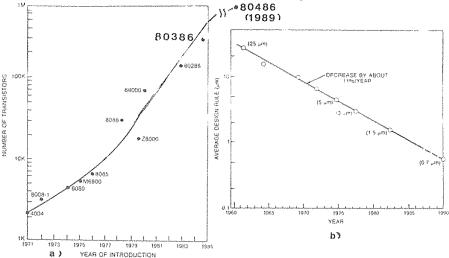

Since the creation of the first integrated circuit in 1960, the density of devices that can be fabricated on semiconductor substrates has steadily increased. In the late 1970s the number of devices manufactured on a chip exceeded the generally accepted definition of very large scale integration, or VLSI (i.e., more than 100,000 devices per chip) (Fig. 1-1a). By 1990 this number had grown to more than 32 million devices per chip (16-Mbit DRAMs), and it is generally acknowledged that the era of ultra-large-scale integration (ULSI) has begun. The increasing device count has been accompanied by a shrinking minimum feature size (Fig. 1-1b), which as of 1990 had decreased to  $\sim$ 0.5  $\mu$ m in the most advanced commercially available chips.

Fig. 1-1 (a) Increase in the number of transistors per microprocessor chip versus year of introduction, for a variety of 8-bit and 16-bit microprocessors, and (b) The decrease in minimum device feature size versus time on integrated circuits.

#### 2 SILICON PROCESSING FOR THE VLSI ERA - VOLUME II

Progress seems likely to continue at a rapid pace, with even further reductions in the unit cost per function and in the power-delay product of integrated circuits projected. Silicon processing has been the dominant technology of IC fabrication and is likely to retain this position for the foreseeable future. The entire adventure of silicon device manufacturing represents a remarkable application of scientific knowledge to the requirements of technology. Our books\* are intended to serve as a comprehensive and cohesive report on the state of the art of this technology, as practiced at the time of

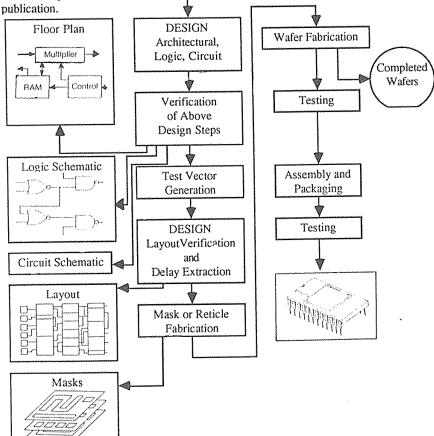

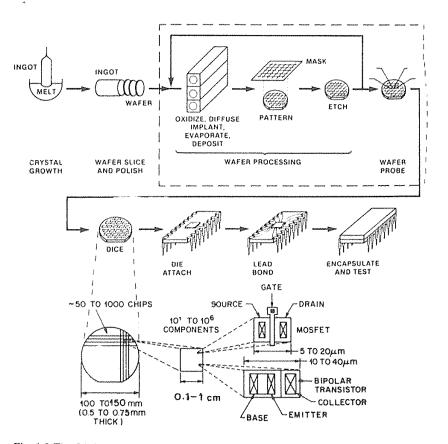

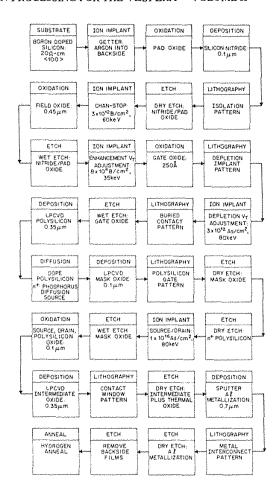

Fig. 1-2 Steps required for the manufacture of very large scale integrated circuits (VLSI).

<sup>\*</sup> SILICON PROCESSING FOR THE VLSI ERA - Volume 1: Process Technology; Volume 2 - Process Integration; and Volume 3 - Assembly, Packaging, and Manufacturing Technology (the latter is scheduled to to be published approximately in 1992)

Figure 1-2 illustrates the sequence of tasks followed in the manufacture of an integrated circuit. These tasks can be grouped into three phases: design, fabrication, and testing. Our books are concerned primarily with the fabrication phase. We describe the IC manufacturing steps that occur from the point at which the circuit design has been completed and the necessary design information has been rendered into the form of a circuit layout. In this form, the layout information is ready to be used to generate a set of masks (or reticles) that will serve as the tools for specifying the circuit patterns on silicon wafers. For VLSI and ULSI circuits, the layout information is stored in a computer.

The details concerning the individual fabrication processes (e.g., those associated with creating patterns, introducing dopants, and depositing films on silicon substrates to form integrated circuits) are the subjects of Volume 1. In this second volume, we

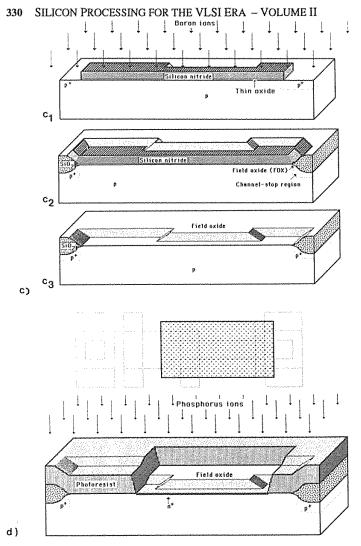

Fig. 1-3 The fabrication process sequence of integrated circuits.

#### 4 SILICON PROCESSING FOR THE VLSI ERA – VOLUME II

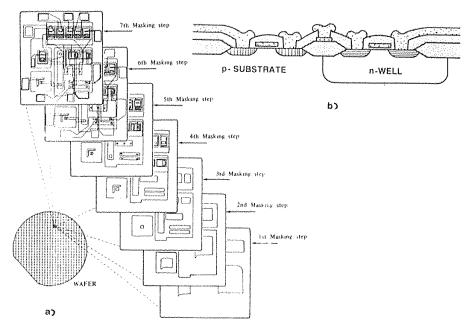

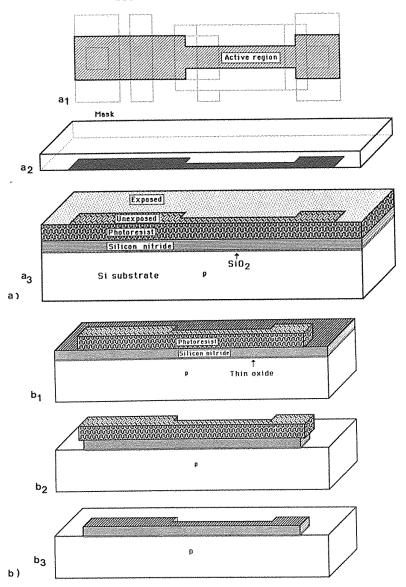

Fig. 1-4 (a) Example of the patterns transferred to a wafer during a seven-mask process sequence, and (b) Cross section of completed devices in a basic CMOS process.

undertake a discussion of the *sequences* of the steps performed to produce the device structures of the circuits. The text describes how the various individual processes are integrated together so that the end result is a completely realized integrated circuit.

One perspective of such a *process-integration* effort is illustrated in Fig. 1-4. It can be seen that a series of masking steps must be sequentially performed for the desired patterns to be created on the wafer surface. The other processing procedures performed between the masking steps serve to create the desired device structures. An example of the end result of a complete process sequence is shown in Fig. 1-4b as an IC cross-section.

This book is roughly divided into two parts. The first part deals with what we refer to as *subprocess integration* (Chapters 2, 3, and 4), while the second covers *complete process integration* (Chapters 5, 6, 7, and 8). Chapter 9 covers the subject of *process simulation*, an approach applicable to both the subprocess and complete process-integration development efforts.

The function of subprocess integration is to produce device structures that can be used in a variety of integrated-circuit technologies (i.e., isolation, contact, and interconnect structures). The purpose of the process-integration task is to design the process sequences used to manufacture complete IC technologies (i.e., NMOS, CMOS, bipolar, BICMOS, and IC memory devices).

### CHAPTER 5

# MOS DEVICES AND NMOS PROCESS INTEGRATION

This chapter deals with NMOS process integration. To provide background information for this topic, a review of the physics of long-channel MOS devices (i.e., whose channel lengths are greater than 2  $\mu$ m) and the basics of MOS circuit design is presented. Also included is a discussion of the relationship between desired device performance and process technology. (More rigorous treatments of MOS device physics are found in references 1 - 5.)

The history of NMOS processing is also presented, emphasizing how the obstacles to fabricating reliable NMOS ICs were overcome. A detailed example of the fabrication sequence of a typical NMOS inverter circuit culminates this discussion. The chapter concludes with a description of short-channel and hot-carrier effects in MOS devices, together with processing techniques developed to combat the problems they cause.

### 5.1 MOS DEVICE PHYSICS

# 5.1.1 The Structure and Device Fundamentals of MOS Transistors

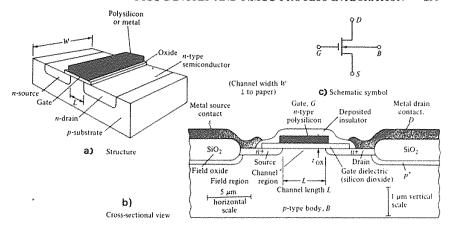

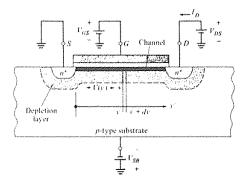

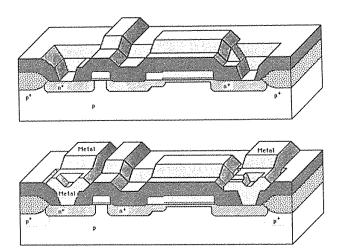

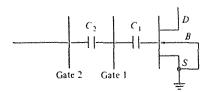

A perspective view of an *n*-channel MOSFET is shown in Fig. 5-1a, while additional details of its structure and its circuit symbol are given in Figs. 5-1b and 5-1c, respectively. The device has a gate terminal (to which the input signal is normally applied), as well as source and drain terminals (across which the output voltage is developed, and through which the output current flows, i.e., the drain-source current, ID). The gate terminal is connected to the gate electrode (a conductor), while the remaining terminals are connected to the heavily doped source and drain regions in the semiconductor substrate.

A *channel* region in the semiconductor under the gate electrode separates the source and drain. The channel (of length L and width W) is lightly doped with a dopant type opposite to that of the source and drain. The semiconductor is also physically separated

Fig. 5-1 (a) Structure of an MOS device. (b) Cross sectional view. (c) Schematic symbol. From D. A. Hodges and H. G. Jackson, *Analysis and Design of Digital Integrated Circuits*, Copyright, 1983 McGraw-Hill Book Co. Reprinted with permission.

from the gate electrode by an insulating layer (typically, SiO<sub>2</sub>), so that no current flows between the gate electrode and the semiconductor.

As shown in Fig. 5-1b, MOS transistors are symmetrical devices, which means that the source and drain are interchangable. In NMOS circuits, however, the more positive of these two electrodes is normally defined to be the drain, and thus the input signal is defined as the voltage between the gate and source terminals  $(V_{in} = V_G)$ .

In simplest terms, the operation of an MOS transistor involves the application of an input voltage to the gate electrode, which sets up a transverse electric field in the channel region of the device (5-2a). By varying this transverse electric field, it is possible to modulate the longitudinal conductance of the channel region. Since an electric field controls current flow, such devices are termed *field-effect transistors* (FETs). They are further described as *metal-oxide-semiconductor* (MOS) FETs because of the thin SiO<sub>2</sub> layer that separates the gate and substrate.

The substrate (or body) of the MOS transistor is a silicon wafer; this wafer also provides mechanical support for the finished circuit. In addition, an external electrical connection (or *terminal*) can be made to the body, making the MOS transistor a four-terminal device. (In later sections we will see how the transistor behavior is impacted if a bias is applied between the source and body terminals of the device.)

The top surface of the body consists of *active* or *transistor* regions as well as *passive* or *(field)* regions. The active regions are those in which transistor action occurs; i.e., the channel and the heavily doped source and drain regions. Conduction between separate active regions must be prevented (see chap. 2). A thick oxide layer  $(0.5-1.0 \ \mu m)$  is normally grown over the field regions as one of the measures to achieve this goal.

If no gate bias is applied, the electrical path between source and drain consists of two back-to-back two pn junctions in series. If a drain bias is applied such that the source-

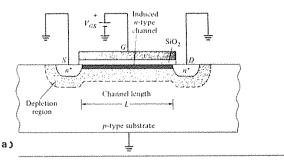

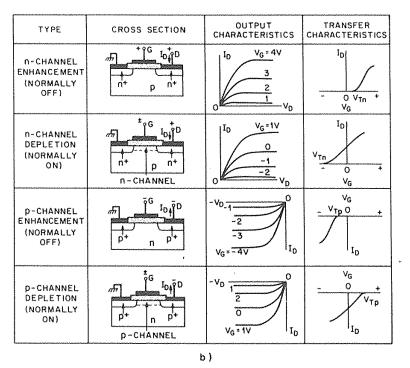

Fig. 5-2 (a) Idealized NMOS cross section with positive V<sub>GS</sub> applied showing depletion regions and the induced channel.<sup>7</sup> From D. A. Hodges and H. G. Jackson, *Analysis and Design of Digital Integrated Circuits*, Copyright, 1983 McGraw-Hill Book Co. Reprinted with permission. (b) Cross sections and output and transfer characteristics of four types of MOSFETs. <sup>7</sup> From S. M. Sze, *Semiconductor Devices - Physics and Technology*, Copyright, 1985, John Wiley & Sons. Reprinted with permission.

body and drain-body junctions remain reverse-biased, I<sub>D</sub> will consist of only the reverse-bias diode leakage current and hence will be considered negligibly small.

When positive bias is applied to an NMOS transistor gate, electrons will be attracted to the channel region and holes will be repelled. (Holes are the majority carriers in the channel of the p-type body when no gate bias exists.) Once enough electrons have been drawn into the channel by the positive gate voltage to exceed the hole concentration, the region behaves like a n-type semiconductor. Under these circumstances, an n-type channel connects the source and drain regions (Fig. 5-2a). Current will flow if a voltage,  $V_{DS}$ , is applied between the source and the drain terminals. The voltage-induced n-type channel does not form unless the voltage applied to the gate exceeds the threshold voltage,  $V_T$ .

MOS devices such as those just described, in which no conducting channel exists when  $V_G = 0$ , are referred to as enhancement-mode (or normally OFF) transistors (see Fig. 5-2b). With NMOS enhancement-mode transistors, a positive gate voltage,  $V_G$ , greater than  $V_T$  must be applied to create the channel (or to turn them ON), while to turn ON PMOS enhancement-mode devices, a negative gate voltage (whose magnitude is  $>V_T$ ) must be applied. Note that in NMOS transistors a positive voltage must also be applied to the drain to keep the drain-substrate reverse-biased, while in PMOS devices this voltage must be negative.

On the other hand, it is also possible to build MOS devices in which a conducting channel region exists when  $V_G = 0$  V (see Fig. 5-2b), and such MOS devices are described as being *normally ON*. Since a bias voltage to the gate electrode is needed to deplete the channel region of majority carriers (that is, the channel is eradicated as long as the bias is applied), such devices are also commonly called *depletion-mode* devices. NMOS depletion-mode devices require a negative gate voltage to be turned *OFF*, while corresponding PMOS devices require positive gate voltages.

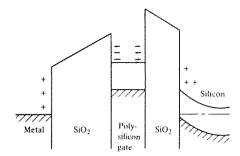

### 5.1.2 The Threshold Voltage of the MOS Transistor

If the source and body of an MOS transistor are both tied to ground ( $V_{SB} = 0$ ), the threshold voltage,  $V_T$ , of the transistor can be found from the following equation (note that  $V_T = V_{T0}$  when  $V_{SB} = 0$ ):

$$V_{T0} = \varphi_{ms} - 2\varphi_f - Q_{tot}/C_{ox} - Q_{BO}/C_{ox}$$

(5-1)

where  $\phi_{ms}$  is the workfunction difference (in V) between the gate material and the bulk silicon in the channel,  $\phi_f$  is the equilibrium electrostatic potential in a semiconductor (in V),  $Q_{BO}$  is the charge stored per unit area (C/cm²) in the depletion region (when the voltage between source and body is zero),  $C_{ox}$  is the gate-oxide capacitance per unit area (F/cm²), and  $Q_{tot}$  is the total positive oxide charge per unit area present at the interface between the oxide and the bulk silicon (see section 5.3.3).

Expressions have been established for these various quantities in terms of doping concentrations in the material, physical constants, device structure dimensions, and temperature. They are:

Fig. 5-3 Work-function difference  $\phi_{ms}$  versus doping for degenerate polysilicon and Al electrodes. 80 Reprinted with permission of Solid-State Electronics.

$$\varphi_f = kT/q \ln (n_i/N_A)$$

(p-type semiconductor) (5 - 2a)

$$\varphi_f = kT/q \ln (N_D/n_i)$$

(n-type semiconductor) (5 - 2b<sub>-</sub>)

where NA is the acceptor concentration in a p-type semiconductor (cm<sup>-3</sup>), ND is the donor concentration in an n-type semiconductor, and  $n_i$  is the intrinsic carrier concentration in the semiconductor. Note that  $n_i$  is a strong function of temperature. For silicon at 300 K, however,  $n_i = 1.45 \times 10^{10}$  cm<sup>-3</sup>. Therefore, at 300 K:

$\Phi$ ms (metal gate, with Al as gate electrode) =  $\Phi$ f(sub) -  $\Phi$ f(Al) =  $\Phi$ f(sub) - (+0.6 V) (5 - 3a)

$$\Phi_{ms}$$

(Si gate) =  $\Phi_{f(sub)} - \Phi_{f(gate)}$  (5 - 3b)

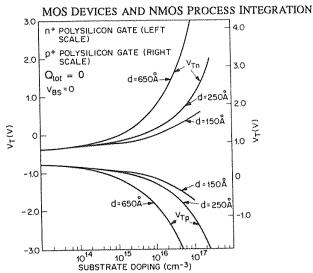

Figure 5-3 shows the value of  $\varphi_{ms}$  for various substrate-doping values if an aluminum gate electrode is used. Note also that in silicon-gate NMOS, the doping of the polysilicon gate material is usually n-type, with ND  $\approx 10^{20}$ /cm<sup>3</sup>, so that  $\varphi_{f(gate)}$  in this case is +0.59 V. Figure 5-4 shows the value of the threshold voltage of  $n^+$  silicon gate MOS transistors (both PMOS and NMOS) versus substrate doping concentration, assuming either a 65-nm, a 25-nm, or a 15-nm thick gate oxide, and  $Q_{tot}=0$ .

Q<sub>BO</sub> is found from:

$$Q_{BO} = -\sqrt{2 q N_A \varepsilon_{si} \left| -2\phi_f \right|} \qquad NMOS \qquad (5-4a)$$

$$Q_{BO} = + \sqrt{2 q N_D \varepsilon_{si} | -2\phi_f|} \qquad PMOS \qquad (5-4b)$$

and Cox is calculated from:

$$C_{ox} = \varepsilon_{ox} / t_{ox} = 3.9 \varepsilon_{o} / t_{ox}$$

(5-5)

where  $\varepsilon_{si} = 11.8 \ \varepsilon_{o}$ ,  $\varepsilon_{o}$  is the permittivity of vacuum, and  $\varepsilon_{ox}$  and  $t_{ox}$  are the permittivity and thickness of the gate oxide.