# LOCAL AREA NETWORKS

ANSI/IEEE Standard Draft International Standard

> Carrier Sense Multiple Access with Collision Detection

# An American National Standard IEEE Standards for Local Area Networks:

Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications

Published by The Institute of Electrical and Electronics Engineers, Inc

Distributed in cooperation with Wiley-Interscience, a division of John Wiley & Sons, Inc

IEEE Standards documents are developed within the Technical Committees of the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Board. Members of the committees serve voluntarily and without compensation. They are not necessarily members of the Institute. The standards developed within IEEE represent a consensus of the broad expertise on the subject within the Institute as well as those activities outside of IEEE which have expressed an interest in participating in the development of the standard.

Use of an IEEE Standard is wholly voluntary. The existence of an IEEE Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE Standard. Futhermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard. Every IEEE Standard is subjected to review at least once every five years for revision or reaffirmation. When a document is more than five years old, and has not been reaffirmed, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE Standard.

Comments for revision of IEEE Standards are welcome from any interested party, regardless of membership affiliation with IEEE. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments.

Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of IEEE, the Institute will initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of all concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason IEEE and the members of its technical committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments on standards and requests for interpretations should be addressed to:

Secretary, IEEE Standards Board 345 East 47th Street New York, NY 10017 USA

ANSI/IEEE Std 802.3-1985 ISO Draft International Standard 8802/3

# An American National Standard IEEE Standards for Local Area Networks:

# Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications

Sponsor

Technical Committee on Computer Communications of the IEEE Computer Society

> Approved June 24, 1983 IEEE Standards Board

Approved December 21, 1984

American National Standards Institute

p. 5

This standard has been adopted for U.S. federal government use.

Details concerning its use within the federal government are contained in FIPS PUB 107, Local Area Networks: Base Band Carrier Sense Multiple Access with Collision Detection Access Method and Physical Layer Specifications and Link Layer Protocol. For a complete list of the publications available in the FEDERAL INFORMATION PROCESSING STANDARDS Series, write to the Standards Processing Coordinator, Institute for Computer Sciences and Technology, National Bureau of Standards, Gaithersburg, MD 20899, U.S.A.

Second Printing (8½" × 11") for NTIS (see page 143)

ISBN 0471-82749-5

Library of Congress Catalog Number 84-43096

© Copyright 1985 by

The Institute of Electrical and Electronics Engineers, Inc 345 East 47th Street, New York, NY 10017 USA

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher

December 31, 1984 SH09738

## Foreword

(This Foreword is not a part of IEEE Std 802.3-1985, Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications.)

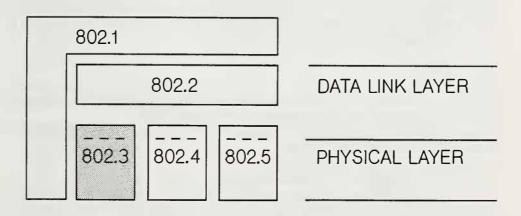

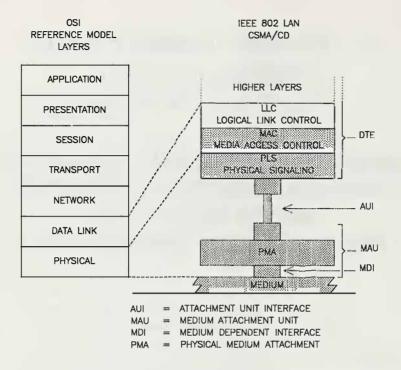

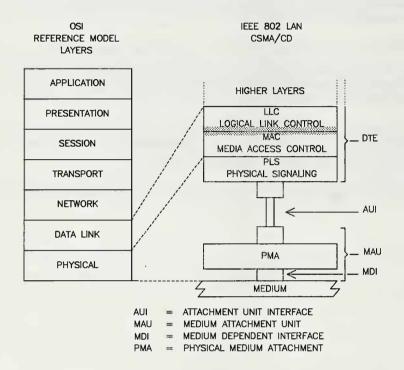

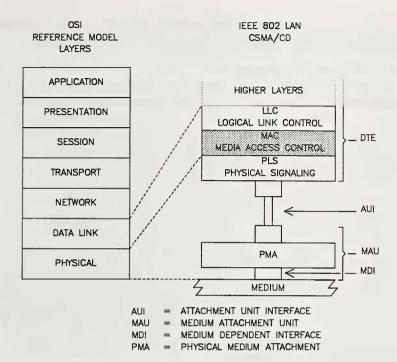

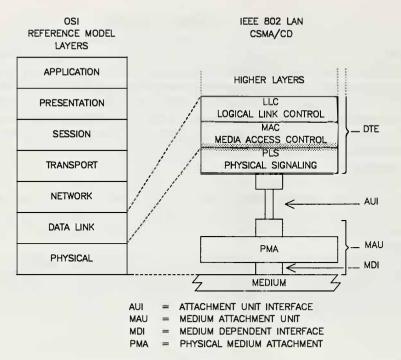

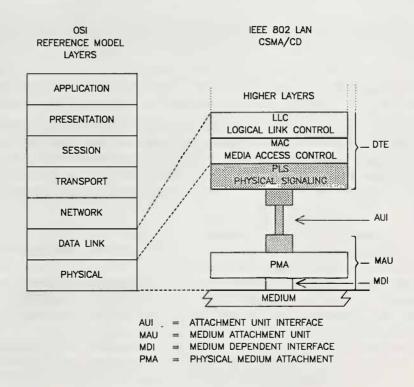

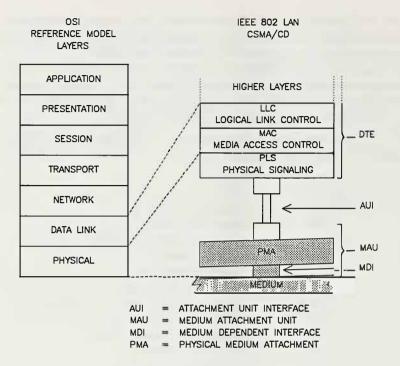

This standard is part of a family of standards for Local Area Networks (LANs). The relationship between this standard and other members of the family is shown below. (The numbers in the figure refer to IEEE standard numbers.)

This family of standards deals with the Physical and Data Link Layers as defined by the ISO Open System Interconnection Reference Model. The access standards define three types of media access technologies and associated physical media, each appropriate for particular applications or system objectives. The standards defining these technologies are

- (1) IEEE Std 802.3-1985 (ISO DIS 8802/3), a bus utilizing CSMA/CD as the access method

- (2) IEEE Std 802.4-1985 (ISO DIS 8802/4), a bus utilizing token passing as the access method

- (3) IEEE Std 802.5-1985 (ISO DP 8802/5), a ring utilizing token passing as the access method

Other access methods (for example, metropolitan area networks) are under investigation. IEEE Std 802.2-1985 (ISO DIS 8802/2), the Logical Link Control standard, is used in conjunction with the medium access standards.

IEEE P802.1 describes the relationship among these standards and their relationship to the ISO Open System Interconnection Reference Model in more detail. This companion document also will contain networking management standards and information on internetworking. The reader of this standard is urged to become familiar with the complete family of standards.

The local area network access mechanism specified by this standard may include patented matter. The IEEE Standards Office calls attention to the fact that it is claimed that the process of the local area network access mechanism described throughout this standard is the subject of United States patent numbers 4 063 220 and 4 099 024 and corresponding patent of foreign countries owned by the Xerox Corporation. Although these patents appear to cover the access mechanism subject in this standard, the IEEE takes no position with respect to patent validity. The Xerox Corporation has assured the IEEE that it is willing to grant a license under these patents on reasonable and nondiscriminatory terms and conditions to anyone wishing to obtain such a license. The Xerox Corporation's undertakings in this respect are on file with the IEEE Standards Office and the license details may be obtained from the Office of General Counsel of Xerox Corporation, whose address is PO Box 1600, Stamford, CT 06904, USA.

### **ISO Standard**

Portions of the text of this standard are the standard ISO 8802/3, supported by the ISO, International Organization for Standardization.

Some portions of the text of this standard are peculiar to IEEE Std 802.4-1984, specifically areas relating to

(1) References to national standards

(2) Recommendations and guidelines related to safety concerns

To avoid duplications of standards the ISO has not developed a separate international standard. Those sections of this standard that are not part of the International Standard are prefaced with a note enclosed in braces "{...}".

At the time this text was printed, ISO Standard 8802/2 was a Draft International Standard (DIS).

#### IEEE Std 802.3-1985

The first edition of the standard defines a 10 Mb/s baseband implementation of the Physical Layer using the CSMA/CD access method. It is anticipated that future editions of the standard may provide additional implementations of the physical layer to support different needs (for example, media, and data rates).

This standard contains state-of-the-art material. The area covered by this standard is undergoing evolution. Revisions are anticipated to this standard within the next few years to clarify existing material, to correct possible errors, and to incorporate new related material.

Readers wishing to know the state of revisions should contact the 802.3 Working Group Chairman through

Secretary, IEEE Standards Board Institute of Electrical and Electronics Engineers, Inc 345 East 47th Street New York, NY 10017 USA The IEEE 802.3 Working Group that developed this standard had the following membership during the ballot cycle:

# Donald C. Loughry, Chairman

Phil L. Arst

Robert F. Bridge

Charles Brill

G. J. Clancy

John Davidson

Ralph DeMent

Hank (H. N.) Dorris

Judith Estrin

Richard Fabbri

Ingrid Fromm

Milton C. Harper

Bryan Hoover

George D. Jelatis

Harold W. Katz

Donald E. Kotas

William P. Lidinsky

Laurie Lindsey

William D. Livingston

J. Luque

Daniel Maltbie

Jerry McDowell

C. Kenneth Miller

Robert L. Morrell

Wendell Nakamine

W. P. Neblett

James Nelson

Thomas L. Phinney

David Potter

Robert S. Printis

Gary S. Robinson

Robert Rosenthal

Gary Stephens

Daniel P. Stokesberry

Ken F. Sumner

Daniel Sze

Victor J. Tarassov

P. E. Wainwright

Lyle Weiman

Hugh E. White

Choa-Ping Wu

Nick Zades

Mo R Zonoun

Individuals who contributed actively in the development of this standard throughout its elaboration were:

Juan Bulnes Ron Crane Dane Elliot Alan Flatman Maris Graube Guy Harkins Dean Lindsay Then. T. Liu Robert Moles Tony Lauck Joseph St. Amand Rich Seifert Nathan Tobol Mark Townsend Roger Van Brunt Bo Vicklund Chris Wargo Richard Williams Ron Yara

The ECMA TC24 Committee on Communication Protocols also provided helpful input in the development of this standard.

The IEEE 802.3 Working Group acknowledges and appreciates that many concepts embodied in this standard are based largely upon the CSMA/CD access method earlier described in *The Ethernet* specification as written jointly by individuals from Xerox Corporation, Digital Equipment Corporation, and Intel Corporation. Appreciation is also expressed to Robert M. Metcalfe and David R. Boggs for their pioneering work in establishing the original concepts.

When the IEEE Standards Board approved this standard on June 23, 1983, it had the following membership:

# James H. Beall, Chairman Edward Chelotti, Vice Chairman

# Sava I. Sherr, Secretary

J. J. Archambault John T. Boettger J. V. Bonucchi Rene Castenschiold Edward J. Cohen Len S. Corey Donald C. Fleckenstein Jay Forster

Donald N. Heirman Irvin N. Howell, Jr Joseph L. Koepfinger\* Irving Kolodny George Konomos R. F. Lawrence John E. May Donald T. Michael\* John P. Riganati Frank L. Rose Robert W. Seelbach Jay A. Stewart Clifford O. Swanson Robert E. Weiler W. B. Wilkens Charles J. Wylie

<sup>\*</sup>Member emeritus

# Contents

| SECTION                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                        |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|

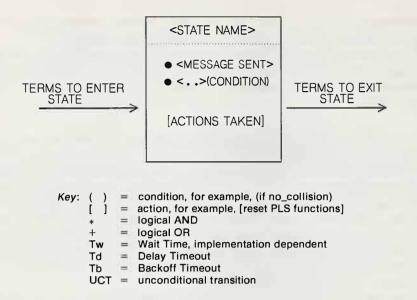

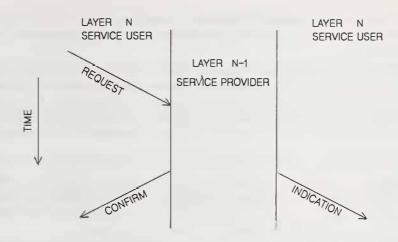

| 1. Introduction 1.1 Overview 1.1.1 Basic Concepts 1.1.2 Architectural Perspectives 1.1.3 Layer Interfaces 1.1.4 Application Areas 1.2 Notation 1.2.1 State Diagram Conventions 1.2.2 Service Specification Method and Notation 1.2.3 Physical Layer and Media Notation 1.2.4 Physical Layer Message Notation 1.3 References                                                        | . 13<br>. 13<br>. 15<br>. 15<br>. 16<br>. 16<br>. 18<br>. 18                                                           |  |

| 2. MAC Service Specification 2.1 Scope and Field of Application 2.2 Overview of the Service 2.2.1 General Description of Services Provided by the Layer 2.2.2 Model Used for the Service Specification 2.2.3 Overview of Interactions 2.2.4 Basic Services and Options 2.3 Detailed Service Specification 2.3.1 MA_DATA.request 2.3.2 MA_DATA.confirm 2.3.3 MA_DATA.indication     | . 20<br>. 20<br>. 20<br>. 21<br>. 21<br>. 21<br>. 21<br>. 21                                                           |  |

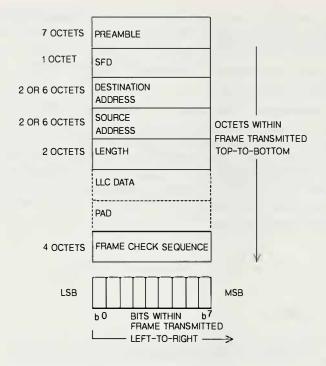

| 3. Media Access Control Frame Structure 3.1 Overview 3.1.1 MAC Frame Format 3.2 Elements of the MAC Frame 3.2.1 Preamble Field 3.2.2 Start Frame Delimiter Field 3.2.3 Address Fields 3.2.4 Destination Address Field 3.2.5 Source Address Field 3.2.6 Length Field 3.2.7 Data and PAD Fields 3.2.8 Frame Check Sequence Field 3.3 Order of Bit Transmission 3.4 Invalid MAC Frame | <ul> <li>23</li> <li>24</li> <li>24</li> <li>24</li> <li>26</li> <li>26</li> <li>26</li> <li>27</li> <li>27</li> </ul> |  |

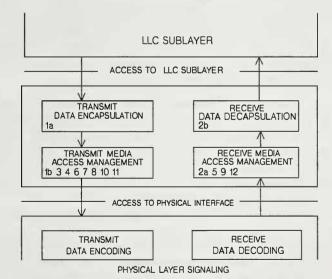

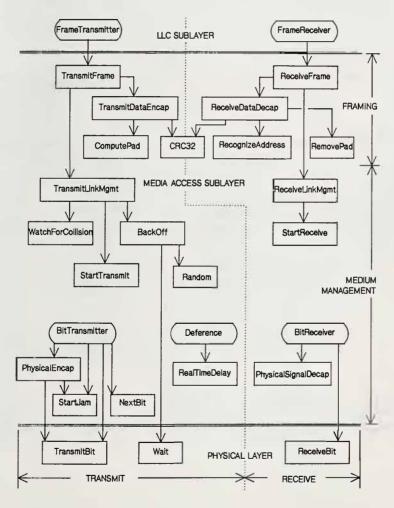

| 4. Media Access Control Method . 4.1 Functional Model of the Media Access Control Method                                                                                                                                                                                                                                                                                           | . 28<br>. 28                                                                                                           |  |

| SECTION |                                                                                                                                                                                                  | PAGE |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

|         | <ul> <li>4.1.3 Relationships to LLC Sublayer and Physical Layer</li> <li>4.1.4 CSMA/CD Access Method Functional Capabilities</li> <li>4.2 CSMA/CD Media Access Control Method: Formal</li> </ul> | . 32 |  |

|         | Specification                                                                                                                                                                                    | . 32 |  |

|         | 4.2.1 Introduction                                                                                                                                                                               |      |  |

|         | 4.2.2 Overview of the Procedural Model                                                                                                                                                           |      |  |

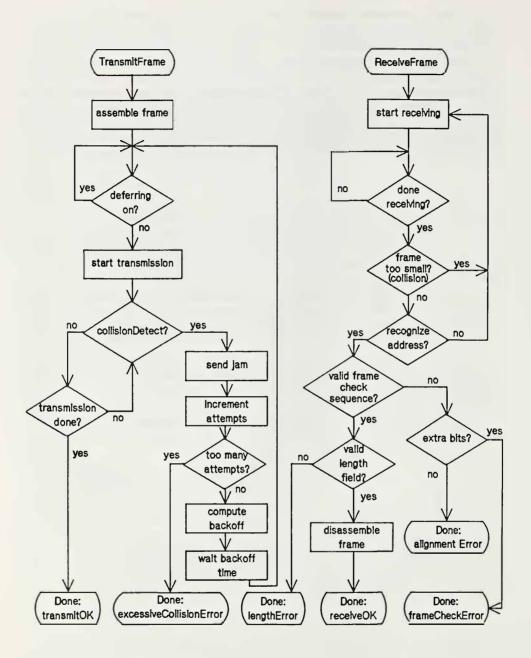

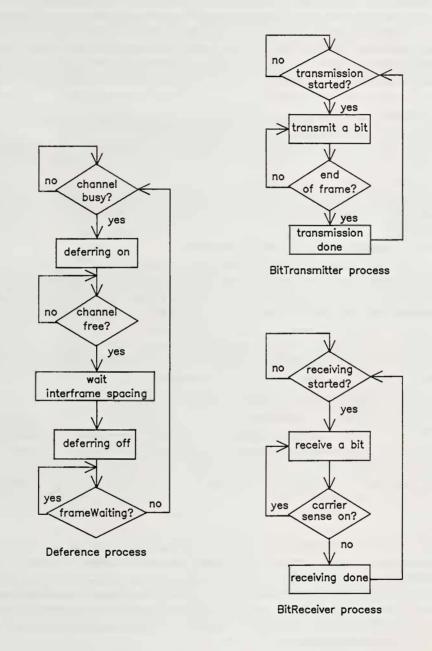

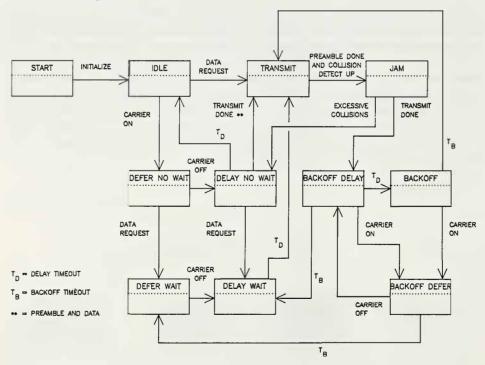

|         | 4.2.3 Frame Transmission Model                                                                                                                                                                   |      |  |

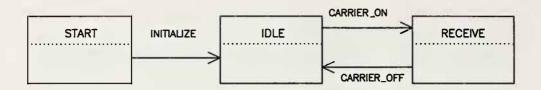

|         | 4.2.4 Frame Reception Model                                                                                                                                                                      |      |  |

|         | 4.2.5 Preamble Generation                                                                                                                                                                        |      |  |

|         | 4.2.6 Start Frame Sequence                                                                                                                                                                       |      |  |

|         | 4.2.7 Global Declarations                                                                                                                                                                        |      |  |

|         | 4.2.8 Frame Transmission                                                                                                                                                                         |      |  |

|         | 4.2.9 Frame Reception                                                                                                                                                                            |      |  |

|         | 4.2.10 Common Procedures                                                                                                                                                                         |      |  |

|         | 4.3 Interfaces to/from Adjacent Layers                                                                                                                                                           |      |  |

|         | 4.3.1 Overview                                                                                                                                                                                   |      |  |

|         | 4.3.3 Services Required from the Physical Layer                                                                                                                                                  |      |  |

|         | 4.4 Specific Implementations                                                                                                                                                                     |      |  |

|         | 4.4.1 Compatibility Overview                                                                                                                                                                     |      |  |

|         | 4.4.2 Allowable Implementations                                                                                                                                                                  |      |  |

| _       |                                                                                                                                                                                                  |      |  |

| 5.      | Network Management                                                                                                                                                                               | . 57 |  |

| 6.      | PLS Service Specifications                                                                                                                                                                       |      |  |

|         | 6.1 Scope and Field of Application                                                                                                                                                               |      |  |

|         | 6.2 Overview of the Service                                                                                                                                                                      |      |  |

|         | 6.2.1 General Description of Services Provided by the Layer                                                                                                                                      |      |  |

|         | 6.2.2 Model Used for the Service Specification                                                                                                                                                   |      |  |

|         | 6.2.3 Overview of Interactions                                                                                                                                                                   |      |  |

|         | 6.2.4 Basic Services and Options                                                                                                                                                                 | . 58 |  |

|         | 6.3 Detailed Service Specification                                                                                                                                                               |      |  |

|         | 6.3.1 Peer-To-Peer Service Primitives                                                                                                                                                            |      |  |

|         | 6.3.2 Sublayer-To-Sublayer Service Primitives                                                                                                                                                    | . 60 |  |

| 7.      | Physical Signaling (PLS) and Attachment Unit Interface (AUI)                                                                                                                                     |      |  |

|         | Specifications                                                                                                                                                                                   | . 61 |  |

|         | 7.1 Scope                                                                                                                                                                                        | . 61 |  |

|         | 7.1.1 Definitions                                                                                                                                                                                | . 62 |  |

|         | 7.1.2 Summary of Major Concepts                                                                                                                                                                  |      |  |

|         | 7.1.3 Application                                                                                                                                                                                |      |  |

|         | 7.1.4 Modes of Operation                                                                                                                                                                         |      |  |

|         | 7.1.5 Allocation of Function                                                                                                                                                                     |      |  |

|         | 7.2 Functional Specification                                                                                                                                                                     |      |  |

|         | 7.2.1 PLS-PMA (DTE-MAU) Interface Protocol                                                                                                                                                       | . 63 |  |

| SE | CTION                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PAGE         |

|----|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|    | 7.2.2                          | PLS Interface to MAC and Management Entities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 69           |

|    | 7.2.3                          | Frame Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

|    | 7.2.4                          | PLS Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |

|    | 7.3 Signa                      | al Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80           |

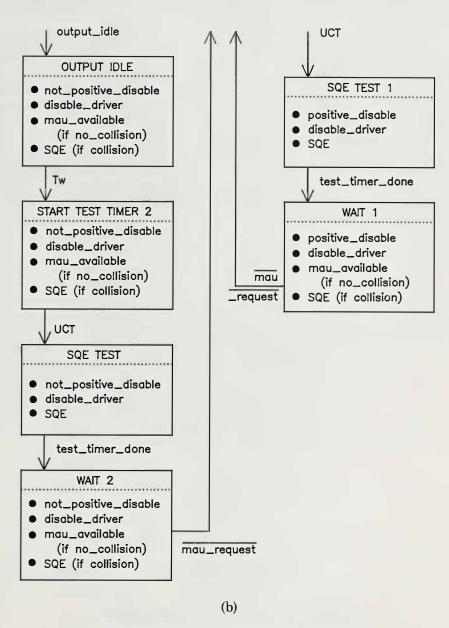

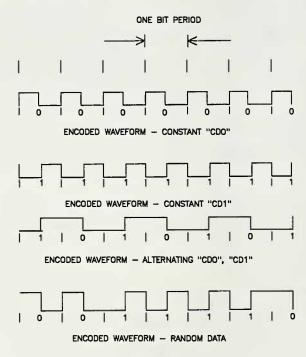

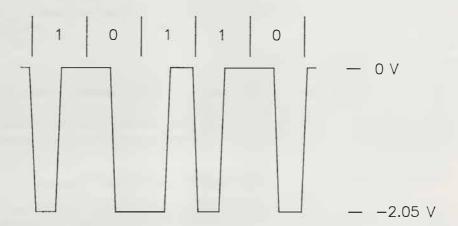

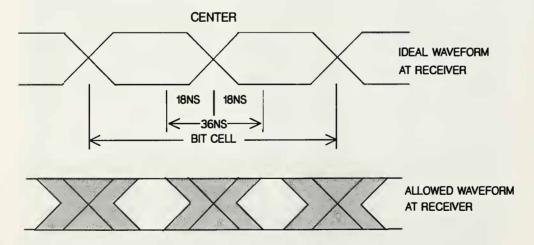

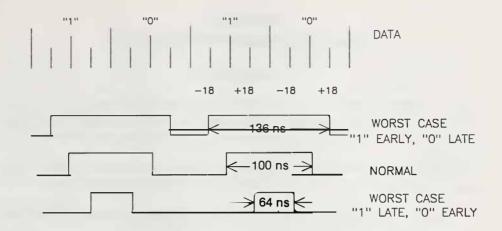

|    | 7.3.1                          | Signal Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80           |

|    | 7.3.2                          | Signaling Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 82           |

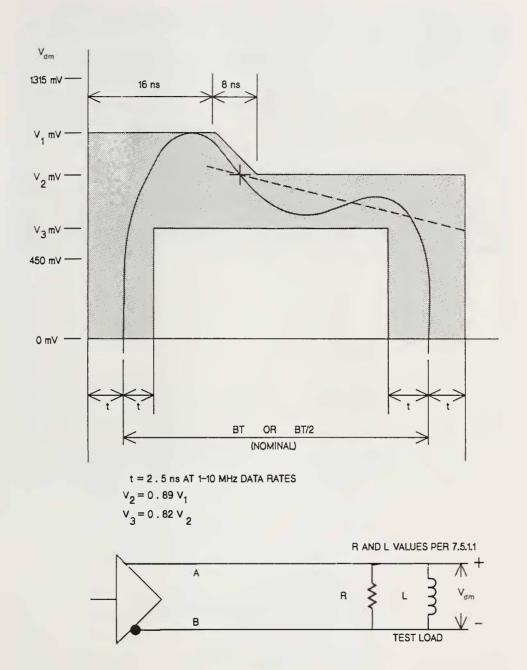

|    | 7.3.3                          | Signaling Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82           |

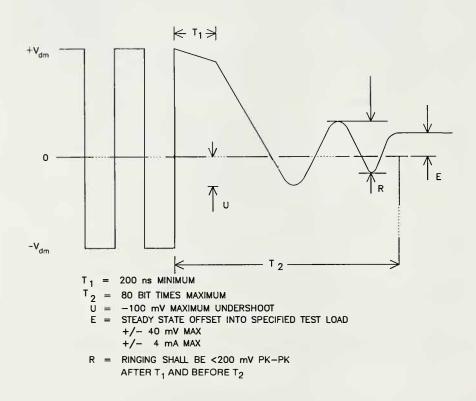

|    | 7.4 Electr                     | rical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 82           |

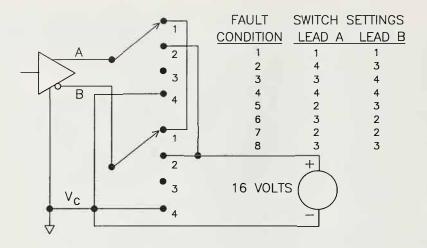

|    | 7.4.1                          | Driver Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 82           |

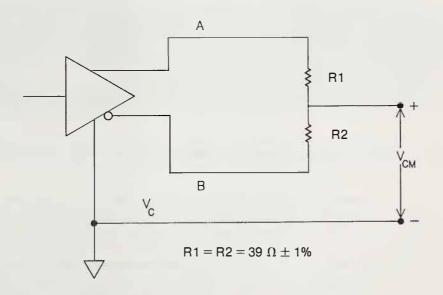

|    | 7.4.2                          | Receiver Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 86           |

|    | 7.4.3                          | AUI Cable Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 88           |

|    | 7.5 Funct                      | tional Description of Interchange Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 90         |

|    | 7.5.1                          | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 90           |

|    | 7.5.2                          | Definition of Interchange Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 90         |

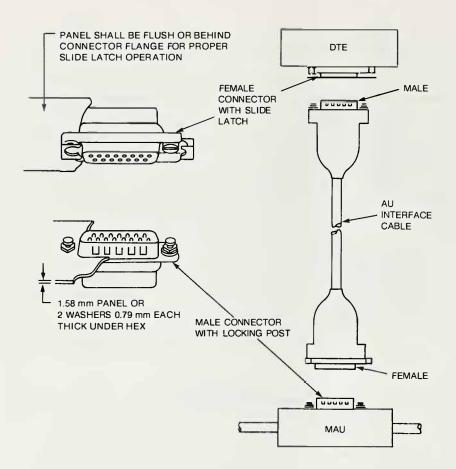

|    | 7.6 Mecha                      | anical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 92         |

|    | 7.6.1                          | Definition of Mechanical Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 92         |

|    | 7.6.2                          | Line Interface Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 94         |

|    | 7.6.3                          | Connector Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 95         |

| 8. | Type 10B<br>8.1 Scope<br>8.1.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 99<br>. 95 |

|    | 8.1.2                          | Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

|    | 8.1.3                          | Principal Indiana Indian |              |

|    |                                | Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |

|    | 8.2.1                          | MAU Physical Layer Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |

|    | 8.2.2                          | MAU Interface Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |

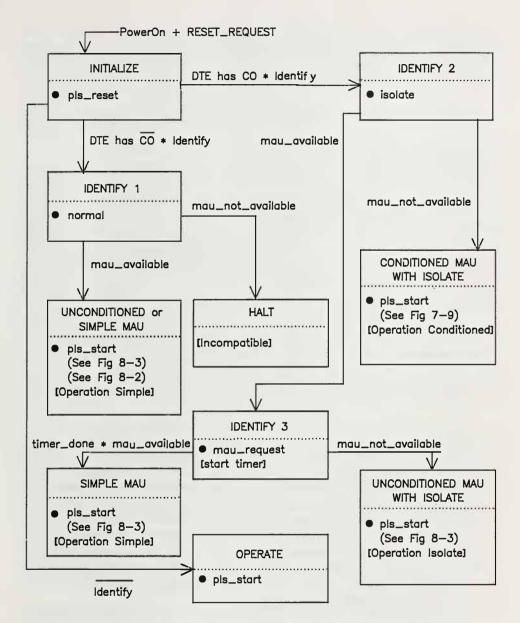

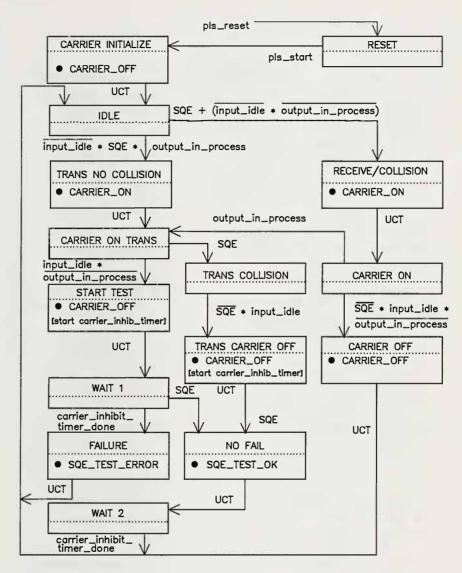

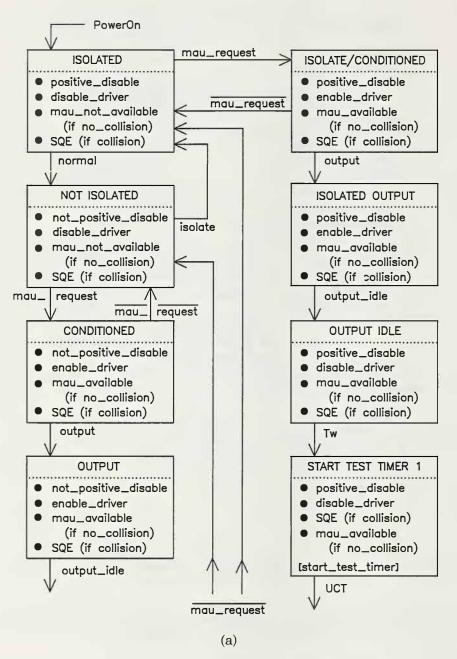

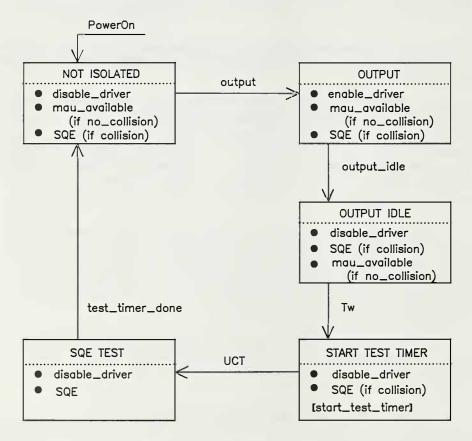

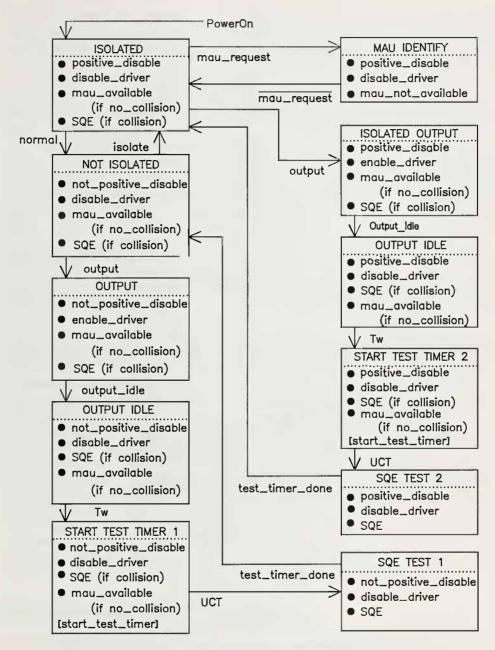

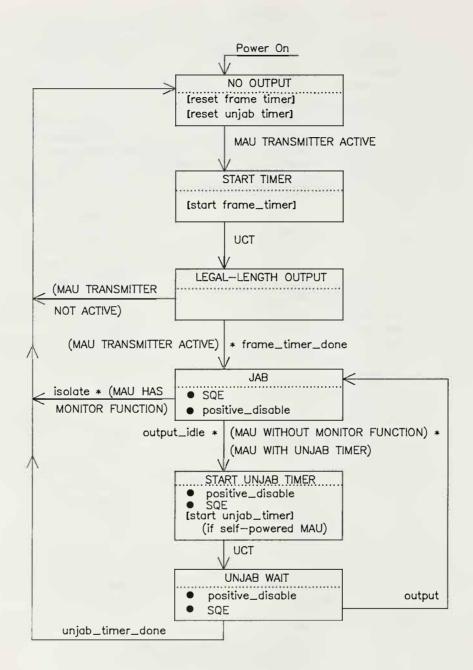

|    | 8.2.3                          | MAU State Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

|    |                                | -Medium Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

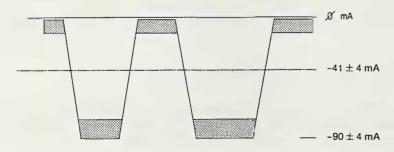

|    | 8.3.1                          | MAU-to-Coaxial Cable Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

|    | 8.3.2                          | MAU Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

|    | 8.3.3                          | MAU-DTE Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

|    | 8.3.4                          | MAU-DTE Mechanical Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |

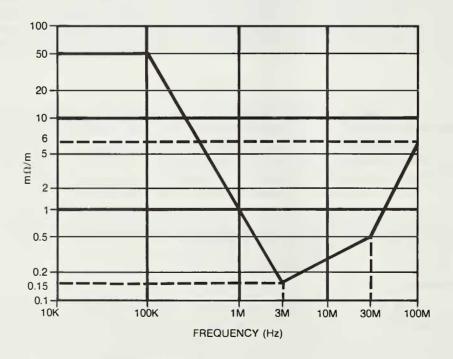

|    |                                | acteristics of the Coaxial Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |

|    | 8.4.1                          | Comment Charle Electrical - aranicolor (111111111111111111111111111111111111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |

|    | 8.4.2                          | Coaxial Cable Physical Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |

|    | 8.4.3                          | Total Segment dc Loop Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |

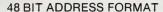

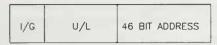

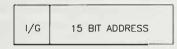

|    |                                | al Trunk Cable Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |