### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

UMI

University Microfilms International A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600

Order Number 1345319

Architectural, numerical and implementation issues in the VLSI design of an integrated CORDIC-SVD processor

Kota, Kishore, M.S. Rice University, 1991

| Page 4  | of 106 |

|---------|--------|

| I ago T | 01 100 |

--

### RICE UNIVERSITY

## Architectural, Numerical and Implementation Issues in the VLSI Design of an Integrated CORDIC-SVD Processor

by

### Kishore Kota

A THESIS SUBMITTED

IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE

Master of Science

APPROVED, THESIS COMMITTEE:

Dr. Joseph R. Cavallaro, Chairman

Assistant Professor

Electrical and Computer Engineering

Dr John K. Bennett,

Assistant Professor

Electrical and Computer Engineering

Dr. Peter J. Varman

Associate Professor

Electrical and Computer Engineering

Houston, Texas

April, 1991

# Architectural, Numerical and Implementation Issues in the VLSI Design of an Integrated CORDIC-SVD Processor

### Kishore Kota

### Abstract

This thesis describes the design of a systolic array for computing the Singular Value Decomposition (SVD) based on the Brent, Luk, Van Loan array. The use of COordinate Rotation DIgital Computer (CORDIC) arithmetic results in an efficient VLSI implementation of the processor that forms the basic unit of the array. A six-chip custom VLSI chip set for the processor was initially designed, fabricated in a  $2.0\mu$  CMOS n-well process, and tested. The CORDIC Array Process Element (CAPE), a single chip implementation, incorporates several enhancements based on a detailed error analysis of fixed-point CORDIC. The analysis indicates a need to normalize input values for inverse tangent computations. This scheme was implemented using a novel method that has  $O(n^{1.5})$  hardware complexity. Use of previous techniques to implement such a normalization would require  $O(n^2)$  hardware. Enhanced architectures, which reduce idle time in the array either through pipelining or by improving on a broadcast technique, are also presented.

## Acknowledgments

Special thanks are due to Dr. Joe Cavallaro for being the motivation and a constant driving force behind this work. I am especially thankful to him for being a good friend and just being there when I needed him most. I would also like to thank Dr. John Bennett and Dr. Peter Varman for serving on the committee and having the patience to deal with me.

My friend and constant companion " $\Psi \chi o$ " Hemkumar deserves special praise for all those enlightening discussions and valuable comments, which on more than one occasion prevented me from taking the wrong decisions. Thanks are due to my roommate, Raghu, for his constant, but often futile efforts at waking me up. But for him I would have slept through the entire semester without a care. Thanks to the Common Pool for allowing me to work through even the most difficult times without compromising on the food. Special thanks to my office-mates Jay Greenwood and Jim Carson. The office would not be half as lively without them.

Finally I am eternally indebted to my mother and father. Even when they are halfway across the world, nothing is possible without their blessings.

To my Grandfather, For his one statement that has been the driving force through the years: "... hope for the best, but be prepared for the worst ... "

# Contents

|   | Abs  | stract                                | i   |

|---|------|---------------------------------------|-----|

|   | Ack  | nowledgments                          | iii |

|   | List | of Tables                             | vii |

|   | List | of Illustrations                      | ix  |

| 1 | Int  | roduction                             | 1   |

|   | 1.1  | Systolic Arrays for SVD               | 2   |

|   | 1.2  | Contributions of the thesis           | 3   |

|   | 1.3  | Overview of the thesis                | 3   |

| 2 | sv   | D Array Architecture                  | 5   |

|   | 2.1  | Introduction                          | 5   |

|   | 2.2  | The SVD-Jacobi Method                 | 6   |

|   | 2.3  | Direct 2-Angle Method                 | 8   |

|   | 2.4  | Architecture for $2 \times 2$ SVD     | 12  |

| 3 | CC   | RDIC Techniques                       | 14  |

|   | 3.1  | Introduction                          | 14  |

|   | 3.2  | CORDIC Algorithms                     | 15  |

|   | 3.3  | CORDIC Operation in the Circular Mode | 16  |

|   |      | 3.3.1 CORDIC Z-Reduction              | 19  |

| ** | : |

|----|---|

| v  | 1 |

|   |     | 3.3.2  | CORDIC Y-Reduction                           | 2  |

|---|-----|--------|----------------------------------------------|----|

|   |     | 3.3.3  | Modified Y-Reduction for the SVD processor   | 2  |

|   | 3.4 | Scale  | Factor Correction                            | 2  |

|   | 3.5 | Error  | Analysis of CORDIC Iterations                | 2  |

|   | 3.6 | Error  | Analysis of CORDIC Z-Reduction               | 2  |

|   |     | 3.6.1  | Error Introduced by X and Y Iterations       | 2  |

|   |     | 3.6.2  | Error Introduced by Z Iterations             | 2  |

|   |     | 3.6.3  | Effects of perturbations in $\theta$         | 2  |

|   | 3.7 | Error  | Analysis of CORDIC Y-Reduction               | 3  |

|   |     | 3.7.1  | Error Introduced by X and Y Iterations       | 3  |

|   |     | 3.7.2  | Error Introduced by Z Iterations             | 3  |

|   |     | 3.7.3  | Perturbation in the Inverse Tangent          | 3  |

|   | 3.8 | Norm   | alization for CORDIC Y-Reduction             | 33 |

|   |     | 3.8.1  | Single Cycle Normalization                   | 35 |

|   |     | 3.8.2  | Partial Normalization                        | 36 |

|   |     | 3.8.3  | Choice of a Minimal Set of Shifts            | 39 |

|   |     | 3.8.4  | Cost of Partial Normalization Implementation | 43 |

|   | 3.9 | Summ   | nary                                         | 43 |

|   | 1   | ~~     |                                              |    |

| 4 | Th  |        | RDIC-SVD Processor Architecture              | 46 |

|   | 4.1 | Introd | uction                                       | 46 |

|   | 4.2 | Archit | ecture of the Prototype                      | 46 |

|   |     | 4.2.1  | Design of the XY-Chip                        | 48 |

|   |     | 4.2.2  | Design of the Z-Chip                         | 50 |

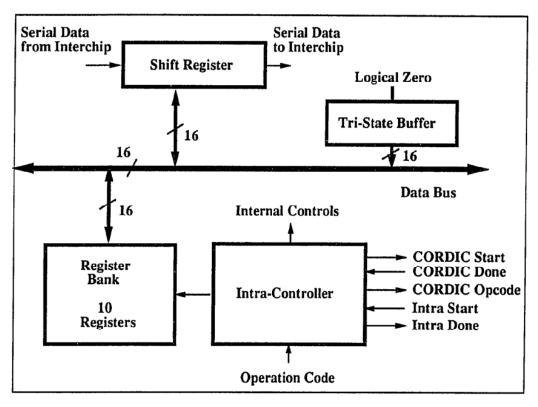

|   |     | 4.2.3  | Design of the Intra-Chip                     | 50 |

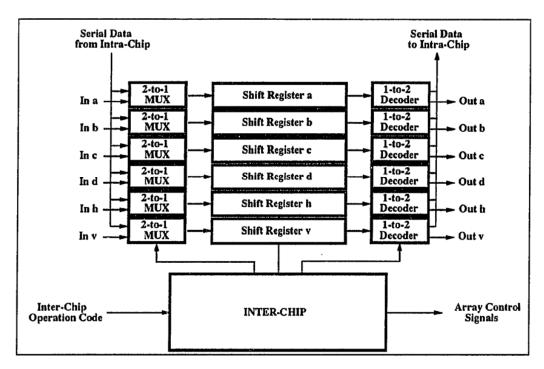

|   |     | 4.2.4  | Design of the Inter-Chip                     | 54 |

|   |                        |                                                 | vii |

|---|------------------------|-------------------------------------------------|-----|

|   | 4.3                    | The CORDIC Array Processor Element              | 55  |

|   | 4.4                    | Issues in Loading the Array                     | 60  |

|   |                        | 4.4.1 Data Loading in CAPE                      | 61  |

| 5 | Ar                     | chitectures to Improve Processor Utilization    | 64  |

|   | 5.1                    | Introduction                                    | 64  |

|   | 5.2                    | Architecture for Systolic Starting              | 65  |

|   | 5.3                    | Architecture for fast SVD                       | 70  |

|   | 5.4                    | Architecture for Collection of U and V Matrices | 73  |

| 6 | $\mathbf{V}\mathbf{L}$ | SI Implementation Issues                        | 75  |

|   | 6.1                    | Design Methodology                              | 75  |

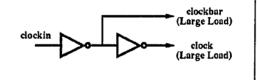

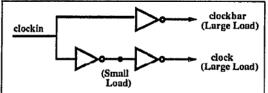

|   | 6.2                    | Reducing Skews in Control Signals               | 78  |

|   | 6.3                    | Design of an Adder                              | 79  |

|   | 6.4                    | Testing                                         | 80  |

| 7 | Co                     | nclusions                                       | 85  |

|   | 7.1                    | Summary                                         | 85  |

|   | 7.2                    | Future Work                                     | 87  |

|   | Dil                    | liography                                       | 22  |

# Tables

| 2.1 | Parallel Ordering                                                 | 8  |

|-----|-------------------------------------------------------------------|----|

| 3.1 | CORDIC Functionality in the Circular Mode                         | 19 |

| 3.2 | Total Shifts Using a Novel Normalization Scheme                   | 41 |

| 3.3 | Summary and Comparison of Error Analysis                          | 44 |

|     |                                                                   |    |

| 6.1 | A list of some of the problems in the 6-chip prototype            | 81 |

| 6.2 | Breakdown of clock cycles for the various sub-tasks in the 6-chip |    |

|     | prototype                                                         | 83 |

| 6.3 | Breakdown of clock cycles for the various sub-tasks in CAPE       | 83 |

# Illustrations

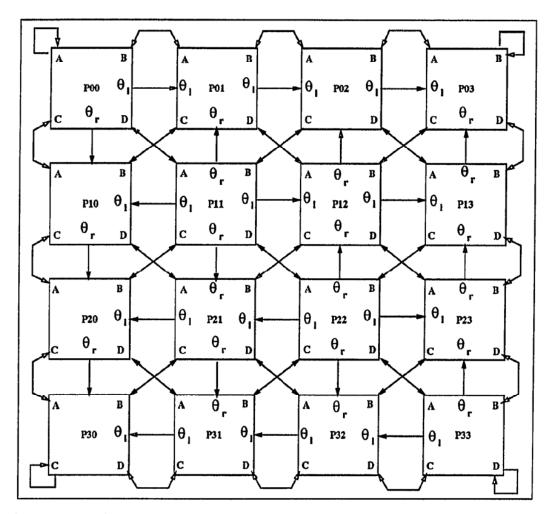

| 2.1 | The Brent-Luk-Van Loan SVD Array                           | 9  |

|-----|------------------------------------------------------------|----|

| 2.2 | Snapshots of Brent-Luk-Van Loan SVD Array                  | 11 |

|     |                                                            |    |

| 3.1 | Rotation of a vector                                       | 17 |

| 3.2 | Implementation of the CORDIC Iterations in Hardware        | 18 |

| 3.3 | Rotation of a vector in Y-Reduction                        | 21 |

| 3.4 | Error in Y-Reduction Without Normalization                 | 34 |

| 3.5 | Algorithm to Invoke Modified CORDIC Iterations             | 40 |

| 3.6 | Implementation of the CORDIC Iterations in Hardware        | 41 |

| 3.7 | Error in Y-Reduction With Partial Normalization            | 42 |

|     |                                                            |    |

| 4.1 | Block Diagram of the 6-chip Prototype CORDIC-SVD Processor | 47 |

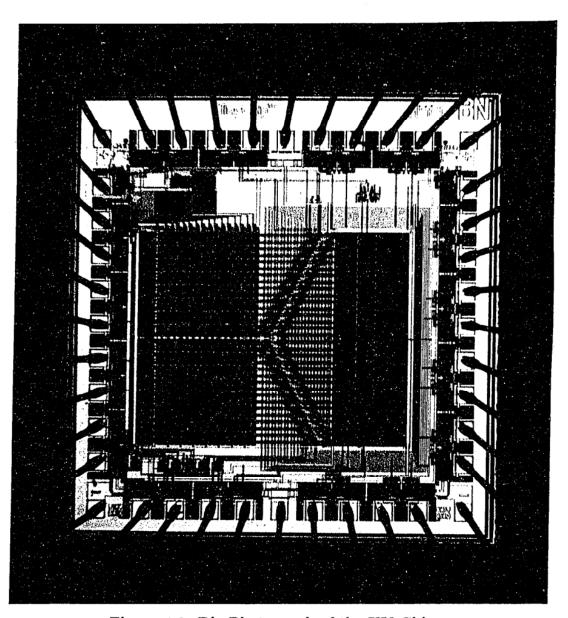

| 4.2 | Die Photograph of the XY-Chip                              | 49 |

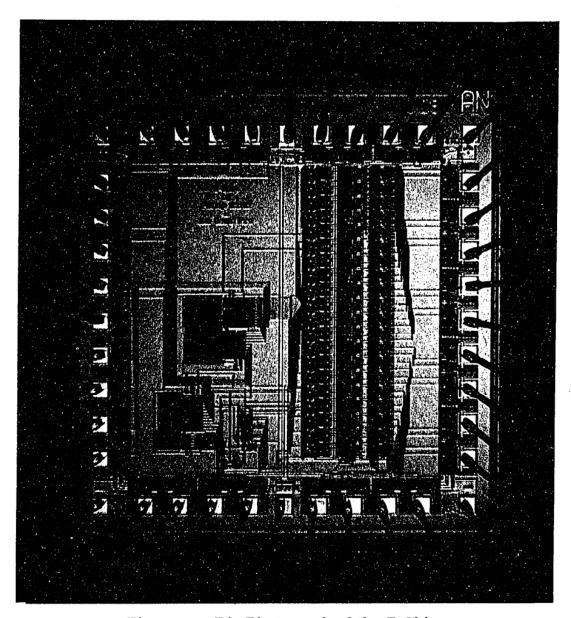

| 4.3 | Die Photograph of the Z-Chip                               | 51 |

| 4.4 | Block Diagram of the Intra-Chip                            | 52 |

| 4.5 | Die Photograph of the Intra-Chip                           | 53 |

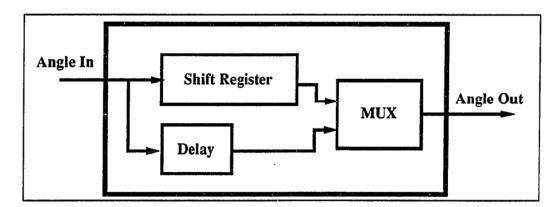

| 4.6 | Block Diagram of Inter-Chip                                | 55 |

| 4.7 | Die Photograph of the Inter-Chip                           | 56 |

| 4.8 | Internal Architecture of CAPE                              | 58 |

| ٦ | , |

|---|---|

| 2 | ι |

|   |   |

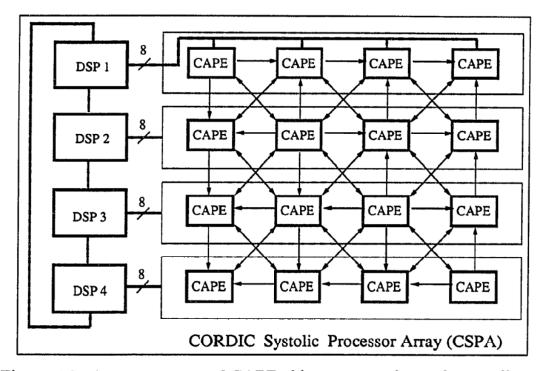

| 4.9 | A Combined DSP-VLSI Array for Robotics                   | 62 |

|-----|----------------------------------------------------------|----|

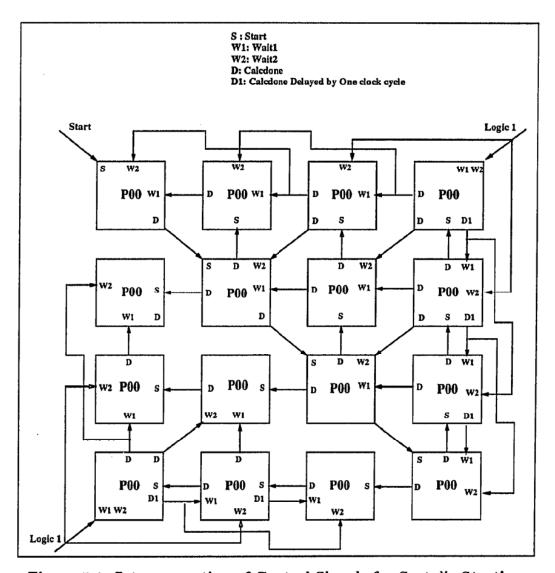

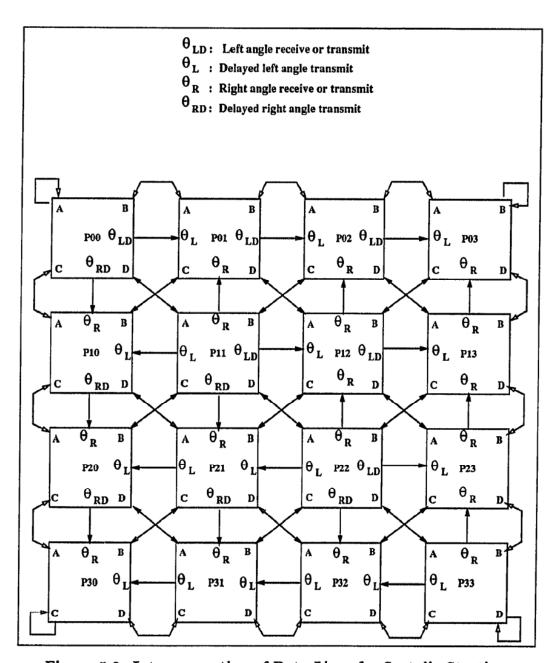

| 5.1 | Interconnection of Control Signals for Systolic Starting | 66 |

| 5.2 | Interconnection of Data Lines for Systolic Starting      | 67 |

| 5.3 | Snapshots of a Systolic Starting scheme                  | 69 |

| 5.4 | Hardware Required for Fast SVD                           | 71 |

| 5.5 | Snapshots of an Array Computing $U$ and $V$              | 73 |

| 6.1 | Plot of the completed Single Chip Implementation         | 77 |

| 6.2 | Clock Generation with Large Skew                         | 78 |

| 6.3 | Clock Generation with Small Skew                         | 78 |

## Chapter 1

## Introduction

Rapid advances made in VLSI and WSI technologies have led the way to an entirely different approach to computer design for real-time applications, using special-purpose architectures with custom chips. By migrating some of the highly compute-intensive tasks to special-purpose hardware, performance which is typically in the realm of supercomputers, can be obtained at only a fraction of the cost. High-level Computer-Aided Design (CAD) tools for VLSI silicon compilation, allow fast prototyping of custom processors by reducing the tedium of VLSI design. Special-purpose architectures are not burdened by the problems associated with general computers and can map the algorithmic needs of a problem to hardware. Extensive parallelism, pipelining and use of special arithmetic techniques tailored for the specific application lead to designs very different from conventional computers.

Systolic and wavefront arrays form a class of special-purpose architectures that hold considerable promise for real-time computations. Systolic arrays are characterized by "multiple use of each data item, extensive concurrency, a few types of simple cells and a simple and regular data and control flow between neighbors" [21]. Systolic arrays typically consist of only a few types of simple processors, allowing easy prototyping. The near-neighbor communication associated with systolic arrays results in short interconnections that allow higher operating speeds even in large arrays. Thus, systolic arrays offer the potential for scaling to very large arrays. Numerical problems

involving large matrices benefit from this property of systolic arrays.

Many real-time signal processing, image processing and robotics applications require fast computations involving large matrices. The high throughput required in these applications can in general, be obtained only through special-purpose architectures. A computationally complex numerical problem, which has evoked a lot of interest is the Singular Value Decomposition (SVD) [15]. It is generally acknowledged that the SVD is the only generally reliable method for determining the rank of a matrix numerically. Solutions to the complex problems encountered in real-time processing, which use the SVD, exhibit a high degree of numerical stability. SVD techniques handle rank deficiency and ill-conditioning of matrices elegantly, obviating the need for special handling of these cases. The SVD is a very useful tool, for example, in analyzing data matrices from sensor arrays for adaptive beamforming [30], and low rank approximations to matrices in image enhancement [2]. The wide variety of applications for the SVD coupled with its computational complexity justify dedicating hardware to this computation.

## 1.1 Systolic Arrays for SVD

The SVD problem has evoked a lot of attention in the past decade. Numerous architectures and algorithms were proposed for computing the SVD in an efficient manner. The Hestenes' method using Jacobi transformations has been a popular choice among researchers, due to the concurrency it allows in the computation of the SVD. Numerous algorithms and architectures for the SVD were proposed by Luk [24, 26, 25, 23]. Brent, Luk and Van Loan [5] presented an expandable square array of simple processors to compute the SVD. A processor architecture for the Brent, Luk and Van Loan array, using CORDIC techniques, was presented by Cavallaro [8].

#### 1.2 Contributions of the thesis

A detailed study of the numerical accuracy of fixed-point CORDIC modules is provided in this thesis. This analysis indicates a need to normalize the values for CORDIC Y-reduction in order to achieve meaningful results. A novel normalization scheme for fixed-point CORDIC Y-reduction that reduces the hardware complexity is developed.

This thesis is chiefly concerned with the issues relating to the VLSI implementation of the CORDIC-SVD array proposed by Cavallaro. Many of the lower-level architectural issues that are not relevant at the higher levels assume a new significance when trying to implement the array. Elegant solutions have been found for all the problems encountered in the design process.

An integrated VLSI chip to implement the  $2 \times 2$  SVD processor element, which serves as the basic unit of the SVD array, has been designed. A new internal architecture has been developed within the constraints imposed by VLSI.

Numerous array architectures that improve on the previous architectures were developed as part of this research. These schemes can used in future implementations as improvements to the current design.

#### 1.3 Overview of the thesis

Chapter 2 presents the SVD algorithm and the array proposed by Brent, Luk and Van Loan [5]. A discussion of the CORDIC-SVD processor is also provided. Chapter 3 reviews the CORDIC arithmetic technique and then presents an improved analysis of the numerical accuracy of fixed-point CORDIC. Chapter 4 presents the improvements made to the architecture of the single chip VLSI implementation of the SVD processor over the various sub-units that constitute the prototype SVD processor. Chapter 5 presents improvements to the array architecture and the impact of these

on the processor design. These improvements include schemes for systolic starting and architectures that reduce idle time in the array, to achieve higher throughput.

## Chapter 2

## SVD Array Architecture

## 2.1 Introduction

This chapter introduces the principles that govern the efficient computation of the Singular Value Decomposition (SVD) in a parallel array. A major portion of the work in this thesis is based on the Brent, Luk and Van Loan [5] array for computing the SVD. Later sections of this chapter provide insight into the operation of this array.

The SVD has proved to be an important matrix decomposition with theoretical and practical significance. The canonical representation of a matrix provided by the SVD is very useful in determining its properties. The SVD [15] of a  $p \times p$  matrix A is defined as

$$A = U\Sigma V^T, (2.1)$$

where,

U and V are orthogonal matrices of dimension  $p \times p$ , and

$\Sigma = diag(\sigma_1, \sigma_2, \dots, \sigma_p)$  is a diagonal matrix of singular values.

The columns of U and V are called the left and the right singular vectors respectively.

The SVD is a compute intensive operation requiring  $O(p^3)$  time on a sequential computer. For example, the SVD of an  $8 \times 8$  matrix on a SUN 3/60 requires about 1 second of CPU time using LINPACK [12], a library of linear algebra routines. A typical real-time application, the inverse kinematics engine of a robot, requires the

computation of the SVD of an  $8 \times 8$  matrix every  $400\mu sec$ . This is precisely the class of applications where the use of dedicated arrays is attractive. With a square array of processors it is possible to reduce the time complexity for the SVD to  $O(p \log p)$ .

### 2.2 The SVD-Jacobi Method

The Jacobi method to compute the SVD is a popular algorithm for parallel implementation, due to the concurrency it introduces to the problem. The algorithm is based on the use of orthogonal transformations, called *Jacobi Rotations* <sup>1</sup> to selectively reduce a given matrix element to zero. A Jacobi rotation by an angle  $\theta$  in the ij plane, is a  $p \times p$  matrix,  $J(i, j, \theta)$ , where,

$$j_{aa} = 1$$

$\forall (a \neq i, j),$

$j_{ii} = \cos \theta, \quad j_{ij} = \sin \theta,$

$j_{ji} = -\sin \theta, \quad j_{jj} = \cos \theta,$

and all other  $j_{ab} = 0.$  (2.2)

Intuitively, a Jacobi rotation is an identity matrix with four of its elements replaced by a vector rotation matrix as shown below:

$$J(i,j,\theta) = \begin{bmatrix} 1 & \cdots & 0 & \cdots & 0 & \cdots & 0 \\ \vdots & \ddots & \vdots & & \vdots & & \vdots \\ 0 & \cdots & \cos\theta & \cdots & \sin\theta & \cdots & 0 \\ \vdots & & \vdots & \ddots & \vdots & & \vdots \\ 0 & \cdots & -\sin\theta & \cdots & \cos\theta & \cdots & 0 \\ \vdots & & \vdots & & \vdots & \ddots & \vdots \\ 0 & \cdots & 0 & \cdots & 0 & \cdots & 1 \end{bmatrix}$$

$$(2.3)$$

The parameters i and j select the matrix element that is to be reduced to zero, while the parameter  $\theta$  is computed using a few matrix elements. Since very few

<sup>1</sup> also called Givens Rotations or simply plane rotations

matrix elements are required to compute the entire transformation, local computation is possible by storing all the required data in the registers of a single processor. In addition, pre-multiplication with a Jacobi rotation matrix, called *left-sided rotation*, modifies only the  $i^{th}$  and  $j^{th}$  rows, while a right-sided rotation affects only the  $i^{th}$  and  $j^{th}$  columns. This introduces concurrency, since computations which use the unmodified data elements can be performed in parallel.

The SVD algorithm consists of a sequence of orthogonal <sup>2</sup> Jacobi transformations, chosen to diagonalize the given matrix. The algorithm to compute the SVD is iterative and can be written as

$$A_0 = A, (2.4)$$

$$A_{k+1} = U_k^T A_k V_k = J_k(i, j, \theta_l)^T A_k J_k(i, j, \theta_r).$$

(2.5)

Appropriate choice of the 2-sided rotations can force  $A_k$  to converge to the diagonal matrix of singular values  $\Sigma$ . The matrix of left singular vectors is obtained as a product of the left rotations  $U_k$ , while the matrix of right singular vectors is obtained as a product of the right-sided rotations. At each iteration k, a left rotation of  $\theta_l$  and a right rotation of  $\theta_l$  in the plane ij are chosen to reduce the two off-diagonal elements  $a_{ij}$  and  $a_{ji}$  of  $A_k$  to zero. A sweep consists of n(n-1)/2 iterations that reduce every pair of off-diagonal elements to zero. Several sweeps are required to actually reduce the initial matrix to a diagonal matrix. The sequence, in which the off-diagonal pairs are annihilated within each sweep is chosen apriori according to some fixed ordering. Forsythe-Henrici [14] proved that the algorithm converges for the cyclic-by-rows and cyclic-by-columns ordering. However, these orderings do not allow decoupling of successive iterations, thereby restricting the parallelism achievable. Brent and Luk [4] introduced the parallel ordering that does not suffer from this drawback.

<sup>&</sup>lt;sup>2</sup>A matrix is orthogonal when its transpose equals the inverse

```

(1,2)

(3,4)

(5,6)

(7,8)

(1,4)

(2,6)

(3,8)

(5,7)

(2,7)

(1,6)

(4,8)

(3,5)

(1,8)

(6,7)

(2,3)

(4,5)

(1,7)

(8,5)

(6,3)

(4,2)

(1,5)

(7,3)

(8,2)

(6,4)

(1,3)

(5,2)

(7,4)

(8,6)

```

Table 2.1: Parallel Ordering data exchange with 8 elements. This is the ordering used when eight chess players have to play a round-robin tournament, each player playing one game a day.

An iteration that annihilates  $a_{11}$  and  $a_{22}$  does not affect any of the terms required for annihilating  $a_{33}$  and  $a_{44}$ , allowing the two sets of rotation angles to be computed concurrently. Thus parallel ordering allows decoupling of the computation of the Jacobi transformations of all the iterations in a single row of the ordering (Table 2.1). Brent, Luk and Van Loan [5] proposed a square array of processors based on this scheme. The ordering has an additional property that it requires only near-neighbor communication in an array and is hence amenable to systolic implementation.

## 2.3 Direct 2-Angle Method

The Brent, Luk and Van Loan systolic array [5] consists of a  $p/2 \times p/2$  array of processors (Figure 2.1) to compute the SVD of a  $p \times p$  matrix. The matrix dimension, p, is assumed to be even. Each processor stores a  $2 \times 2$  submatrix and has the ability to compute the SVD of a  $2 \times 2$  matrix. The special structure of the Jacobi rotation matrix allows computing the angles for a  $p \times p$  two-sided rotation in terms of a basic  $2 \times 2$  rotation. The application of the transformation on a  $p \times p$  matrix can also be expressed as a set of  $2 \times 2$  transformations. Thus the  $2 \times 2$  SVD forms the basic step for the  $p \times p$  SVD.

Figure 2.1: The Brent-Luk-Van Loan SVD Array for Computing the SVD of an  $8\times 8$  Matrix

A  $2 \times 2$  SVD can be described as

$$R(\theta_l)^T \begin{bmatrix} a & b \\ c & d \end{bmatrix} R(\theta_r) = \begin{bmatrix} \psi_1 & 0 \\ 0 & \psi_2 \end{bmatrix}, \tag{2.6}$$

where  $\theta_l$  and  $\theta_r$  are the left and right rotation angles, respectively. The rotation matrix is

$$R(\theta) = \begin{bmatrix} \cos \theta & \sin \theta \\ -\sin \theta & \cos \theta \end{bmatrix}, \tag{2.7}$$

and the input matrix is

$$M = \begin{bmatrix} a & b \\ c & d \end{bmatrix}.$$

The angles  $\theta_l$  and  $\theta_r$  necessary to diagonalize the matrix M can be shown to be the inverse tangents of the data elements of M:

$$\theta_r + \theta_l = \tan^{-1} \left[ \frac{c+b}{d-a} \right],$$

$$\theta_r - \theta_l = \tan^{-1} \left[ \frac{c-b}{d+a} \right]$$

(2.8)

The left and right rotation angles in equation 2.5 can be computed using the equations 2.8 on a  $2 \times 2$  matrix formed by  $\begin{bmatrix} a_{ii} & a_{ij} \\ a_{ji} & a_{jj} \end{bmatrix}$ . It may be noted that the p/2 diagonal processors store precisely the matrices required for p/2 successive iterations, corresponding to a single row of parallel ordering in Table 2.1. All the transformations that annihilate the off-diagonal elements in the diagonal processors are independent and hence can be computed in parallel. An update of the entire array requires the left angles to be propagated from a diagonal processor to all the processors on the same row, and the right angle to be propagated to all the processors on the same column. This propagation is systolic. The update of the matrix is followed by a permutation of the rows and the columns of the matrix according to the parallel ordering. An 8-connected mesh is required to perform this data exchange. The permutation results in the next set of sub-matrices, required to compute the new set of angles, to be formed

Figure 2.2: Snapshots of the Brent-Luk-Van Loan SVD Array Showing Diagonal Waves of Activity

at the diagonal processors. Since the diagonal processors require data only from their diagonal neighbors, new computation can start as soon as these neighbors complete their portion of the computation. Thus, the updates of the matrix, corresponding to separate iterations in equation 2.5 are pipelined. This leads to diagonal waves of activity originating at the main diagonal and propagating outwards. This is shown in Figure 2.2. The various steps in the operation of this array are listed below:

- The p/2 diagonal processors compute the required transformation angles using the  $2 \times 2$  sub-matrix stored in them.

- Each diagonal processor propagates the left angle, which it computed, to its east and west neighbor. Similarly the right rotation angles are propagated north and south.

- The non-diagonal processors receive the left and right angles and apply the 2sided transformation to their sub-matrices. After the computation, they forward the left and right rotation angles to the processor next in the row or column.

- Processor P22 in Figure 2.1 receives its next set of data elements from processors

P11, P33, P13 and P31. Hence, it has to wait till processors P31 and P13 finish

their computations. Similarly, all the other diagonal processors need to wait

for their diagonal neighbors to complete the transformations before exchanging

data. Exchange of data in different parts of the array is staggered in time.

- After the data exchange, a new set of angles is computed by the diagonal processors and the same sequence of operations is repeated.

Each diagonal processor requires (p-1) iterations to complete a sweep. The number of sweeps required for convergence is  $O(\log p)$ . For most matrices up to a size of  $100 \times 100$ , the algorithm has been observed to converge within 10 sweeps. Since each iteration for a diagonal processor is completed in constant time, the total SVD requires  $O(p \log p)$ .

### 2.4 Architecture for $2 \times 2$ SVD

The array proposed by Brent, Luk and Van Loan was converted into an architecture suitable for VLSI implementation by Cavallaro and Luk [8]. By using CORDIC arithmetic, a simple architecture suitable for systolic implementation was developed. The basic functionality required in each processor is:

Ability to compute inverse tangents is required for the computation of the 2sided transformations from matrix data,

- Ability to perform 2-sided rotations of a  $2 \times 2$  matrix that is required when performing the transformation,

- Control to perform the parallel ordering data exchange.

CORDIC allows efficient implementation of the required arithmetic operations in hardware. Chapter 3 discusses the CORDIC algorithm in depth. The architecture of the individual processor element is discussed in Chapter 4.

## Chapter 3

## CORDIC Techniques

### 3.1 Introduction

In a special-purpose VLSI processor it is not necessary to include a general purpose Arithmetic and Logic Unit (ALU). An efficient design with optimal area and time complexity can be obtained by using special arithmetic techniques that map the desired computations to simplified hardware. The CORDIC technique allows efficient implementation of functions, like vector rotations and inverse tangents, in hardware. These constitute the principal computations in the SVD algorithm. Additional ALU operations (addition, subtraction and divide-by-2) required for the SVD are more basic operations and can reuse the adders and shifters that constitute the CORDIC modules.

The Coordinate Rotation Digital Computer (CORDIC) technique was initially developed by Volder [35] as an algorithm to solve the trignometric relationships that arise in navigation problems. Involving only a fixed sequence of additions or subtractions, and binary shifts, this scheme was used to quickly and systematically approximate the value of a trignometric function or its inverse. This algorithm was later unified for several elementary functions by Walther [36]. The algorithm has been used extensively in a number of calculators [16] to perform multiplications, divisions, to calculate square roots, to evaluate sine, cosine, tangent, arctangent, sinh, cosh, tanh, arctanh, ln and exp functions, and to convert between binary and mixed radix num-

ber systems [10].

## 3.2 CORDIC Algorithms

A variety of functions are computed in CORDIC by approximating a given angle in terms of a sequence of fixed angles. The algorithm for such an approximation is iterative and always converges in a fixed number of iterations. The basic result of CORDIC concerns the convergence of the algorithm and is discussed in depth by Walther [36]. The convergence theorem states the conditions that affect convergence and essentially gives an algorithm for such an approximation. The theorem is restated here. Walther [36] gives the proof for this theorem.

Theorem 3.1 (Convergence of CORDIC) Suppose

$$\varphi_0 \ge \varphi_1 \ge \varphi_2 \ge \cdots \ge \varphi_{n-1} > 0$$

,

is a finite sequence of real numbers such that

$$\varphi_i \le \sum_{j=i+1}^{n-1} \varphi_j + \varphi_{n-1}, \text{ for } 0 \le i \le n-1,$$

and suppose r is a real number such that

$$|r| \le \sum_{j=0}^{n-1} \varphi_j$$

If  $s_0 = 0$ , and  $s_{i+1} = s_i + \delta_i \varphi_i$ , for  $0 \le i \le n-1$ , where

$$\delta_i = \begin{cases} 1, & \text{if } r \ge s_i \\ -1, & \text{if } r < s_i, \end{cases}$$

then,

$$|r - s_k| \le \sum_{j=k}^{n-1} \varphi_j + \varphi_{n-1}$$

, for  $0 \le k \le n-1$ ,

and so in particular  $|r - s_n| < \varphi_{n-1}$ .

If  $\varphi_i$ s represent angles, the theorem provides a simple algorithm for approximating any angle r, in terms of a set of fixed angles  $\varphi_i$ , with a small error  $\varphi_{n-1}$ . The versatility of the CORDIC algorithm allows its use in several different modes: linear, circular and hyperbolic. The principal mode of interest in the CORDIC-SVD processor is the *circular* mode of CORDIC, due to its ability to compute vector rotations and inverse tangents efficiently.

## 3.3 CORDIC Operation in the Circular Mode

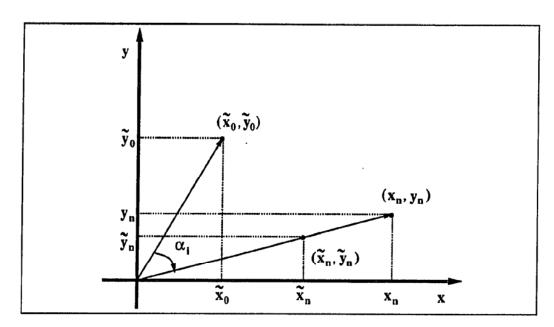

The anticlockwise rotation of a vector  $[\tilde{x}_i, \tilde{y}_i]^T$  through an angle  $\alpha_i$  (Figure 3.1) is given by

$$\begin{bmatrix} \tilde{x}_{i+1} \\ \tilde{y}_{i+1} \end{bmatrix} = \begin{bmatrix} \cos \alpha_i & \sin \alpha_i \\ -\sin \alpha_i & \cos \alpha_i \end{bmatrix} \begin{bmatrix} \tilde{x}_i \\ \tilde{y}_i \end{bmatrix}. \tag{3.1}$$

The same relation can be rewritten as

$$\begin{bmatrix} \tilde{x}_{i+1} \sec \alpha_i \\ \tilde{y}_{i+1} \sec \alpha_i \end{bmatrix} = \begin{bmatrix} 1 & \tan \alpha_i \\ -\tan \alpha_i & 1 \end{bmatrix} \begin{bmatrix} \tilde{x}_i \\ \tilde{y}_i \end{bmatrix}. \tag{3.2}$$

All computations in the circular mode of CORDIC involve a fixed number of iterations, which are similar to equation 3.2, but for a scaling,

$$x_{i+1} = x_i + \delta_i y_i \tan \alpha_i \tag{3.3}$$

$$y_{i+1} = y_i - \delta_i x_i \tan \alpha_i, \tag{3.4}$$

where  $x_i$  and  $y_i$  are states of variables x and y at the start of the  $i^{th}$  iteration,  $0 \le i < n$ , and  $\delta_i \in \{-1, +1\}$ . The values  $x_n$  and  $y_n$  are the values obtained at the end of the CORDIC iterations and differ from the desired values  $\tilde{x}_n$  and  $\tilde{y}_n$  due to a scaling as shown in Figure 3.1. Along with the x and y iterations, iterations of the form

$$z_{i+1} = z_i + \delta_i \alpha_i \tag{3.5}$$

Figure 3.1: Rotation of a vector

are performed on a variable z to store different states of an angle. The angles  $\alpha_i$  are chosen to be  $\tan^{-1}(2^{-i})$ , which reduces equation 3.3 and equation 3.4 to

$$x_{i+1} = x_i + \delta_i y_i 2^{-i} (3.6)$$

$$y_{i+1} = y_i - \delta_i x_i 2^{-i}. (3.7)$$

These iterations, called the x and the y iterations, can be implemented as simple additions or subtractions, and shifts. The angles  $\alpha_i$  are stored in a ROM, allowing the z iterations, given by equation 3.5, to be implemented as additions or subtractions. The actual hardware required to implement these iterations in hardware is shown in Figure 3.2.

Rotation of a vector through any angle  $\theta$  is achieved by decomposing the angle as a sum of  $\alpha_i$ s, using the CORDIC convergence theorem, and rotating the initial vector through this sequence of angles. Different functions are implemented by a different choice of  $\delta_i$  at each iteration. If  $\delta_i$  is chosen to force the initial  $z_0$  to 0, it

Figure 3.2: Implementation of the CORDIC Iterations in Hardware

| Operation   | Initial Values<br>for Variables                                                                       | Final values for variables                                                                                 | Functions<br>Computed                |

|-------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Z-Reduction | $x_0 = \tilde{x_0}$ $y_0 = \tilde{y_0}$ $z_0 = \theta$                                                | $x_n = (x_0 \cos \theta + y_0 \cos \theta)/K_n$ $y_n = (-x_0 \sin \theta + y_0 \cos \theta)/K_n$ $z_n = 0$ | Vector<br>Rotations,<br>sine, cosine |

| Y-Reduction | $ \begin{array}{rcl} x_0 & = & \tilde{x_0} \\ y_0 & = & \tilde{y_0} \\ z_0 & = & \theta \end{array} $ | $x_n = \sqrt{x_0^2 + y_0^2} / K_n$ $y_n = 0$ $z_n = \theta = \tan^{-1} \left( \frac{y_0}{x_0} \right)$     | Inverse<br>Tangents                  |

Table 3.1: CORDIC Functionality in the Circular Mode

is termed Rotation or Z-reduction. This is used to perform efficient vector rotations given an initial angle. A choice of  $\delta_i$ s to reduce the initial  $y_0$  to 0 is called Vectoring or Y-reduction. Iterations of this form allow the computation of the inverse tangent function. Table 3.1 summarizes the various operations performed in the CORDIC circular mode, as they pertain to the SVD processor.

#### 3.3.1 CORDIC Z-Reduction

Given an initial vector  $[\tilde{x}_0, \tilde{y}_0]^T = [x_0, y_0]^T$  and an angle  $z_0 = \theta$ , through which to rotate, the rotated vector can be obtained by rotating the initial vector through a sequence of fixed angles  $\alpha_i$  given by  $\alpha_i = \tan^{-1}(2^{-i})$ . This results in the following iterative equations

$$x_{i+1} = x_i + \delta_i y_i 2^{-i}$$

$$y_{i+1} = y_i - \delta_i x_i 2^{-i}$$

$$z_{i+1} = z_i - \delta_i \alpha_i,$$

(3.8)

where,

$$\alpha_i = \tan^{-1}(2^{-i})$$

$$\delta_i = \begin{cases} 1 & \text{if } z_i \ge 0 \\ -1 & \text{if } z_i < 0. \end{cases}$$

Each iteration for  $x_i$  and  $y_i$  corresponds to either a clockwise or an anticlockwise rotation of  $[x_i, y_i]^T$  through the angle  $\alpha_i$ , and a scaling with  $\sec(\alpha_i)$ . The CORDIC iterations for  $z_i$  correspond to a decomposition of the initial angle in terms of a set of fixed angles,  $\alpha_i$ , as given by Theorem 3.1.

After n iterations, the vector  $[x_n, y_n]^T$  is a clockwise rotation of  $[x_0, y_0]^T$  through an angle  $\theta$  and a scaling by  $1/K_n$ . Figure 3.1 illustrates  $x_n$  and  $y_n$  scaled with respect to the desired values  $\tilde{x}_n$  and  $\tilde{y}_n$ . This can be expressed as

$$\begin{bmatrix} x_n \\ y_n \end{bmatrix} = \begin{bmatrix} \cos \theta & \sin \theta \\ -\sin \theta & \cos \theta \end{bmatrix} \begin{bmatrix} x_0/K_n \\ y_0/K_n \end{bmatrix}, \tag{3.9}$$

where  $K_n$ , the constant scale factor, is given by equation 3.10,

$$K_n = \prod_{i=0}^{n-1} \cos \alpha_i. \tag{3.10}$$

This scale factor is independent of the actual  $\delta_i$ s chosen at each step, and converges to  $\approx 0.607$  for large n. A post-processing step is required to eliminate the scale factor. An algorithm for scale-factor correction is described in Section 3.4. Z-reduction can be used to compute the cosine and sine of the initial angle  $\theta$ , by choosing special cases for the initial vector  $[x_0, y_0]^T$ .

#### 3.3.2 CORDIC Y-Reduction

CORDIC is used in the Y-reduction mode for inverse tangent computations. The decomposition of an angle, according to Theorem 3.1, requires only the knowledge of the sign of the angle at that iteration and not the actual magnitude. In the

Figure 3.3: Rotation of a vector in Y-Reduction

computation of  $\tan^{-1}(y_0/x_0)$ , the same information is obtained from the y component of the vector at each iteration. As shown in Figure 3.3, if  $\theta_i > 0$ ,  $y_i > 0$  and vice versa. The function  $\tan^{-1}(y_0/x_0)$  is computed by rotating the initial vector through successively smaller angles  $\alpha_i$ , the direction of rotation at each step chosen to reduce the y-component of the vector to zero. The total angle, through which the vector has been rotated is accumulated in the z-register. The CORDIC convergence theorem forces the accumulated angle to within  $\tan^{-1}(2^{-n})$  of  $\tan^{-1}(y_0/x_0)$ . Using the initial values  $[\tilde{x}_0, \tilde{y}_0]^T = [x_0, y_0]^T$  and  $z_0 = 0$ , the following CORDIC iterations can be used to compute the value of  $\tan^{-1}(y_0/x_0)$ :

$$x_{i+1} = x_i + \delta_i y_i 2^{-i}$$

$$y_{i+1} = y_i - \delta_i x_i 2^{-i}$$

$$z_{i+1} = z_i + \delta_i \alpha_i,$$

(3.11)

where,

$$\alpha_{i} = \tan^{-1}(2^{-i}),$$

$$\delta_{i} = \begin{cases} 1 & \text{if } y_{i} \ge 0 \\ -1 & \text{if } y_{i} < 0. \end{cases}$$

(3.12)

After n iterations,  $x_n = \sqrt{x_0^2 + y_0^2}/K_n$ ,  $y_n \approx 0$  and  $z_n = \tan^{-1}(y_0/x_0)$ . If the radius  $\sqrt{x_0^2 + y_0^2}$  is desired, a scale factor correction step is necessary. The final vector  $(x_n, y_n)$  is the initial vector  $(x_0, y_0)$  rotated through  $\tan^{-1}(y_0/x_0)$  and scaled.

#### 3.3.3 Modified Y-Reduction for the SVD processor

If  $\delta_i$  is chosen according to equation 3.12, the y-reduction iterations do not converge for negative values of  $x_i$ . This restricts the initial vectors to lie in the first and fourth quadrants. This is a restriction that cannot be ensured at all steps of the SVD algorithm. Although alternate algorithms utilize the final value of  $x_n$  [38], in this SVD processor only the inverse tangent is required. This allows scaling both  $x_0$  and  $y_0$  with a constant, without affecting the computed value. Thus a simple preprocessing step [8], which negates both  $x_0$  and  $y_0$ , if  $x_0$  is negative, can be used to map the vectors from third and second quadrants to the first and fourth quadrants respectively. A different method of choosing the  $\delta_i$ s extends the convergence of the CORDIC module and hence obviates the need for this pre-processing step. This alternate choice [38] of  $\delta_i$  is given by equation 3.13,

$$\delta_i = \begin{cases} 1 & \text{if } y_i x_i \ge 0\\ -1 & \text{if } y_i x_i < 0. \end{cases}$$

$$(3.13)$$

This choice of  $\delta_i$  is implemented using a single exclusive-or gate to find the XOR of the sign-bits of  $x_i$  and  $y_i$ . This is considerably simpler than an implementation using pre-processing.

### 3.4 Scale Factor Correction

There have been numerous approaches to scale factor correction in the literature [36, 16, 1, 11]. Most approaches require special iterations of a form similar, but not identical, to the CORDIC iterations. It is important to reduce the number of these iterations to the minimum, since scale factor correction may be regarded as overhead. Most scale factor correction algorithms approximate the value of  $K_n$  as

$$\prod_{j\in J}(1-2^j),$$

where J is a set of values obtained empirically. The cardinality of the set J is typically at least n/4 and in some cases as large as n. An alternate algorithm (equation 3.14), which is more regular and hence useful for different values of n is applicable after two complete CORDIC rotations. By the end of two CORDIC rotations, the variables  $x_n$  and  $y_n$  are scaled by  $K_n^2$ . The scheme [8] to eliminate the factor of  $K_n^2$  requires only  $\lceil n/4 \rceil$  scale factor correction iterations after two CORDIC rotations of n iterations each and, hence, is cheaper than the other scale factor correction algorithms,

$$2K_n^2 = \prod_{j \in J} (1 - 2^{-2j}),\tag{3.14}$$

where  $J = \{1, 3, 5, \dots, 2\lceil n/4\rceil - 1\}$ . The scale factor iterations are given by

$$x_{i+1} = x_i - x_i 2^{-j}$$

$$y_{i+1} = y_i - y_i 2^{-j},$$

(3.15)

where,  $j = 2, 6, 10 \cdots, 4 \lceil n/4 \rceil - 2$ . At the end of these iterations, the factor of 2 in equation 3.14 is eliminated by a simple right shift.

# 3.5 Error Analysis of CORDIC Iterations

Any numerical scheme has to be resilient to truncation errors at every stage of computation in order to justify its implementation in a computer. Error analysis is the

acid test to determine whether a numerical algorithm is suitable for implementation. Many algorithms that are mathematically accurate, fail in the presence of truncation errors. While finite precision presents insurmountable problems to some algorithms, it results in only a bounded error in some others. A detailed study of these errors is necessary to interpret the results and guarantee a certain degree of accuracy.

Although CORDIC has been used previously, much of the analysis of its numerical accuracy has been ad hoc. Walther [36] claimed that a precision of n bits can be achieved if the internal representation used is  $n + \log_2 n$  bits. This analysis neglects any interaction between the various iterations and considers only the effect of the finite precision of the x and y data paths. Walther studied CORDIC for a floating-point implementation and pointed out that it is necessary to use a normalized representation to achieve this precision. Johnsson [18] attempted to obtain a closer bound on the error caused by x and y iterations, while still neglecting the interaction between the various iterations. This analysis showed that the internal representation of L bits guarantees an accuracy of n bits, if,

$$L > n + \log_2(2n - L - 3). \tag{3.16}$$

This is again  $n + \log_2 n$  bits internal representation to obtain the desired precision of n bits. Both the analyses neglect the effect of the z iterations on the the x and y iterations and  $vice\ versa$ .

A more detailed error analysis for fixed-point CORDIC modules is presented by Duryea [13]. He shows that the error for Z-reduction is bounded as:

$$|\tilde{x}_n - \hat{x}_n| \le \frac{7}{6}n2^{-t_1} + 2^{-(n-1)}$$

(3.17)

where, n is the number of iterations and  $t_1$  is the bit precision of x, y and z. In addition, he shows that the error in the computed value of inverse tangent is:

$$|\tilde{\theta}_n - \hat{\theta}_n| \le (n+1)2^{-t_1} + 2^{-(n-1)}$$

(3.18)

This error bound, however, does not account for the effect of unnormalized  $x_0$  and  $y_0$ , which is the main source of error in Y-reduction.

An exact analysis of the various errors involved in CORDIC is presented in Sections 3.6 and 3.7. For a finite number of iterations, CORDIC computes an approximate value of the desired functions even with infinite precision. Thus an error is inherently associated with the computations. This error is usually very small. Additional errors occur due to the finite-precision representation of the different variables. The analysis presented in this thesis uses the following notation to represent the different values of the variables x, y and z:

- $\hat{x}_i$ ,  $\hat{y}_i$ ,  $\hat{z}_i$  represent the actual values obtained due to CORDIC iterations, assuming finite-precision arithmetic in a real-world implementation of CORDIC,

- x<sub>i</sub>, y<sub>i</sub>, z<sub>i</sub> represent the values that will be obtained if the same CORDIC iterations that were performed in the previous case, are performed on numbers represented with infinite-precision,

- $\tilde{x}_i$ ,  $\tilde{y}_i$ ,  $\tilde{z}_i$  represent the values that should be obtained for the desired function with infinite precision, as mathematically defined.

# 3.6 Error Analysis of CORDIC Z-Reduction

Let the initial values for x, y and z be  $x_0$ ,  $y_0$ ,  $z_0 = \theta$ . Each CORDIC iteration for x and y is of the form,

$$x_{i+1} = x_i + \delta_i y_i 2^{-i}$$

$$y_{i+1} = y_i - \delta_i x_i 2^{-i}.$$

Finally after n iterations,

$$x_n = (x_0 \cos \alpha + y_0 \sin \alpha)/K_n \tag{3.19}$$

$$y_n = (y_0 \cos \alpha - x_0 \sin \alpha)/K_n, \qquad (3.20)$$

where,

$$K_n = \prod_{i=0}^{n-1} \cos \alpha_i$$

$$\alpha_i = \tan^{-1}(2^{-i})$$

$$\alpha = \sum_{i=0}^{n-1} \delta_i \alpha_i.$$

(3.21)

The sequence of  $\delta_i$ s is exactly the same as what would be obtained in a real-world implementation of CORDIC, using the same initial conditions. The angle  $\alpha$  is an approximation of  $\theta$ . Since the x and y iterations implement a rotation through  $\tan^{-1}(2^{-i})$  by shifting the variables, they achieve a rotation through exactly  $\alpha_i$ . The finite-precision representation of  $x_i$  and  $y_i$ , however, causes a truncation error in their computation. Let the actual values of  $x_i$  and  $y_i$  obtained at the end of each iteration be  $\hat{x}_i$ ,  $\hat{y}_i$ .

#### 3.6.1 Error Introduced by X and Y Iterations

Suppose x and y are represented with  $t_1$  bits and x and y are interpreted as fractions, without any loss of generality. Since the numbers are truncated after the right shift, the addition and subtraction operations result in a truncation error not exceeding  $2^{-t_1}$ . Accordingly,

$$\hat{x}_1 = x_0 + \delta_0 y_0 2^{-0} = x_1$$

$$\hat{y}_1 = y_0 + \delta_0 x_0 2^{-0} = y_1.$$

The second iteration results in a truncation error due to the right shift,

$$\hat{x}_2 = x_1 + \delta_1 y_1 2^{-1} + \mu_{x1} = x_2 + \mu_{x1}$$

$$\hat{y}_2 = y_1 + \delta_1 x_1 2^{-1} + \mu_{y1} = y_2 + \mu_{y1},$$

where,

$$|\mu_{x1}|, |\mu_{y1}| < 2^{-t_1}.$$

Using these values in the next iteration results in,

$$\hat{x}_3 = \hat{x}_2 + \delta_2 \hat{y}_2 2^{-2} + \mu_{x2}

= x_2 + \delta_2 y_2 2^{-2} + (\mu_{x1} + \mu_{y1} \delta_2 2^{-2}) + \mu_{x2}

= x_3 + (\mu_{x1} + \mu_{y1} \delta_2 2^{-2}) + \mu_{x2}.$$

Continuing this for n iterations, we obtain

$$\hat{x}_n = x_n + \epsilon_x \tag{3.22}$$

$$\hat{y}_n = y_n + \epsilon_y, \tag{3.23}$$

where,

$$\begin{aligned} |\epsilon_x|, |\epsilon_y| &< 2^{-t_1} [1 + (1 + \delta_{(n-1)} 2^{-(n-1)}) + \\ & (1 + \delta_{(n-1)} 2^{-(n-1)}) (1 + \delta_{(n-2)} 2^{-(n-2)}) + \dots + \\ & (1 + \delta_{(n-1)} 2^{-(n-1)}) (1 + \delta_{(n-2)} 2^{-(n-2)}) \dots (1 + \delta_1 2^{-1})] \\ &< 2^{-t_1} [1 + (1 + 2^{-(n-1)}) + \\ & (1 + 2^{-(n-1)}) (1 + 2^{-(n-2)}) + \dots + \\ & (1 + 2^{-(n-1)}) (1 + 2^{-(n-2)}) \dots (1 + 2^{-1})] \\ &\approx 2^{-t_1}(n). \end{aligned}$$

The upper bound is obtained by considering the maximum value for the right hand side of the above relation, which occurs when all  $\delta_i = +1$ . The sum of the product terms is approximately n. Hence, the finite precision representation of the x and y causes an error in approximately  $\log n$  bits.

### 3.6.2 Error Introduced by Z Iterations

Let  $\beta_i$  be the finite-precision approximation of  $\alpha_i$ , then assuming fixed point implementation.

$$\alpha_i = \beta_i + \mu_{2i}, \quad |\mu_{2i}| < 2^{-t_2},$$

(3.24)

where  $\beta_i$  is assumed to be represented by  $t_2$  bits. The value  $\beta_i$  is the actual value of  $\tan^{-1}(2^{-i})$  stored in the ROM. The error in representation of the angle  $\alpha_i$ , due to finite precision is  $\mu_{2i}$ .

Each iteration of CORDIC for the z variable is of the form

$$\hat{z}_{i+1} = \hat{z}_i - \delta_i \beta_i.$$

The sequence of  $\beta_i$ s satisfies the conditions required by Theorem 3.1, in spite of the errors, and hence causes the z iterations to converge. The absence of any shifting in the z iterations implies exact arithmetic, since no bits are truncated. The only deviation of  $\sum \delta_i \beta_i$  from the angle  $\theta$  is a consequence of the CORDIC approximation. Accordingly, from the convergence properties of CORDIC,

$$\hat{z}_n \leq \beta_{n-1},$$

$$\hat{z}_0 = \theta = \sum_{i=0}^{n-1} \delta_i \beta_i + \gamma, \quad |\gamma| \leq \beta_{n-1}$$

Theorem 3.1 governs the maximum error  $\gamma$  possible in this expression to be less than the smallest angle  $\beta_{n-1}$ . Coupling the finite-precision approximation error in the representation of  $\alpha_i$  with this relation, gives a bound on the deviation of the angle  $\alpha$  from the desired angle  $\theta$ . The angle  $\alpha$ , is the angle through which the vector  $[x_0, y_0]^T$  is actually rotated. Using equations 3.21 and 3.24:

$$\theta = \sum_{i=0}^{n-1} \delta_i \alpha_i - \sum_{i=0}^{n-1} \delta_i \mu_{2i} + \gamma$$

$$= \alpha - \sum_{i=0}^{n-1} \delta_i \mu_{2i} + \gamma.$$

(3.25)

Substituting the bounds on  $\gamma$  and  $\mu_{2i}$  and choosing  $\delta_i = -1$ , the error in the angle  $|\alpha - \theta|$  is,

$$|\alpha - \theta| < \beta_{n-1} + n2^{-t_2} = \tan^{-1}(2^{-(n-1)}) + n2^{-t_2} \approx 2^{-(n-1)} + n2^{-t_2}$$

(3.26)

Equation 3.26 gives the error that could be caused in the z iterations in the worst case.

#### 3.6.3Effects of perturbations in $\theta$

Combining results from equations 3.19, 3.22, 3.25, a relation can be derived between what we obtain,  $[\hat{x}_n, \hat{y}_n]^T$ , and what we expect,  $[\tilde{x}_n, \tilde{y}_n]^T$ . The expected values can be expressed in terms of exact equations as,

$$\tilde{x}_n = (x_0 \cos \theta + y_0 \sin \theta)/K_n \tag{3.27}$$

$$\tilde{y}_n = (y_0 \cos \theta - x_0 \sin \theta) / K_n. \tag{3.28}$$

Assuming that the error  $\Delta \theta = |\alpha - \theta|$  is small, the error in  $\tilde{x}_n$  and  $\tilde{y}_n$  can be obtained through differentiation as

$$\frac{\partial \tilde{x}_n}{\partial \theta} = (-x_0 \sin \theta + y_0 \cos \theta)/K_n = \tilde{y}_n/K_n \tag{3.29}$$

$$\frac{\partial \tilde{x}_n}{\partial \theta} = (-x_0 \sin \theta + y_0 \cos \theta)/K_n = \tilde{y}_n/K_n$$

$$\frac{\partial \tilde{y}_n}{\partial \theta} = (-y_0 \sin \theta - x_0 \cos \theta)/K_n = -\tilde{x}_n/K_n.$$

(3.29)

An approximation that can be made if the error in the angles is small is,

$$\Delta \tilde{x}_n \approx \frac{\partial \tilde{x}_n}{\partial \theta} \Delta \theta$$

$$\Delta \tilde{y}_n \approx \frac{\partial \tilde{y}_n}{\partial \theta} \Delta \theta.$$

Observing that the derivatives are always less than 1 yields,

$$|\tilde{x}_n - x_n| < \Delta \theta$$

$$|\tilde{y}_n - y_n| < \Delta \theta.$$

Substituting the maximum errors for  $\Delta\theta$ ,  $x_n$  and  $y_n$ , an upper bound on the actual observed error is obtained:

$$|\tilde{x}_n - \hat{x}_n|, |\tilde{y}_n - \hat{y}_n| < (\beta_{n-1} + n2^{-t_2}) + \epsilon_x$$

$< (2^{-(n-1)} + n2^{-t_2}) + (n)2^{-t_1}.$  (3.31)

This error is bounded for all values of  $|x_0|$  and  $|y_0|$ . Hence, this error can be eliminated by increasing the data-width to include extra bits as *guard* bits. The error bound obtained here is nearly the same as that given by equation 3.17. However, equation 3.31 separates the effects of the x, y iterations and the z iterations allowing a study of different components of the error.

For the prototype implementation,  $t_1 = 15$ ,  $t_2 = 15$  and n = 16. Thus the error is given by,

Observed Error

$$< (2^{-15} + (16) 2^{-15}) + (16) 2^{-15}$$

$< (33) 2^{-15}$

The error predicted by this relation is pessimistic and may never occur in practice. It is reasonable to include  $\log_2 32 = 5$  guard bits to correct the error.

# 3.7 Error Analysis of CORDIC Y-Reduction

Let the initial values for x, y and z be  $x_0$ ,  $y_0$ ,  $z_0 = 0$ . Each CORDIC iteration for x and y is of the form,

$$x_{i+1} = x_i + \delta_i y_i 2^{-i}$$

$$y_{i+1} = y_i - \delta_i x_i 2^{-i}.$$

Finally after n iterations the equations yield,

$$x_n = (x_0 \cos \alpha + y_0 \sin \alpha)/K_n \tag{3.32}$$

$$y_n = (y_0 \cos \alpha - x_0 \sin \alpha)/K_n, \tag{3.33}$$

where,

$$K_n = \prod_{i=0}^{n-1} \cos \alpha_i$$

$$\alpha_i = \tan^{-1}(2^{-i})$$

$$\alpha = \sum_{i=0}^{n-1} \delta_i \alpha_i.$$

(3.34)

The sequence of  $\delta_i$ s is exactly the same as what would be obtained in a real-world implementation of CORDIC, using the same initial conditions. The angle  $\alpha$  is an approximation of  $\theta$ , the inverse tangent accumulated in the z-variable. Since x and y iterations implement a rotation through  $\tan^{-1}(2^{-i})$  by shifting the variables, they achieve a rotation through exactly  $\alpha_i$ . The finite-precision representation of  $x_i$  and  $y_i$ , however, causes a truncation error in their computation. Let the actual values of  $x_i$  and  $y_i$  obtained at the end of each iteration be  $\hat{x}_i$ ,  $\hat{y}_i$ .

#### 3.7.1 Error Introduced by X and Y Iterations

This analysis is identical to that for Z-reduction in Section 3.6.1. The error bound is given by:

$$\hat{x}_n = x_n + \epsilon_x \tag{3.35}$$

$$\hat{y}_n = y_n + \epsilon_y \approx 0 \tag{3.36}$$

$$|\epsilon_x|, |\epsilon_y| < 2^{-t_1}(n). \tag{3.37}$$

#### 3.7.2 Error Introduced by Z Iterations

Let  $\beta_i$  be the finite-precision approximation of  $\alpha_i$ ; then assuming fixed point implementation,

$$\alpha_i = \beta_i + \mu_{2i}, \quad |\mu_{2i}| < 2^{-t_2},$$

where  $\beta_i$  is assumed to be represented by  $t_2$  bits .

Each iteration of CORDIC for the z variable is of the following form:

$$\hat{z}_{i+1} = \hat{z}_i + \delta_i \beta_i$$

$$\hat{z}_0 = 0$$

$$\hat{z}_n = \sum_{i=0}^{n-1} \delta_i \beta_i \triangleq \theta$$

$$\theta = \sum_{i=0}^{n-1} \delta_i \alpha_i - \sum_{i=0}^{n-1} \delta_i \mu_{2i}$$

$$= \alpha - \sum_{i=0}^{n-1} \delta_i \mu_{2i}.$$

(3.38)

The maximum deviation of the computed result  $\theta$ , from the angle through which the vector is rotated  $\alpha$  is given by,

$$|\alpha - \theta| < n2^{-t_2}.\tag{3.39}$$

#### 3.7.3 Perturbation in the Inverse Tangent

If x and y could be represented with infinite precision, then  $y_n$  is related to the initial values as

$$y_n = (y_0 \cos \alpha - x_0 \sin \alpha)/K_n. \tag{3.40}$$

Let r and  $\varphi$  be defined as

$$r = \sqrt{x_0^2 + y_0^2}$$

$$\tan \varphi = \frac{y_0}{x_0}.$$

Equation 3.40 can now be rewritten as:

$$K_n y_n = r \sin \varphi \cos \alpha - r \sin \alpha \cos \varphi$$

$$\frac{K_n y_n}{\sqrt{x_0^2 + y_0^2}} = \sin(\varphi - \alpha)$$

$$|\varphi - \alpha| = \sin^{-1} \left(\frac{K_n y_n}{\sqrt{x_0^2 + y_0^2}}\right)$$

$$|\varphi - \theta| < \sin^{-1} \left(\frac{K_n y_n}{\sqrt{x_0^2 + y_0^2}}\right) + \sum_{i=0}^{n-1} \delta_i \mu_{2i}.$$

Substituting all the maximum errors from Equations 3.37 and 3.39, we get,

$$|\varphi - \theta| < \frac{2nK_n2^{-t_1}}{\sqrt{x_0^2 + y_0^2}} + n2^{-t_2}.$$

(3.41)

Here,  $\varphi$  is the true inverse tangent that is to be evaluated. The final value accumulated in the z variable,  $z_n = \theta$ , is the angle actually obtained. Thus relation 3.41 gives the numerical error in inverse tangent calculations. However, this relation does not provide a constant bound for all  $x_0$  and  $y_0$ . In the worst case,  $x_0$  and  $y_0$  are close to zero, resulting in a large error.

#### 3.8 Normalization for CORDIC Y-Reduction

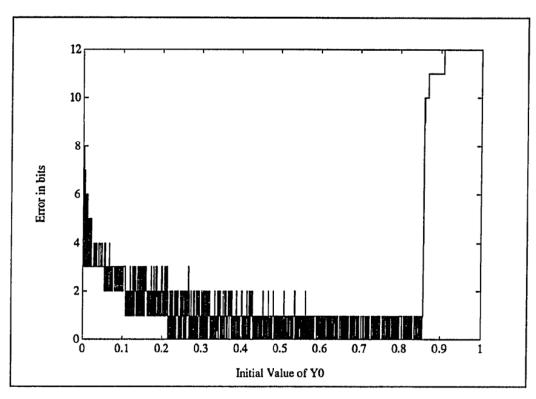

Equation 3.31 gives an upper bound on the error introduced by Z-reduction. This upper bound allows elimination of all the effects of the error by increasing the number of digits in the internal representation of the x and y. A similar upper bound does not exist for Y-reduction. This is reflected by relation 3.41, where small values of  $x_0$  and  $y_0$  result in a very large right-hand-side in the relation. Figure 3.4 shows the large errors observed in a prototype fixed-point CORDIC module when both  $x_0$  and  $y_0$  are small. An identical analysis of Y-reduction using floating-point datapaths shows that the error remains bounded for all possible inputs. Floating-point

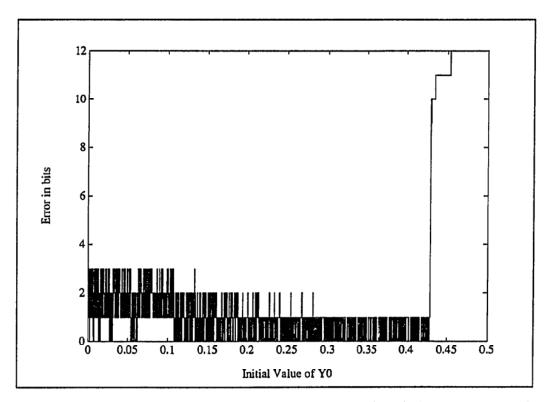

Figure 3.4: Error in the computed value of  $\tan^{-1}(1) = \tan^{-1}(y_0/y_0)$  over the entire range of  $y_0$  in a CORDIC module without normalization. The error has been quantized into the number of bits in error. A large error is observed for small values of  $y_0$ . For very large  $y_0$ , the large error is due to overflow. In the SVD problem, by choosing small values for the initial matrix, the values at all subsequent iterations can be kept sufficiently small as to avoid overflow. This experiment has been performed on a datapath that is 16 bits wide.

arithmetic implies normalization at every stage of computation, which prevents a loss of significant digits during Y-reduction iterations. The same effect can be achieved in fixed-point CORDIC by normalizing the initial values,  $x_0$  and  $y_0$ , before performing the CORDIC iterations.

Normalization involves increasing the absolute magnitude of  $x_0$  and  $y_0$  by multiplying them with the maximum power of 2 that does not cause the subsequent CORDIC iterations to result in an overflow. Since both x and y are shifted by the same amount, the inverse tangent is not affected and no post-processing is required. If x and y are represented by  $t_1$  bits, normalization tries to increase x and y until the third most significant bit is a 1. In the worst case, the two most significant bits are reserved to avoid overflow, since every step of Y-reduction, results in an increase in the magnitude of  $x_i$ . In the worst case,  $x_0 = y_0$ , which results in  $x_n = \sqrt{2}/K_n x_0 \approx 1.6468\sqrt{2}$ .

### 3.8.1 Single Cycle Normalization

If normalization is performed as a pre-processing step, it is necessary to reduce the number of cycles required. A single cycle normalization pre-processing step would require the following components:

**Barrel Shifter:** To handle any shift up to  $(t_1-2)$  in a single cycle, a barrel shifter is required. The area complexity of such a shifter is  $O(t_1^2)$ . A shifter with a few selected shifts would suffice if more cycles are allowed for normalization.

Leading Zero Encoder: The normalization shifts are determined by the number of leading-zeros in both  $x_0$  and  $y_0$ ; the register with fewer leading zeros determining the shift. For a single cycle implementation, this takes the form of a  $(t_1-2)$  bit leading-zero encoder, since  $(t_1-2)$  is the maximum shift that will be ever be encountered. The area complexity of this encoder is  $O(t_1^2)$ . Implementations

that allow more cycles for normalization would require smaller leading-zero encoders.

The hardware complexity of implementing normalization in a single-step is  $O(t_1^2)$ . An implementation with no associated time penalty and a low area complexity is described in the next section.

#### 3.8.2 Partial Normalization

The large error in inverse tangent computation occurs due to a loss of significant digits caused by the right shift associated with each iteration. If both  $x_0$  and  $y_0$  are small, then the maximum value of  $x_n$  is also small. Thus after only a few iterations of the form,

$$x_{i+1} = x_i + \delta_i y_i 2^{-i} (3.42)$$

$$y_{i+1} = y_i - \delta_i x_i 2^{-i}, (3.43)$$

the right shift, i, results in a complete loss of significant bits. Hence, the values of  $x_i$  and  $y_i$  remain unaffected by further iterations. Pre-normalization avoids this situation by artificially increasing the magnitudes of  $x_0$  and  $y_0$ .

The following scheme, called *Partial Normalization*, provides a low overhead solution to the normalization problem and is applicable to fixed-point CORDIC modules. Partial normalization reduces the hardware complexity by making normalization a part of the CORDIC iterations. Some of the initial CORDIC iterations are modified to include a small left shift of the results:

$$x_{i+1} = (x_i + \delta_i y_i 2^{-i}) 2^j (3.44)$$

$$y_{i+1} = (y_i - \delta_i x_i 2^{-i}) 2^j. (3.45)$$

This small shift introduces zeros in the low order bits, which are then shifted out in further CORDIC iterations. By keeping this shift a small integer, the hardware complexity of the shifter can be reduced. However, since the right shift, i, increases at each iteration, the magnitude of the left shift, j, should be large enough to prevent any loss of bits before normalization is complete. Using this technique, a small left shift can be used to simulate the effect of pre-normalization. The following theorem quantifies this idea.

**Theorem 3.2** Let  $t' = \arctan(y_0 2^k/x_0 2^k)$ , be the value calculated by preshifting  $x_0$  and  $y_0$  and using an unmodified CORDIC unit, where k is an integral multiple of a constant j. Let  $t = \arctan(y_0/x_0)$  be the value calculated by using a modified CORDIC unit and unnormalized initial values. The modified CORDIC unit initially performs k/j iterations of the form

$$x_{i+1} = (x_i + \delta_i y_i 2^{-i}) 2^j$$

$$y_{i+1} = (y_i - \delta_i x_i 2^{-i}) 2^j,$$

where i is the iteration index, followed by (n - k/j) unmodified CORDIC iterations. The two inverse tangents computed, t and t', will be identical if k < K, where K is an upper bound given by

$$K = 2j^2$$

**Proof** Let  $x'_i$  and  $y'_i$  be the intermediate values obtained in the computation of t' and  $x_i$  and  $y_i$  be the intermediate values obtained in the computation of t. Since a left shift of j is introduced in each modified CORDIC iteration, the desired shift of k requires k/j cycles to achieve. The two results are guaranteed to be identical if the following conditions hold:

- 1. At every iteration i < k/j,  $x_i$  and  $y_i$  are multiples of  $2^{m_i}$  where  $m_i \ge i$ . This condition prevents any loss of bits due to the right shift of i in a CORDIC iteration i, when i < k/j,

- In the computation of t', a similar condition should hold for x'<sub>i</sub> and y'<sub>i</sub> for at least k/j cycles.

The proof for this theorem first finds the maximum total shift, K, which can be achieved with modified iterations given a constant j, and then shows that for any k that is a multiple of j and less than K, condition 2 holds.

For the modified CORDIC module, at any iteration  $0 \le i < k/j$ ,  $x_i$  and  $y_i$  are multiples of  $2^{m_i}$  where

$$2^{m_i} = \frac{(2^j)^i}{2^{0+1+2+\dots+(i-1)}}$$

Imposing the condition required to avoid any loss of bits,

$$m_i \ge i$$

$\frac{(2^j)^i}{2^{i(i-1)/2}} \ge 2^i$

$ji - \frac{i(i-1)}{2} \ge i$

$i \le 2j-1$ .

Thus, the maximum number of iterations, for which no bits are lost is given by 2j. The maximum achievable total shift is  $K = (2j)j = 2j^2$ .

If  $k < 2j^2$  and is a multiple of j, then, in the computation of t', at the k/jth iteration (viz, i = k/j - 1), x' and y' are multiples of  $2^q$  where

$$q = k - \left[0 + 1 + 2 + 3 + \dots + \left(\frac{k}{j} - 2\right)\right].$$

Thus, no bits will be lost in the computation of t' within the first k/j iterations, if the condition  $q \ge k/j - 1$  is true. Solving this inequality,

$$k - \frac{(k/j-1)(k/j-2)}{2} \ge k/j-1$$

$k \le 2j^2$ .

This is exactly the condition  $k \leq K$ ; hence condition 2 holds.

Thus

$$K = 2j^2$$

is the upper bound such that if  $k \le K$ ,  $t' = t$ .

This theorem shows that if a constant shift of j is introduced in the CORDIC iterations, then any overall shift that is a multiple of j but less than  $2j^2$  can be achieved. In practice, the parameter j can be made a variable, allowing one of several shifts to be chosen at each iteration. An appropriate choice of these shifts can achieve any desired total shift.

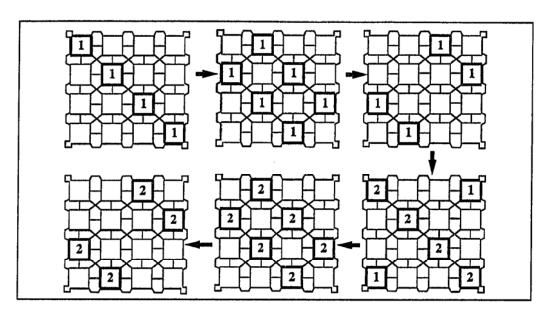

Suppose j in equation 3.44 and 3.45 can be chosen from a total of J shifts, shift  $[J-1] > \text{shift}[J-2] > \cdots > 1$ , if k is the desired shift, then the algorithm given in Figure 3.5, gives a choice of shifts at each iteration to normalize the input. This control can be implemented using combinational logic; a pair of leading-zero encoders and a comparator to select the smaller shift from the output of the encoders.

### 3.8.3 Choice of a Minimal Set of Shifts

The following is an example of a CORDIC unit with a data-width  $t_1 = 15$  bits and n = 16 iterations.

• An overall shift of 1 can be achieved only by making j = 1. Thus a shift of 1 is necessary in any implementation.

```

begin

for i := 0 to n do

begin

Choose maximum xindex such that x_i 2^{\text{shift}}[xindex] < 0.25;

Choose maximum yindex such that y_i 2^{\text{shift}}[yindex] < 0.25;

index := min( xindex, yindex );

Perform a modified CORDIC Iteration with j := index;

end

end

```

Figure 3.5: Modified CORDIC Iterations, invoked during Y-reduction when the input is not normalized

- Multiple iterations with j = 1 can achieve any shift up to a maximum of 2j² = 2.

A shift of 3, however, cannot be implemented as three iterations with j = 1, since this will result in a loss of significant bits. Hence, a shift of 3 requires a single iteration with j = 3 that necessitates the inclusion of the shift j = 3.

- The shift j=3 can achieve any shift up to a maximum  $2j^2=18$  as given by Table 3.2. Since the maximum shift required is 13, the normalization shifter does not have to implement any shift other than 0, 1 and 3. Any shift that is not a multiple of 3 is performed as shifts of 3 for  $\lfloor k/3 \rfloor$  iterations, followed by iterations with j=1 to achieve the remaining shift.

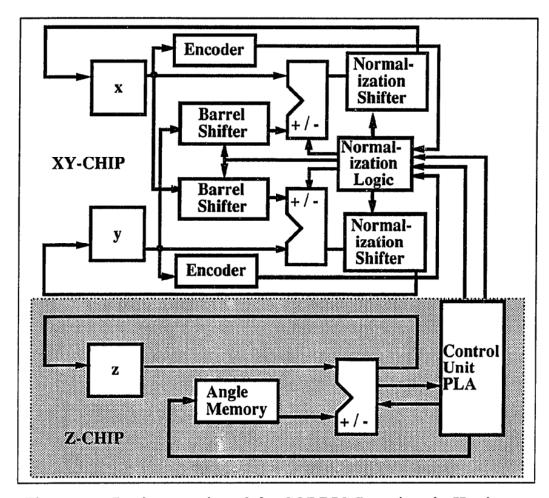

Figure 3.6 shows a hardware implementation of the CORDIC unit that includes the above normalization scheme. The number of bits in error using such a scheme is bounded even for small initial values, as shown in Figure 3.7.

Figure 3.6: Implementation of the CORDIC Iterations in Hardware

| Shift introduced in each CORDIC iteration | Maximum shift that can be achieved |

|-------------------------------------------|------------------------------------|

| j                                         | k                                  |

| 1                                         | 2                                  |

| 2                                         | 8                                  |

| 3                                         | 18                                 |

| 4                                         | 32                                 |

Table 3.2: Total shifts that can be achieved with a small shift in each iteration, as part of a novel normalization scheme

Figure 3.7: Error in the computed value of  $\tan^{-1}(y_0/y_0)$  over the entire range of  $y_0$  in a CORDIC module that implements the partial normalization scheme

### 3.8.4 Cost of Partial Normalization Implementation

For a CORDIC implementation with the data width of the x and y datapaths  $t_1$  bits, a shifter with a maximum shift  $\sqrt{t_1/2}$  is required. The shifts at each iteration are obtained from leading-zero encoders that encode the  $\sqrt{t_1/2}$  most significant bits of the x and y variables. The hardware costs involved in these operations are:

Shifter: The area complexity [34] of the shifter grows as

$$O(t_1 \times \text{Maximum Shift required}) = O(t_1 \times \sqrt{t_1}) = O(t_1^{1.5}).$$

Control Logic: The size of the control logic grows as  $O((\text{Maximum Shift required})^2)$ =  $O(\sqrt{t_1}^2) = O(t_1)$ .

Time Penalty: The shifting is performed as part of the CORDIC iterations. Thus, the only time penalty is the decrease in the clock rate due to the extra propagation delay caused by the presence of the shifter in the CORDIC data path. This effect can be neglected for most cases. Hence, this scheme does not require any extra clock cycles.

### 3.9 Summary

CORDIC is an efficient technique to implement inverse tangent and vector rotation computations in hardware. Rotation of a vector is implemented as several iterations of rotations through a set of fixed angles given by  $\alpha_i = \tan^{-1}(2^{-i})$ , where  $i = 0, 1, 2, \dots, (n-1)$ , is the iteration count. These rotations reduce to the following iterative relations:

$$x_{i+1} = x_i + \delta_i y_i 2^{-i}$$

$$y_{i+1} = y_i - \delta_i x_i 2^{-i}$$

$$z_{i+1} = z_i + \delta_i \alpha_i$$

|             | Z-Reduction  Maximum Error in computed value of vector rotation (Number of bits) | Y-Reduction  Maximum Error in  computed value of $\tan^{-1}(y_0/x_0)$ (Number of  bits) |

|-------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Walther     | $\log n$                                                                         |                                                                                         |

| Johnsson    | $(L-n)$ , where $L > n + \log_2(2n - L - 3)$                                     |                                                                                         |

| Duryea      | $\log \left[ \frac{7}{6} n 2^{-t_1} + 2^{-(n-1)} \right]$                        | $\log \left[ (n+1)2^{-t_1} + 2^{-(n-1)} \right]$                                        |

| Section 3.5 | $\log_2 \left[ (2^{-(n-1)} + n2^{-t_2}) + (n)2^{-t_1} \right]$                   | $\log_2\left[\frac{2nK_n2^{-t_1}}{\sqrt{x_0^2+y_0^2}}+n2^{-t_2}\right]$                 |

Table 3.3: Summary and Comparison of the maximum errors obtained from previous methods

These relations can be implemented using simple structures: adders, shifters and a small ROM table of angles. The direction of rotation,  $\delta_i$ , of each iteration is determined by the data and the function that is to be evaluated. If  $\delta_i$ s are chosen to reduce the initial  $z_0$  to zero, it is termed Z-reduction, and is used to compute vector rotations. On the other hand, a choice which reduces the initial  $y_0$  to zero, is called Y-reduction and is used to compute inverse tangents. A detailed error analysis takes into account the errors due to the finite-precision representation in both the x, y iterations and the z iterations. Table 3.3 gives a summary of the error bounds given by present and previous methods. The analysis indicates that normalization of the input values is required for Y-reduction to bound the errors. Hardware complexity

of a normalization scheme would be  $O(n^2)$  using generic techniques. If the required total left shift is performed as several iterations of small shifts, however, it is possible to perform normalization as a part of the CORDIC iterations. The modified CORDIC iterations are:

$$x_{i+1} = (x_i + \delta_i y_i 2^{-i}) 2^j \tag{3.46}$$

$$y_{i+1} = (y_i - \delta_i x_i 2^{-i}) 2^j. (3.47)$$

A constant shift of j can be used to perform any left shift up to  $2j^2$  through several iterations. A shifter with multiple values of j is required in an actual implementation. Such a partial normalization scheme reduces the hardware complexity to  $O(n^{1.5})$ , with no associated time penalty.

# Chapter 4

### The CORDIC-SVD Processor Architecture

#### 4.1 Introduction

The SVD algorithm discussed in Chapter 2 and the CORDIC algorithm described in Chapter 3 form the basis for the design of the CORDIC-SVD processor. The processor has been designed in two phases. Initially, a six chip prototype of the processor was designed. Once the basic blocks were identified, they were designed, fabricated and tested independently by different design groups. The prototype was built of TinyChips, fabricated by MOSIS, which are cost effective and serve as a proof of concept. Implementation of the processor as a chip set provided controllability and observability that was essential at that stage of design. This prototype served as a means of exhaustively testing every aspect of the design, which was not possible with simulation.

The second phase involved designing a single chip version of the processor. This chip utilized many of the basic blocks from the six-chip prototype, in an enhanced architecture. The single chip version utilized better layout techniques using higher level design tools. Some of the low level VLSI layout issues are discussed in Chapter 6.

# 4.2 Architecture of the Prototype

The basic structure of the CORDIC SVD processor was discussed by Cavallaro [6].

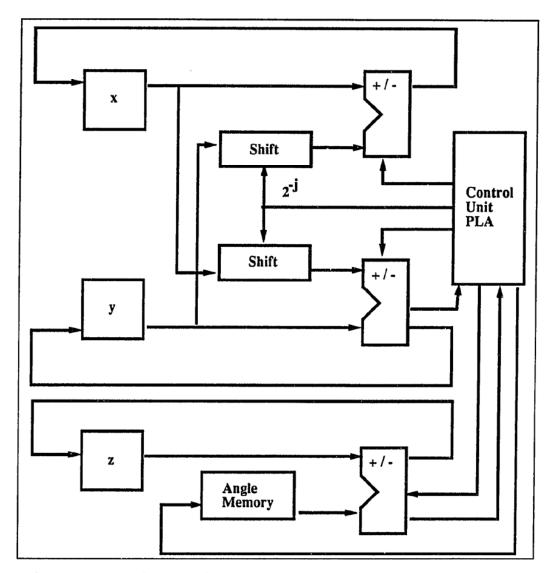

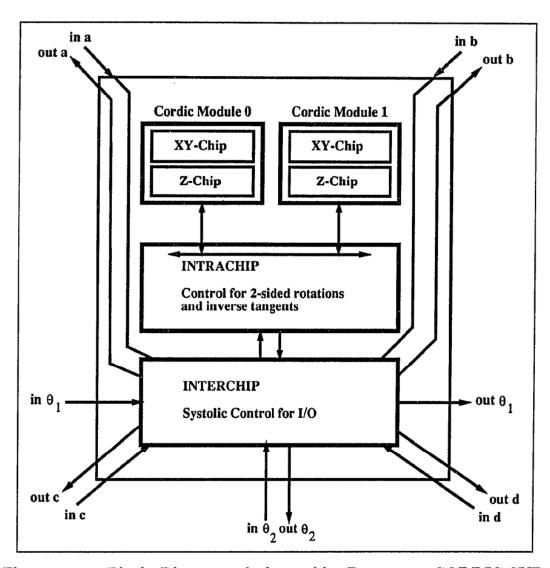

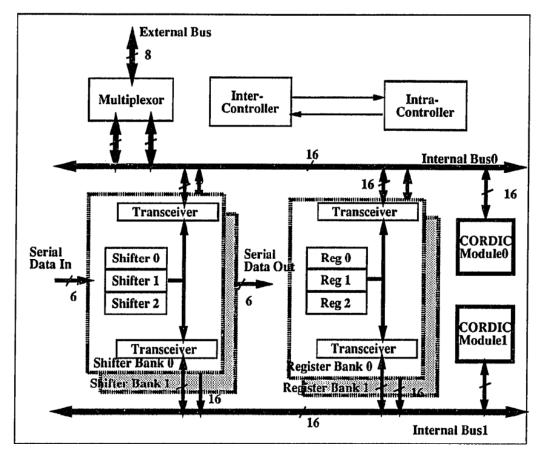

Figure 4.1: Block Diagram of the 6-chip Prototype CORDIC-SVD Processor

This architecture, shown in Figure 4.1, consists of four distinct modules that have been implemented in four different TinyChips. Two of the chips, the xy-chip and the z-chip, together form one CORDIC module. Maximal parallelism is achieved in the computation of the  $2 \times 2$  SVD by including two CORDIC modules in the processor. The control and interconnection for the SVD processor was implemented in two separate chips. The intracontroller chip is used to provide all the internal control necessary to implement the computation of the  $2 \times 2$  SVD. The systolic array control is provided by the intercontroller chip. A hierarchical control mechanism provides a way to effectively shield the low level control details from the higher level controllers. At each level the controllers provide a set of macros to the controller next in the hierarchy. In addition, this separation of control allows a degree of concurrency not possible with a single controller. The next few sections describe the individual chips in greater detail.

#### 4.2.1 Design of the XY-Chip