DOCKET NO.: 0107131-00645US1 Filed on behalf of Intel Corporation

By: John V. Hobgood, Reg. No. 61,540

Richard Goldenberg, Reg. No. 38,895

Dominic Massa, Reg. No. 44,905

Wilmer Cutler Pickering Hale and Dorr LLP

60 State Street

Boston, MA 02109

Email: John. Hobgood@wilmerhale.com

Richard.Goldenberg@wilmerhale.com

#### UNITED STATES PATENT AND TRADEMARK OFFICE

\_\_\_\_

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

Intel Corporation Petitioner

v.

VLSI Technology LLC Patent Owner

Case IPR2019-01192

DECLARATION OF DR. CARL SECHEN U.S. PATENT NO. 7,523,331 CLAIM 7

# TABLE OF CONTENTS

|       |                                      | ı                                                                           | age |

|-------|--------------------------------------|-----------------------------------------------------------------------------|-----|

| I.    | INTRODUCTION                         |                                                                             |     |

| II.   | BACKGROUND TECHNOLOGY                |                                                                             | 5   |

|       | A.<br>B.                             | Computer Memory Operating Modes and Interrupts                              |     |

| III.  | OVE                                  | OVERVIEW OF THE '331 PATENT                                                 |     |

| IV.   | LEVEL OF ORDINARY SKILL IN THE ART12 |                                                                             |     |

| V.    | UNDERSTANDING OF THE LAW             |                                                                             |     |

| VI.   | CLAIM CONSTRUCTION                   |                                                                             | 15  |

| VII.  | SUMMARY OF THE PRIOR ART REFERENCES  |                                                                             | 16  |

|       | A.<br>B.<br>C.                       | Irie'331 Patent AAPA                                                        | 19  |

| VIII. | SUMMARY OF OPINIONS                  |                                                                             |     |

| IX.   | INVALIDITY OF THE CHALLENGED CLAIMS  |                                                                             |     |

|       | A.                                   | Ground I: Claim 7 is Rendered Obvious by Irie in View of AAPA               | 23  |

|       |                                      | 1. Claim 7                                                                  | 23  |

|       | В.                                   | Ground II: Claim 7 is Rendered Obvious by Irie in View of AAPA and Bourekas |     |

|       |                                      | 1. Claim 7                                                                  | 59  |

| X.    | AVAILABILITY FOR CROSS-EXAMINATION76 |                                                                             | 76  |

| XI.   | RIGHT TO SUPPLEMENT76                |                                                                             |     |

| XII.  | JURA                                 | AT                                                                          | 76  |

I declare as follows:

#### I. INTRODUCTION

- 1. My name is Dr. Carl Sechen.

- 2. I earned a B.E.E. in Electrical Engineering from the University of Minnesota in 1975, followed by a M.S. in Electrical Engineering from the Massachusetts Institute of Technology in 1977. I earned a Ph.D. in Electrical Engineering from the University of California, Berkeley in 1986.

- 3. I have been a Professor of Electrical Engineering for 33 years. Since August 15, 2005, I have been a Professor of Electrical and Computer Engineering at the University of Texas at Dallas. From July 1992 to August 14, 2005, I served as a Professor of Electrical Engineering at the University of Washington. From July 1986 through June 1992, I served as an Assistant Professor and then Associate Professor of Electrical Engineering at Yale University.

- 4. Over these years my research has focused on the design and computer-aided design of digital integrated circuits, including computer architecture and the design of dynamic random-access memory ("DRAM") and static random-access memory (SRAM) modules. I have taught numerous students how to design DRAM and SRAM memories as part of the design courses that I have offered.

- 5. As a professor, I have developed and taught numerous courses, in particular, several courses that teach digital integrated circuit design and memory design in great detail. I have taught these courses continuously for the past 24 years. I have taught digital integrated circuit design and memory design to undergraduate and graduate students at the University of Washington and at the University of Texas at Dallas since 1995.

- 6. I have also been involved in numerous research projects on digital integrated circuit design and memory design. I have taught numerous graduate researchers how to design digital integrated circuits, including memories. Most of these had applications in computer architecture. I have also taught several Ph.D. graduate students how to design digital integrated circuits, including the design of various types of computer circuits and memories. I have authored or coauthored over 190 papers and one book, the majority of which concern digital integrated circuit design and memory design.

- 7. I was elected a Fellow of the IEEE in 2002 for contributions to placement and routing of ASICs. IEEE stands for Institute of Electrical and Electronics Engineers, which is the leading professional association for electrical engineers. The Board of Directors of the IEEE awards the rank of "Fellow" to individuals with an extraordinary record of accomplishments in any of the IEEE fields of interest. The total number of IEEE members who can be named Fellows

U.S. Patent No. 7,523,331 Claim 7

in any one year cannot exceed one-tenth of one percent of the total voting IEEE membership.

- 8. I received several research and teaching awards during my career. I received the Semiconductor Research Corporation's Inventor's Recognition Award in 1988 and in 2001. I also received the Technical Excellence Award from the Semiconductor Research Corporation in 1994. While serving as Professor at the University of Washington, I received the Outstanding Research Advisor award from the Department of Electrical Engineering in 2002. In 2008, I received the Distinguished Teacher of the Year Award from the Department of Electrical Engineering at the University of Texas at Dallas. I also received the Distinguished Teaching Award for the Erik Johnson School of Engineering and Computer Science in 2014.

- 9. Over the years, I have also received funding to conduct research in computer circuits and memory designs, including area-efficient and reliable embedded DRAM and SRAM design. Together with my graduate students, I have designed and fabricated various types of DRAM and SRAM chips.

- 10. I am a co-inventor on a provisional patent application and an issued patent directed to transistor and computational logic technologies.

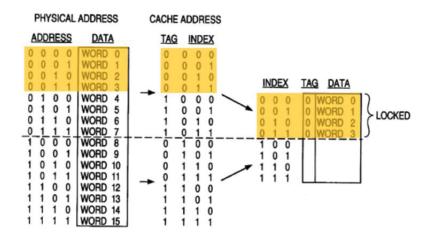

- 11. A copy of my CV is attached as Appendix A.

- 12. I have reviewed the specification, file history and claims of U.S. Patent No. 7,523,331 to Gerardus Wilhelmus Theodorus Van Der Heijden (the "'331 patent") (Ex. 1001).

- 13. I have reviewed and understand the following references that form the grounds of the petition:

- Japanese Patent Application Publication JP 2000-105639 (English Translation) ("Irie") (Ex. 1002)

- Applicant Admitted Prior Art from U.S. Patent 7,523,331 ("AAPA")

(Ex. 1001)

- U.S. Patent 5,694,567 ("Bourekas") (Ex. 1005)

- 14. I have also reviewed and understand the following documents cited in the petition: Ex. 1006, Ex. 1007, and Ex. 1009 Ex. 1025.

- 15. I have been retained by Petitioner, Intel Corporation, to provide my opinion concerning the validity of the '331 patent in support of its petition for *inter* partes review of the '331 patent.

- 16. I am being compensated at my normal consulting rate of \$375 per hour for my work. My compensation is not in any way dependent on the outcome of any *inter partes* review, and in no way affects the substance of my statements in

this declaration, nor have I any financial or personal interest in the outcome of this proceeding.

17. To the best of my knowledge, I have no financial interest in Petitioner, Intel Corporation, or in the '331 patent. To the extent any mutual funds or other investments I own have a financial interest in the Petitioner or the '331 patent, I do not knowingly have any financial interest that would affect or bias my judgment.

# II. BACKGROUND TECHNOLOGY

# A. Computer Memory

18. Computers have memory that stores information such as data and program instructions. K.R. Kaplan and R.O. Winder, "Cache-based Computer Systems,", March 1973 ("Kaplan") (Ex. 1018), 30. Such memory is typically divided into main memory and cache memory. Ex. 1002, ¶¶ 0011-0012; Ex. 1018, 30. Main memory is commonly used at computer start up because it stores programs that execute when the computer is turned on. U.S. Patent Publication 2002/0026601 ("Shiraga") (Ex. 1020), ¶¶ 0008, 0009. ROM (Read Only Memory) and SRAM (Static Random Access Memory) are examples of main memory. *Id.*, ¶ 0008. For instance, ROM stores start-up programs that execute when a computer is powered on and SRAM stores programs during the operation of the computer. *Id.*, ¶ 0009. Dynamic RAM, also known as "DRAM," is a common type of main memory RAM. *Id.*, Abstract, ¶ 0005. In contrast, cache memory is used to store information that is

most recently accessed from main memory and provide fast access to this information if it is subsequently needed again. Ex. 1018, 30. SRAM can also be used for cache memory; SRAM is "static" in that it does *not* need to periodically refresh, which is different from dynamic RAM, and because of this difference SRAM cache consumes much less power than DRAM. John L. Hennessy and David A. Patterson, *Computer Organization and Design: The Hardware/Software Interface* 541 (2nd ed. 1998) ("Hennessy 2nd") (Ex. 1019), 541.

- 19. As I explain above, cache memory stores information so it can be accessed easily when the information is needed again without recourse to main memory. Ex. 1018, 30. An exemplary process where cache memory is used, which shows cache memory functionality, is as follows:

- Information is needed by a processor. *Id.*

- The main memory address associated with the information is used to try retrieving the information from cache. *Id.*, 30-32.

- A "cache hit" occurs if the information corresponding to the main memory address is found in cache. *Id.*, 32. The information is then obtained from the cache without accessing the slower main memory. *Id.*

- If the information is not found in the cache, a "cache miss" occurs; here, the main memory must be accessed for the information, and once it is obtained, the information is placed in cache. *Id*.

- A difference between main memory and cache memory is access speed; 20. cache memory is accessed much faster than main memory because cache stores information retrieved from main memory that was recently used by a processor. Ex. 1018, 30. Moreover, the typical access time is less for cache memory SRAM compared to main memory DRAM. Ex. 1019, 541; see also John L. Hennessy and David A. Patterson, Computer Architecture: A Quantitative Approach, at ix, 13, 277-278 (3rd ed. 2003) ("Hennessy 3rd") (Ex. 1023), 394, Fig. 5.3 (reporting typical access times in 2001 of 0.50-25 ns for CMOS SRAM cache and 80-250 ns for CMOS DRAM main memory). Hennessy 2nd explains that "[t]o save pins and reduce the package cost, the same address lines are used for both the row and column address; a pair of signals called RAS (Row Access Strobe) and CAS (Column Access Strobe) are used to signal the DRAM that either a row or column address is being supplied." Ex. 1019, B-32. Hennessy 2nd continues, "The two-level addressing scheme, combined with the internal circuitry, make DRAM access times much longer (by a factor of 5 to 10) than SRAM access times." *Id*. This means that cache memory can quickly provide this information if it is subsequently needed—much faster than if the information was obtained again from main memory. Id.

- 21. Computer memory is usually organized at different hierarchical levels determined by access speed. Ex. 1019, 541. At the higher level, which is closer to the computer processor, sits cache memory because it operates at a faster speed

compared to main memory. *Id.* Programs are stored in these various memory levels of memory, and when memory at one level (e.g., main memory) is deactivated, programs can be stored in memory at a different level (e.g., cache memory). Ex. 1002, ¶¶ 0028, 0032.

- 22. Information in a memory is accessed for reading/writing using a memory address formed from a "tag" and "index" that identifies a memory location. Ex. 1005, 1:18-30; Ex. 1019, 552-553. Addresses are uniquely identified and differentiated by the tag and index. Ex. 1005, 1:27-54.

- 23. Cache memory information can be organized in various ways, and a relationship can exist between main memory addresses and where information of these addresses are stored in cache memory. The relationship can be determined at the time of caching or ahead of time. Mapping the main memory and cache memory to each other ahead of time can provide that program instructions stored in a certain portion of main memory are cached in a certain portion of cache memory. *See* Ex. 1005, 4:64-5:3.

# **B.** Operating Modes and Interrupts

24. Operating modes define the state of a computer. For instance, in a "normal" mode, a computer may have full functionality and execute all instructed programs. Ex. 1002, ¶¶ 0022-0023. In contrast, in a "low power" mode, which is

also known as a "standby mode," all or part of the computer may be powered down, and only part of the computer may be available for use. Id., ¶¶ 0034-0035.

- 25. "Interrupts" can be used to make a computer move from one operating mode to another. Ex. 1002, ¶ 0037. For instance, an interrupt signal can make a processor interrupt its current state and perform a particular operation. *Id.* I provide an example of this situation: a computer may not be in use, and may place itself in a low power mode (standy mode) where its display and certain processors, circuitry, and/or memory are powered down to conserve power. *Id.*, ¶¶ 0034-0036. An interrupt signal may instruct the computer to wake up from this low power mode and return to a normal operating mode. *Id.*, ¶ 0037. For instance, the interrupt signal may be generated by pressing the computer's power button. *Id.*

- 26. In a low power mode, computers usually power down most of their memory. Thus, interrupt programs can be stored in memory parts that are not powered down, such as cache memory, and executed from the cache memory. Ex. 1002, ¶¶ 0032, 0037.

#### III. OVERVIEW OF THE '331 PATENT

27. The '331 patent states that prior art computing devices could not perform "certain basic functions" like processing interrupts "in the low power mode without switching to the normal operating mode." Ex. 1001, 1:16-20. The patent says these prior art devices were problematic: "[s]witching back the apparatus to a

normal operating mode to perform such basic functions ... considerably increase[s] power consumption" when "performed frequently while the apparatus does not have to return to full operation for other reasons." *Id.*, 1:21-25.

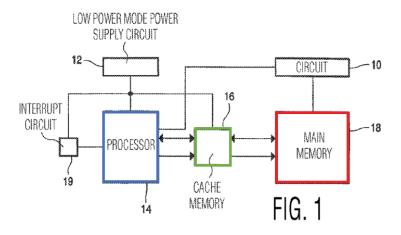

28. Fig. 1 of the '331 patent is shown below:

Ex. 1001, Fig. 1<sup>1</sup>

- 29. The Fig. 1 apparatus includes a processor 14, cache memory 16, and main memory 18 and says that in a "normal operating mode cache memory 16 functions as a conventional cache memory 16." Ex. 1001, 2:35-36.

- 30. The apparatus switches from the normal operating mode to a "low power operating mode" and the switch can occur when the apparatus detects "it is no longer necessary to operate in the normal mode." Ex. 1001, 3:7-11. Part of the switch includes that instructions of an interrupt program stored in main memory 18

<sup>&</sup>lt;sup>1</sup> I have added color annotations to figures unless otherwise noted.

may be loaded into cache memory 16. *Id.*, 3:16-19. For instance, the '331 patent says that "[t]he interrupt program is stored at addresses in main memory that have been selected so that all instructions of the interrupt program can be stored together in cache memory 16." *Id.*, 3:19-22.

- 31. Loading can be performed in various ways. A "switchover program" may be used to "switch [the apparatus] over to the low power mode" and can be provided with the start address and end address of the interrupt program stored in main memory. Ex. 1001, 3:12-13, 23-25. The information at these addresses can be loaded from the main memory 18 into cache memory 16 using this program. Id., 3:25-28. A "conventional locking mechanism" can be used by cache memory 16, which "enables processor 14 to signal that (and optionally from which addresses) instructions and/or data must be kept in cache." *Id.*, 3:31-36. Alternatively, the patent says that the interrupt program "may be stored at addresses that are selected so that it is ensured in advance that the switchover program can load the entire interrupt program into cache memory 16 without being subsequently discarded." *Id.*, 3:38-43. The patent also says that processor 14 may "contain[] an instruction to cause specified instructions, or specifically the interrupt routine, to be loaded into cache memory 16." Id., 3:43-46.

- 32. The processor can execute the interrupt program without accessing main memory after the instructions have been loaded into cache memory 16 and the

apparatus is in the low power mode. Ex. 1001, 1:53-62. The main memory can be deactivated to reduce power consumption since it is not used. *Id.*, 1:63-2:6. For instance, the patent says that "all instructions of the interrupt program can be stored together in cache memory," and that "[t]he interrupt program is stored at addresses in main memory that have been selected so that all instructions of the interrupt program can be stored together in cache memory 16." *Id.*, 3:19-22. Storing all the instructions together in the cache (as opposed to having some instructions reside in main memory) allows the processor to "execute the interrupt program without recourse to main memory 18." *Id.*, 3:65-67.

# IV. LEVEL OF ORDINARY SKILL IN THE ART

33. A person of ordinary skill in the art ("POSA") at the time of the alleged invention would have had at least: (1) an undergraduate degree in electrical engineering (or an equivalent subject), together with at least two years of post-graduate experience designing cache systems; or (2) a master's degree in electrical engineering (or equivalent subject) together with at least one year of post-graduate experience in designing cache systems.

#### V. UNDERSTANDING OF THE LAW

34. I am not an attorney. For the purposes of this declaration, Petitioner's counsel has informed me about certain aspects of the law that are relevant to my opinions.

- 35. Petitioner's counsel has informed me that a patent claim may be "anticipated" if each element of that claim is present either explicitly or inherently in a single prior art reference.

- 36. Petitioner's counsel has informed me that a patent claim can be considered to have been obvious to a POSA at the time the application was filed. This means that, even if all of the requirements of a claim are not found in a single prior art reference, the claim is not patentable if the differences between the subject matter in the prior art and the subject matter in the claim would have been obvious to a POSA at the time the application was filed.

- 37. Petitioner's counsel has informed me that a determination of whether a claim would have been obvious should be based upon several factors, including, among others:

- the level of ordinary skill in the art at the time the application was filed;

- the scope and content of the prior art;

- what differences, if any, existed between the claimed invention and the prior art.

- 38. Petitioner's counsel has informed me that a single reference can render a patent claim obvious if any differences between that reference and the claims would have been obvious to a person of ordinary skill in the art. Alternatively, the teachings of two or more references may be combined in the same way as disclosed

in the claims, if such a combination would have been obvious to one having ordinary skill in the art. In determining whether a combination based on either a single reference or multiple references would have been obvious, it is appropriate to consider, among other factors:

- whether the teachings of the prior art references disclose known concepts combined in familiar ways, and when combined, would yield predictable results;

- whether a POSA could implement a predictable variation, and would see the benefit of doing so;

- whether the claimed elements represent one of a limited number of known design choices, and would have a reasonable expectation of success by those skilled in the art;

- whether a person of ordinary skill would have recognized a reason to combine known elements in the manner described in the claim;

- whether there is some teaching or suggestion in the prior art to make the modification or combination of elements claimed in the patent; and

- whether the innovation applies a known technique that had been used to improve a similar device or method in a similar way.

- 39. Petitioner's counsel has informed me that one of ordinary skill in the art has ordinary creativity, and is not an automaton. Petitioner's counsel has

informed me that in considering obviousness, it is important not to determine obviousness using the benefit of hindsight derived from the patent being considered.

# VI. CLAIM CONSTRUCTION

- 40. I have been informed that a claim in *inter partes* review is given its plain and ordinary meaning as understood by a POSA at the time of the invention in light of the claim language, specification, and prosecution history.

- 41. I understand that claim 7 requires an interrupt program be stored at "addresses in main memory that have been selected so that all instructions of the interrupt program can be stored together in the cache memory." In my opinion, the '331 patent's specification does not describe the meaning of "stored together." The patent just says that the instructions are "stored together," repeating the claim language. Ex. 1001, 3:19-22. In my opinion, the file history does not provide explanation of the term either. See Amendment (03/18/08) (Ex. 1013). This recitation of claim 7 should therefore have its plain and ordinary meaning.

- 42. Indeed, a POSA would have understood that the plain meaning of "addresses in main memory that have been selected so that all instructions of the interrupt program can be stored together in the cache memory" would at least

<sup>&</sup>lt;sup>2</sup> Bolding, underline, and/or italics have been added to quotes, unless otherwise noted.

encompass addresses in main memory that have been selected so that all instructions of the interrupt program can be stored in a single cache memory or a single part of cache memory at the same time, and this interpretation is taught by the reference Irie. The '331 patent supports this understanding that all instructions of the interrupt program must be present in the cache memory during the low power operating mode so the interrupt program can be executed from the cache memory. See Ex. 1001, 3:48-67. For instance, the '331 patent says that "Once the interrupt program has been loaded into cache memory 16, the switchover program ... cause[s] processor 14 to signal to main power supply circuit 10 to deactivate itself," and this is known as, "the low power operating mode." Id., 3:48-54. The '331 patent also says that "During operation in low power operating mode," processor 14 may "execute the interrupt program," and "During execution of the interrupt program main memory 18 remains deactivated." *Id.*, 3:55-61. Thus, "processor 14... is able to execute the interrupt program without recourse to main memory 18." Id., 3:64-67. Thus, these sections at least show that all instructions of the interrupt program must be present in the cache memory during the low power operating mode so the interrupt program can be executed from the cache memory.

#### VII. SUMMARY OF THE PRIOR ART REFERENCES

#### A. Irie

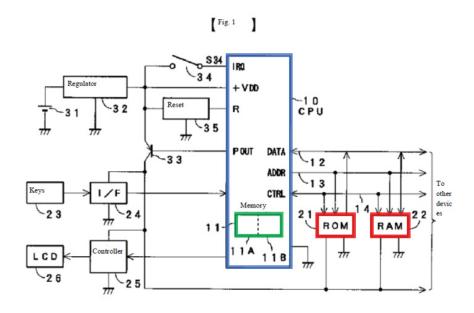

43. Irie discloses a mobile information terminal shown in Fig. 1:

Ex. 1002, Fig. 1

- 44. The mobile information terminal includes a CPU 10,<sup>3</sup> ROM 21, RAM 22, and cache memory 11. Ex. 1002, ¶¶ 0010-0013. CPU 10 is a "circuit" that "executes ... process[es]" and routines such as routine 100 and routine 300, and provides "system control." *Id.*, ¶¶ 0009, 0011, 0024, 0028. ROM 21 stores "programs for controlling the mobile information terminal." *Id.*, ¶ 0013, Fig. 1. RAM 22 "provides a work area and a stack area for the CPU 10." *Id.*, ¶¶ 0013-0014.

- 45. The terminal is operational in a "normal operating mode" when power switch 34 is in an "on" position, and in the normal operating mode, cache memory 11 operates according to a "first mode" where an "entire area (all addresses) of memory 11 can be used as cache memory." Ex. 1002, ¶¶ 0009, 0011, 0012, 0022-

<sup>&</sup>lt;sup>3</sup> CPU is a term known in the art to stand for "central processing unit."

0023, 0025, 0037, 0041, claim 1, Abstract. The terminal is placed in an "energy-saving mode" when power switch 34 is moved from "on to off." Ex. 1002, ¶¶ 0013-0014, 0024, 0028, 0033, Figs. 2-4.

- 46. Irie explains that instructions for an interrupt processing program are loaded from ROM 21 to RAM 22, and then from RAM 22 to cache memory 11 when the terminal switches to the energy-saving mode.<sup>4</sup> Ex. 1002, ¶¶ 0024-0032, Figs. 2-4. This process (governed by routine 300) is performed as follows:

- CPU 10 determines a starting address location in ROM 21 storing the program instructions. *Id.*, ¶¶ 0028, 0032, Fig. 4.

- CPU 10 then copies instructions at that address to a temporary location in RAM 22. *Id*.

- Instructions are next moved from the temporary location in RAM 22 to cache memory 11. *Id.*, ¶¶ 0027-0031.

<sup>&</sup>lt;sup>4</sup> Irie describes instructions for an interrupt processing program because programs are formed by instructions; thus, the content of Irie's interrupt processing program includes instructions. *See* Ex. 1019, 14 ("The processor is the active part of the board, following the **instructions of a program** to the letter."); *see id.*, 61 ("the machine had to execute the instruction to run the program, the execution time must depend on the **number of instructions in a program**.").

- CPU 10 then determines a subsequent address location in ROM 21 where further program instructions are stored, reads the instruction content stored at this subsequent address location, copies it to the same temporary location in RAM 22, and the instructions are moved from the temporary location in RAM 22 to cache memory 11. *Id.*, ¶¶ 0028-0032.

- This process is continued until a final address location in ROM 21 is reached. *Id.*, ¶¶ 0029-0030.

- 47. The terminal may then be in an energy-saving mode. Ex. 1002, ¶¶ 0032-0037. To switch CPU 10 back to the normal operating mode, the interrupt processing program copied to cache memory 11 is executed from the cache memory (in particular, cache area 11A of cache memory 11). *Id*.

#### B. '331 Patent AAPA

48. The '331 patent admits that many concepts related to computer memory are known, conventional, and therefore in the prior art. Likewise, the claims of the '331 patent include recitations that the patent admits were known. For instance, the '331 patent's applicant admitted prior art ("AAPA") admits the following: "Known apparatuses that contain a computer processor and a main memory with data and/or instructions for use by the processor are often provided with a cache memory in order to speed up execution." Ex. 1001, 1:34-37. Thus, the '331 patent admits that systems including (1) a computer processor,

- (2) a cache memory, and (3) a main memory were known, and that storing data and/or instructions in main memory for use by the processor was known. *Id.*, 1:34-49.

- 49. The AAPA also admits the following about these **known** systems: "[t]he cache memory temporarily stores copies of part of the data and/or instructions that the processor has addressed in main memory, so that it can be retrieved given its main memory address" and "[w]hen the processor addresses such data and/or instructions again, the cache memory substitutes the cached data and/or instructions for the data and/or instructions from main memory." Ex. 1001, 1:37-43. I note that this admittedly known disclosure from AAPA is the equivalent of language in claim 7, including limitation 7[c], as explained below.

- 50. AAPA further states: "cache memory is **conventionally** one of the circuits that are deactivated when the apparatus is switched to the low power mode, because it merely stores redundant copies of part of the data and/or instructions that were used during previous processing." Ex. 1001, 1:45-49. Thus, AAPA admits to the conventional behavior that its known apparatuses (which include a computer processor, cache memory, and main memory) provide. *Id*.

- 51. There are additional areas where '331 AAPA admits what is in the prior art:

- "[i]n the normal operating mode cache memory 16 functions as a conventional cache memory 16;" AAPA explains that in this conventional operation, "[w]hen processor 14 needs an instruction and/or data, processor 14 outputs the address with which the instruction and/or data is addressed in main memory on its address/data interface" and "[c]ache memory 16 receives the address and tests whether an instruction and/or data corresponding to the address is stored in cache memory 16." Ex. 1001, 2:35-42.

- AAPA further explains this conventionality when it notes

"[t]echniques for this type of testing are known per se" and in the

conventional process, "[i]f the addressed instruction and/or data is

available in cache memory 16, cache memory 16 returns the

instruction and/or data from cache memory 16" but "[i]f the addressed

instruction and/or data is not available in cache memory 16, cache

memory forwards the address to main memory 18, which returns the

instruction and/or data to cache memory 16." *Id.*, 2:42-48.

- AAPA also admits that in this conventional process, "[c]ache memory 16 then supplies the instruction and/or data from main memory 18 to processor 14" and "[p]referably, cache memory 16 also stores a copy

of this instruction and/or data, for later use, when processor 14 uses the address again." *Id.*, 2:48-52.

# C. Bourekas

- 52. Bourekas' system has a cache memory, main memory, and CPU–just like Irie and AAPA. Ex. 1005, 3:46-64, 4:21-24. Bourekas discloses how main memory and cache memory are mapped to each other, and how saving information in one part of main memory means that the information will be cached in a certain part of cache memory. *Id.*, 3:65 4:2, Fig. 3. For instance, Bourekas describes a main memory having a physical address range 0000 to 0111 and 1000 to 1111 and a cache memory having a cache index range 000 to 011 and 100 to 111. *Id.*Information can be locked in certain addresses of the cache memory so they are not deleted. For example, Bourekas explains that a program can be locked in the "lower-order half of the cache RAM," which refers to cache index addresses 000 to 011. *Id.*, 4:2-5, Fig. 3.

- 53. The physical address range 0000 to 0111 of main memory is mapped to the cache index range 000 to 011. Ex. 1005, 3:65 4:2, Fig. 3. The physical address range 1000 to 1111 of main memory is mapped to the cache index range 100 to 111. *Id.* Thus, a user can lock a "4 word program" stored at main memory physical address range 0000 to 0011 in the "lower-order half of the cache RAM" cache address at 000 to 011. *Id.*, 4:2-5, Fig. 3.

# VIII. SUMMARY OF OPINIONS

54. It is my opinion that every limitation recited in claim 7 of the '331 patent is disclosed by the prior art, and is anticipated and/or rendered obvious by the prior art.

# IX. INVALIDITY OF THE CHALLENGED CLAIMS

- A. Ground I: Claim 7 is Rendered Obvious by Irie in View of AAPA

- 1. Claim 7

- a) 7[a]: "A method of operating an apparatus that contains an instruction processing circuit, a main memory addressable by the instruction processing circuit and a cache memory, the method comprising"

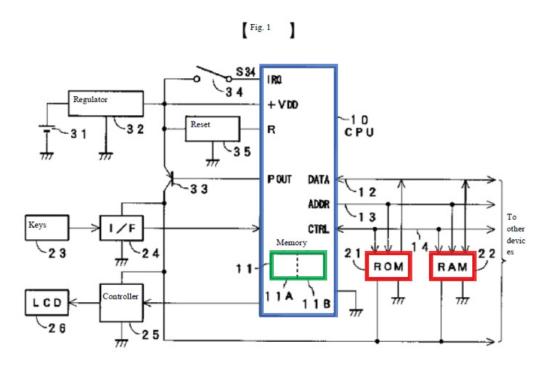

- 55. Irie discloses the preamble 7[a]. Irie discloses a mobile information terminal (shown in figure 1 below) which is "an apparatus" as claimed. Ex. 1002, ¶ 0010.

Ex. 1002, Fig. 1

- 56. The mobile information terminal "contains an instruction processing circuit, a main memory addressable by the instruction processing circuit and a cache memory" as claimed. First, the terminal includes CPU 10 which is "an instruction processing circuit" because it is a "circuit" that "executes...process[es]" such as routine 100 and routine 300 and provides "system control." Ex. 1002, ¶¶ 0009-0011, 0024, 0028, Fig. 1; see also id., claim 1 ("[a]n energy-saving circuit, comprising a CPU which controls operation"). Irie therefore discloses "an apparatus that contains an instruction processing circuit" as claimed.

- 57. Second, Irie discloses that its terminal includes a "*main memory*." The terminal contains a ROM 21 and a RAM 22, which are shown above in reproduced

- Figure 1. Ex. 1002, ¶ 0013, Fig. 1. Both ROM 21 and RAM 22 can be considered "a main memory" as claimed. Indeed, the '331 patent acknowledges that ROM and RAM are both types of "main memory." Ex. 1001, 2:65-3:2.

- Furthermore, in my opinion, ROM 21 is "a main memory" because it 58. "has programs for controlling the mobile information terminal," (Ex. 1002, ¶ 0013, Fig. 1) just as the main memory of the '331 patent holds instructions executed by its processor 14. See Ex. 1001, 2:27-34. Specifically, the '331 patent explains that "processor 14 executes programs of instructions that are retrieved from main memory 18." Id. Likewise, Irie discloses "a CPU which controls operation of predetermined circuits, [and] a ROM in which first and second programs which are executed by the CPU are written." Ex. 1002, ¶ 0009. My understanding is also supported by Shiraga (Ex. 1020) that describes an information processing apparatus that has a power saving method. Ex. 1020, ¶ 0002. Ex. 1020 states "In the information processing apparatus, it is generally necessary for CPU to fetch a command at a reset vector address immediately after the power is turned on. From this reason, the apparatus is provided with an inexpensive ROM (boot ROM) as a portion of the main memory." Id., ¶ 0009.

- 59. In addition to the '331 patent's express inclusion of ROM as a type of main memory, as I explain above, the RAM 22 of Irie also qualifies as "a main memory" because it "provides a work area and a stack area for the CPU 10." Ex.

1002, ¶ 0014. A POSA would have understood this is a typical characteristic of a "main memory." My understanding is supported by U.S. Patent 3,713,107 (Ex. 1025), which describes a "main memory" having a "work area" (Ex. 1025, 6:38-40, Moreover, the '331 patent explains the main memory supplies the instructions and/or data copied to the cache memory. The '331 patent states, "If the addressed instruction and/or data is not available in cache memory 16, cache memory forwards the address to *main memory 18*, which returns the instruction and/or data to cache memory 16. Cache memory 16 then supplies the instruction and/or data from main memory 18 to processor 14. Preferably, cache memory 16 also stores a copy of this instruction and/or data, for later use, when processor 14 uses the address again." Ex. 1001, 2:45-52. Irie also uses RAM 22 to supply program instructions to its cache memory 11. Irie reads "programs and tables ... into the memory 11 ... provided in the ROM 21." Ex. 1002, ¶ 0027. Irie does so by reading content from ROM 21 to "a temporary location," which "is any open space in RAM 22." Id., ¶ 0028. When "the program 200 ... is copied to the same temporary address [in RAM 22]...the area 11A in the memory 11 is used as cache memory." Id., ¶ 0031. In this way, "program 200 ... is sequentially copied to the cache area 11A." Id. Thus, Irie's RAM 22 supplies program instruction to its cache memory 11 just as the '331 patent's main memory 18 supplies instructions and/or data to its cache memory 16.

- 60. Hennessy 3rd also describes that a RAM is a type of main memory. For instance, Hennessy 3rd explains that "[t]he main memory of virtually every desktop or server computer sold since 1975 is composed of semiconductor DRAMs." Ex. 1023, 454. A DRAM is a dynamic RAM. *Id.*, 455; Ex. 1019, 541. Indeed, Hennessy 2nd explains that "Main memory is implemented from DRAM (dynamic random access memory), while levels closer to the CPU (caches) use SRAM (static random access memory)." Ex. 1019, 541. Therefore, both ROM 21 and RAM 22 are typical examples of *main memory*, and Irie discloses "*an apparatus*" that contains "*a main memory*" as claimed.

- 61. Irie also discloses that ROM 21 (the claimed "main memory") is "addressable" by CPU 10 (the claimed "instruction processing circuit") as claimed. This is because CPU 10 executes a program routine 300, which copies a program from ROM 21 to cache memory 11. Ex. 1002, ¶ 0028. By executing routine 300, CPU 10 determines a starting address location in ROM 21 storing instruction content for a program, reads this content, and copies it to a temporary location in RAM 22. Id.. This content is then moved from the temporary location in RAM 22 to cache memory 11. Id., ¶¶ 0027-0031. Then, CPU 10 determines a subsequent address location in ROM 21 where further program content is stored, reads the content stored at this subsequent address location, copies it to the same temporary location in RAM 22, and this content is moved from the temporary location in RAM 22 to cache

- memory 11. *Id.*, ¶¶ 0028-0029. These steps continue for each subsequent address until a final address location holding content in ROM 21 is reached. *Id.*, ¶¶ 0029-0030. Therefore, because CPU 10 determines address locations of ROM 21 to read content stored at these address locations, ROM 21 (the claimed "*main memory*") is "*addressable*" by CPU 10 (the claimed "*instruction processing circuit*"). *Id.*, ¶¶ 0027-0031, Fig. 4.

- 62. RAM 22, which can also be considered the claimed "main memory," is "addressable" by CPU 10 (the claimed "instruction processing circuit"). RAM 22 "provides a work area and a stack area for CPU 10," and a POSA would have understood that a "work area" refers to a range of memory addresses in RAM 22 to which CPU 10 can read and write data directly. Ex. 1002, ¶ 0014; id., ¶ 0011. My understanding is supported by U.S. Patent No. 3,713,107 (Ex. 1025), which describes a "main memory" having a "work area…used to operate as an input buffer for storage of raw data to be processed" (Ex. 1025, 6:38-40, Fig. 7).

- 63. Thus, because CPU 10 reads and writes to these memory addresses of RAM 22 directly, RAM 22 (which can be considered the claimed "main memory") is "addressable" by CPU 10 (the claimed "instruction processing circuit").

- 64. I also note that Hennessy 2nd states that "[o]ccasionally, people call the processor the CPU." Ex. 1019, 14. Figure 5.1 shows the main components of a million instructions per second (MIPS) implemented processor and that the

processor directly supplies addresses to both data memory and instruction memory. *Id.*, 338-340, Fig. 5.1, 344-345, G-7. This disclosure confirms the understanding a POSA would have had regarding how processors and memory, including main memory, interact, and how main memory is addressable by a processor (CPU). Thus, when viewing Irie, a POSA would have understood that the ROM 21 and RAM 22 are addressable by CPU 10.

- 65. Thus, Irie discloses "a main memory addressable by the instruction processing circuit" as claimed.

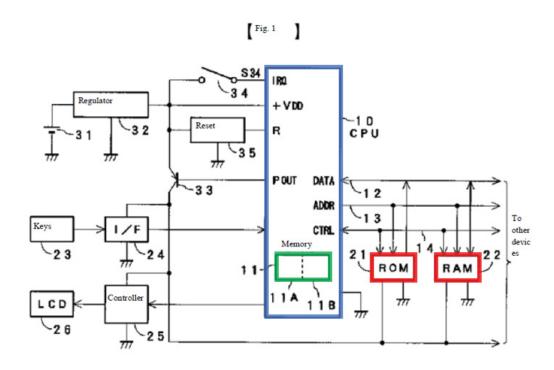

- 66. Irie's mobile information terminal (the claimed "apparatus") also contains cache memory 11, which is "a cache memory" as claimed. Ex. 1002,  $\P$  0012. I provide figure 1 below as reference.

# Ex. 1002, Fig. 1

- 67. Irie explains that "CPU 10" of the mobile information terminal "has a cache memory 11." Ex. 1002, ¶ 0012; see also id., claim 3. Thus, Irie discloses "an apparatus" (Irie's mobile information terminal) contains "a cache memory" as claimed. Irie also discloses "[a] method of operating" its terminal (the claimed "apparatus") as claimed because the reference explains that when a power switch 34 is in an "on" position, the terminal (claimed "apparatus") is operated in a "normal operating mode." Ex. 1002, ¶¶ 0022-0023. When power switch 34 is moved from "on to off," the terminal (claimed "apparatus") operates by executing routines. Id., ¶¶ 0013-0014, 0024, 0028, 0033, Figs. 2-4. Irie therefore discloses "[a] method of operating an apparatus" as claimed.

- 68. Accordingly, Irie discloses the preamble 7[a]

- b) 7[b]: "using the cache memory and the main memory in a normal operating mode . . ."

- 69. Irie discloses limitation 7[b]. To begin with, Irie describes a CPU 10 (having an external memory and cache) that can operate in a "normal operating mode." Ex. 1002, ¶ 0011 ("CPU 10...[has] an energy-saving mechanism which allows **operation in normal mode**..."), ¶¶ 0012-13; see also id., claim 1, Abstract.

- 70. In that normal operating mode, Irie discloses "using" cache memory 11 (the claimed "cache memory") in the normal operating mode (the claimed "normal operating mode"). Cache memory 11 is used in the normal operating mode

according to a "first mode" where the "entire area (all addresses) of memory 11 can be used as cache memory." Ex. 1002, ¶¶ 0012, 0022-0025, 0037, 0041. Specifically, Irie explains that when "the mobile information terminal is in **normal operating mode**... the cache memory 11 is set to a first operating mode" and "both areas 11A and 11B operate as cache memory." Id., ¶ 0023. Irie thus discloses "using" cache memory 11 in a "normal operating mode."

(either of which can be the claimed "main memory" as I explain above) in a normal operating mode. Irie states that "in normal operating mode...the output voltage of the regulator circuit 32 is supplied to...memories 21 and 22," such that ROM 21 "has programs for controlling the mobile information terminal" (and "operates as a general purpose mask ROM"), while RAM 22 "provides a work area and a stack area for the CPU 10." *Id.*, ¶¶ 0013-0014, 0022. Irie further discloses that both memories are operational when CPU 10 is in a "normal mode," because "operating

voltage" is supplied to memories ROM 21 and RAM 22<sup>5</sup>; ROM 21 then stores program 100, which is executed, while RAM 22 is "enabled." *Id.*, ¶¶ 0037-0039; *see also id.*, claim 1 ("the CPU, when operating in the **normal operating mode**, has the switch element turned on by the CPU, **supplying voltage** from the power source through the switch element **to the ROM** and the predetermined circuits **as operating voltage** . . . "). Irie thus discloses "using" ROM 21 and RAM 22 (the claimed "main memory") in a normal operating mode.

- 72. Accordingly, Irie discloses limitation 7[b].

- c) 7[c]: "... to cache in cache memory a part of data and/or instructions that the instruction processing circuit addresses in the main memory during execution and to substitute cached data and/or instructions when the instruction processing circuit addresses the data and/or instructions in the main memory;"

- 73. Irie in view of AAPA teaches limitation 7[c].

<sup>&</sup>lt;sup>5</sup> Although Irie states "operating voltage is supplied to the peripheral devices such as the circuits 24 and 25 **in** the memories 21 and 22, etc.," Figure 1 shows that circuits 24 and 25 are separate circuits not located "**in**" memories 21 and 22. Ex. 1002, ¶ 0038, Fig. 1. The word "**in**" should thus be read as "**and**," as confirmed by paragraph 0022 of Irie, which states that "voltage...is supplied to the circuits 24 and 25 **and** the memories 21 and 22, etc...." Ex. 1002, ¶ 0022.

- 74. Irie discloses using its cache memory 11, ROM 21, and RAM 22 in a normal operating mode (claimed "using the cache memory and the main memory in a normal operating mode"). I explain this above in section IX.A.1.b (limitation 7[b]).

- 75. Also, "cache memory 11 is set to a first operating mode, in which both areas 11A and 11B operate as cache memory." Ex. 1002, ¶¶ 0022-0023. This setting improves processing speed of CPU 10. *Id*.

- A conventional and well known implementation of cache memory 76. functionality is described by AAPA. In my opinion, a POSA would have implemented this cache functionality of AAPA into Irie's cache memory 11. AAPA states that "known apparatuses that contain a computer processor and a main memory with data and/or instructions for use by the processor are often provided with a cache memory in order to speed up execution" and that in this known apparatus, "[t]he cache memory temporarily stores copies of part of the data and/or instructions that the processor has addressed in main memory, so that it can be retrieved given its main memory address." Ex. 1001, 1:34-40; see also id., 2:35-52. Thus, AAPA discloses using known cache memory and main memory "to cache in cache memory a part of data and/or instructions that the instruction processing circuit addresses in the main memory during execution" as claimed because AAPA describes how known caches store copies of part of data and/or

instructions that a processor addressed in main memory to speed up execution. *Id.*, 1:34-40.

and/or instructions again, the cache memory substitutes the cached data and/or instructions for the data and/or instructions from main memory." Ex. 1001, 1:37-43. This disclosure therefore means that AAPA discloses "to substitute cached data and/or instructions" as claimed, and that the substituting of AAPA occurs when the processor addresses data and/or instructions in main memory that were previously addressed and temporarily stored in the cache (claimed "when the instruction processing circuit addresses the data and/or instructions in the main memory"). Id.. Thus, AAPA discloses "to substitute cached data and/or instructions when the instruction processing circuit addresses the data and/or instructions when the instruction processing circuit addresses the data and/or instructions in the main memory" as claimed. Id.

#### 1. Constructions from District Court

78. I understand that in the corresponding district court litigation, the parties have proposed constructions of "data and/or instructions that the instruction processing circuit addresses in the main memory" and "when the instruction processing circuit addresses the data and/or instructions in the main memory." In my opinion, Irie and the AAPA satisfy each party's constructions proposed for these terms in the related district court litigation.

- 79. I understand that Petitioner proposed that "data and/or instructions that the instruction processing circuit addresses in the main memory" means "data and/or instructions whose main memory address the instruction processing circuit outputs on its address/data interface" and "when the instruction processing circuit addresses the data and/or instructions in the main memory" means "when the instruction processing circuit outputs the main memory address of the data and/or instructions on its address/data interface" in the district court litigation. Ex. 1006, Exhibit A, 3. The constructions proposed by the Petitioner in the district court are satisfied by Irie in view of AAPA.

- 80. Irie's CPU 10 uses each "address in the ROM 21" ("main memory") that stores the content of program 200 ("data and/or instructions") when reading program 200 from ROM 21 ("main memory") and copying the program into cache memory 11. Ex. 1002, ¶ 0028. I note that paragraph 0028 of Irie refers to a "Program 20," but I understood this to be a typographical error for "program 200" which is used in Irie. Ex. 1002, ¶ 0027, 0029-0031, 0033, 0039.

- 81. Moreover, Irie explains that "CPU 10 ["instruction processing circuit"] is connected to ... ROM 21 ... ["main memory"] via data bus 12, address bus 13, and control bus 14." *Id.*, ¶¶ 0012-0013, Fig. 1. A POSA would have therefore understood that when the content of program 200 ("data and/or instructions") are copied from ROM 21 to cache memory 11, CPU 10 ("instruction processing")

circuit") addresses program 200 in ROM 21 ("main memory") by outputting each address of ROM 21 ("main memory address") corresponding to each portion of the instruction content of program 200 on address bus 13 (where address bus 13 is an address/data interface of CPU 10) such that the address is provided to ROM 21. Id., ¶ 0012-0013, Fig. 1. In my opinion, AAPA confirms this understanding that a POSA would have had of Irie because it describes "conventional cache memory" operations in which a processor in need of an instruction and/or data "outputs the address with which the instruction and/or data is addressed in main memory on its address/data interface." Ex. 1001, 2:35-39. And a POSA would have had this understanding because the address bus 13 acts as an address interface between CPU 10 and ROM 21, and therefore provides the medium by which addresses in ROM 21 required by CPU 10 are output from CPU 10. Id. See also, Ex. 1002, ¶ 0012-0013, Fig. 1

82. I understand that Patent Owner proposed "data and/or instructions that the instruction processing circuit addresses in the main memory" means "data and/or instructions that the instruction processing circuit identifies using addresses with which they can be retrieved from main memory" and "when the instruction processing circuit addresses the data and/or instructions in the main memory" means "when the instruction processing circuit identifies the data and/or instructions using addresses with which they can be retrieved from main memory" in the district court

U.S. Patent No. 7,523,331 Claim 7

litigation. *VLSI Tech. LLC v. Intel Corp.*, No. 18-966 (D. Del.), (Ex. 1006), Joint Claim Construction Chart, Exhibit A, 3. The Patent Owner's constructions in the district court litigation are also satisfied by Irie in view of AAPA.

- 83. As I discuss above, CPU 10 uses each "address in the ROM 21" ("main memory") that stores the content of program 200 ("data and/or instructions") when reading program 200 from ROM 21 ("main memory") and copying the program into cache memory 11. Ex. 1002, ¶ 0028. A POSA would have therefore understood that CPU 10 identifies each portion of the content of program 200 ("data and/or instructions") using its respective "address in the ROM 21." Id. This is because each address of ROM 21 corresponds to each instruction of program 200 and is used to copy the instruction stored at each address into cache memory 11. Id. Furthermore, in my opinion, a POSA would have further understood that because each address of ROM 21 is used to copy the content stored at that address into cache memory 11, each ROM 21 address can be used to retrieve its respective instruction content from ROM 21 ("main memory"). Id.

- 84. AAPA also satisfies the constructions proposed by Patent Owner in the district court litigation, as it describes that instructions and/or data are retrieved from main memory "given its main memory address" when the processor addresses the data and/or instructions in main memory. Ex. 1001, 1:34-40. Thus, a POSA would have understood that the AAPA processor uses "its main memory address" to

identify the data and/or instructions it retrieves from main memory. *Id.* This POSA understanding of how a processor uses addresses to identify information (*i.e.*, data and/or instructions) it retrieves from main memory is corroborated by Hennessy 2nd, which explains "[t]o access a word in memory, the instruction must supply the memory address...the address acting as the index to that [memory] array." Ex. 1019, 111. Hennessy 2nd further provides an example using Figure 3.2, reproduced below.

FIGURE 3.2 Memory addresses and contents of memory at those locations. This is a simplification of the MIPS addressing; Figure 3.3 shows MIPS addressing for sequential words in memory.

85. Hennessy 2nd explains that in Figure 3.2, the data value "10" is present at address "2" in memory. Ex. 1019, 111, Fig. 3.2. Thus, Ex. 1019 states that "the value of Memory[2] is 10." *Id.* Accordingly, Ex. 1019 shows how a memory address—used by a processor to access the information at the address—identifies the information stored at that address, and corroborates the understanding of POSA that a processor uses addresses to identify the information (*i.e.*, the data and/or instructions) it retrieves from main memory. *Id.*

- 86. As I explain above, AAPA describes known functionality of cache memory, and a POSA would have understood that the cache functionality of AAPA would have been implemented by Irie's cache memory 11. Implementing this functionality of AAPA with the addressing performed by Irie (as described in this section) would have been well within the knowledge of a POSA, and a POSA would have been motivated to combine Irie and AAPA for the reasons noted below.

- 87. Thus, Irie in view of AAPA teaches limitation 7[c].

## 2. **Motivation to Combine**

88. The combination of Irie and AAPA simply uses prior art cache memory elements according to known methods and would have yielded predictable results: namely, a cache memory that caches information. Thus, a POSA would have been motivated to combine the references. As I explain above, Irie in view of AAPA teaches each element claimed in limitation 7[c]. *See* Section IX.A.1.c. I also note that a POSA would have combined the elements of Irie and AAPA by known methods and each element performs the same function in the combination as it does separately. This is because Irie describes the following system having the following components: CPU 10, cache memory 11, and main memory (ROM 21 and RAM 22); Irie also describes that cache memory 11 operates in a normal operating mode and interacts with these other parts; Irie further describes the addressing of instruction content in main memory. *See Section IX.A.1.a.*, IX.A.1.b., IX.A.1.c.

(limitations 7[a], 7[b], 7[c]). Likewise, AAPA describes a known system that includes a processor, cache memory, and main memory, and that the cache memory interacts with the processor and main memory. Ex. 1001, 1:34-44. A combination of Irie with AAPA would have made Irie's cache memory 11 operate like AAPA's cache in Irie's normal operating mode. *Id.*; Ex. 1002, ¶¶ 0009-0013. The combination would have merely involved incorporating AAPA's known cache functionality into Irie's cache memory 11. Id. In my opinion, this combination would have been performed by known, conventional methods of memory design. This is because Irie's and AAPA's hardware (cache memory) perform the same function (caching); the adjustment would simply provide that the way Irie's cache memory 11 caches information would be adjusted. The systems of Irie and AAPA both include main memory and a processor that function with cache memory. Ex. 1001, 1:34-42, 2:35-52; Ex. 1002, ¶¶ 0009-0013. Thus, a POSA would have readily appreciated, and been readily able to implement, operating Irie's cache memory 11 like AAPA's cache memory in the normal operating mode. *Id.* I also note that Irie's cache memory 11 would still function when combined with AAPA in the same way that it does separately. Indeed, cache memory 11 would still cache information and interact with a processor (CPU 10) and a main memory (ROM 21 or RAM 22). Ex.  $1002, \P\P 0009-0013.$

U.S. Patent No. 7,523,331 Claim 7

- A POSA would have further recognized that combining Irie and AAPA 89. would have yielded predictable results. As I explain above, cache memory 11 operates like AAPA's conventional and known cache memory in the combination. Predictable results occur from the combination and the combination has a reasonable likelihood of success. Irie's system would have addressed information in ROM 21 using address bus 13, and cache memory 11 would have operated to cache information and perform information caching like AAPA describes in normal operation. The combination of Irie and AAPA would have provided a cache that operates in a normal operating mode to "cache in cache memory a part of data and/or instructions that the instruction processing circuit addresses in the main memory during execution and to substitute cached data and/or instructions when the instruction processing circuit addresses the data and/or instructions in the main memory" as claimed. I note that the combination of Irie and AAPA also describes this claimed recitation under each party's constructions.

- 90. A POSA would have also combined Irie and AAPA because the combination is use of a known technique to improve similar devices in the same way. As I explain above, Irie describes a base device that describes limitation 7[c], and AAPA describes a device that includes a processor, cache memory, and main memory the same components as Irie. *See* IX.A.1.c. The Irie and AAPA devices are therefore comparable, and also compatible. Moreover, AAPA teaches that its

cache memory increases execution speed, which is an improvement that Irie recognizes and seeks. Ex. 1001, 1:34-37; Ex. 1002, ¶ 0023.

91. Indeed, recognizable benefits are associated with the combination of Irie and AAPA, and these benefits show that a POSA would have been motivated to combine Irie and AAPA. A POSA would have been motivated to combine Irie and AAPA to at least obtain the benefit of increased execution speed. Irie explains that its cache memory is used during the execution of program routines to receive information addressed from ROM 21 ("main memory"). Ex. 1002, ¶¶ 0011-0014, 0024-0032. AAPA similarly explains that "known apparatuses that contain a computer processor and a main memory with data and/or instructions for use by the processor are often provided with a cache memory in order to speed up execution." Ex. 1001, 1:34-37. Therefore, operating Irie's cache memory like AAPA's known cache would have provided a beneficial increase in execution speed, which would have caused Irie's cache to receive information from ROM 21 faster and improved the functionality of Irie's mobile terminal. Ex. 1001, 1:34-37; Ex. 1002, ¶¶ 0011-0014, 0023-0032. Increasing execution speed is a known design goal for memory systems in general, and in particular, cache memory, and a POSA would have wanted to obtain this design goal. For instance, Hennessy 2nd explains that in cache operation and locating blocks in cache, "speed is of the essence." Ex. 1019, 573. Ex. 1019 further explains that in memory systems, CPU speeds continue to

increase and to keep up, access times to memory must also improve. Ex. 1019, 618-621. Ex. 1023 also explains that speed was an important consideration in memory systems and that in hierarchical memories having various levels, "[t]he goal is to provide a memory system with...speed almost as fast as the fastest level." Ex. 1023, 390.

- 92. Therefore, a POSA would have been motivated to combine Irie and AAPA.

- 93. Accordingly, Irie in view of AAPA teaches teach limitation 7[c].

- d) 7[d]: "storing, in the main memory, a program of instructions for executing an interrupt function during operating in a low power operating mode,"

- 94. Irie discloses limitation 7[d]. First, it discloses "a program of instructions for executing an interrupt function during operating in a low power operating mode," by disclosing an "interrupt processing program" that is executed when CPU 10 is in an "energy-saving mode." Ex. 1002, ¶¶ 0027, 0036, 0037. The energy-saving mode is entered when power switch 34 is "turned from on to off," which causes a "signal S34" to move "from H level to L level," leading the CPU 10 to enter an "energy-saving mode" and "power to peripheral devices" such as "circuits 24 and 25 and the memories 21 and 22" to be "turned off." *Id.*, ¶¶ 0024, 0036; *see also id.*, ¶¶ 0025-0035. Then, when CPU is in "energy-saving mode," power switch 34 can be "turned from off to on," moving signal S34 "from L level to

H level," to initiate a return to the normal operating mode. *Id.*, ¶ 0037. "When this [change in signal S34] happens, the CPU 10 is interrupted, and the interrupt program...is executed." *Id.* Irie thus discloses a "program of instructions for executing an interrupt function" because it describes an interrupt processing program executed when CPU 10 is in its energy-saving ("low power operating") mode.

- 95. Irie discloses "storing" this program of instructions "in the main memory" in both ROM 21 and RAM 22 (either of which can be the claimed "main memory"). Irie states that "programs"—including the interrupt processing program are "provided in the ROM 21." Ex. 1002, ¶ 0027. Irie then describes storing that program in RAM 22 because the program is transferred from ROM 21 into cache 11 using routine 300, which "copie[s]" it from addresses of ROM 21 to a temporary location in RAM 22, and thereafter to cache 11. *Id.*, ¶¶ 0027-0032, Figs. 2-4.

- 96. Accordingly, Irie discloses limitation 7[d].

- e) 7[e]: "wherein the interrupt program is stored at addresses in main memory that have been selected so that all instructions of the interrupt program can be stored together in the cache memory;"

- 97. Irie teaches limitation 7[e]. I first note limitation 7[d] recites "storing ... a program of instructions for executing an interrupt function during operating in a low power operating mode." Ex. 1001, 8:8-10. Claim 7 then recites "the interrupt program" in limitation 7[e]. *Id.*, 8:11. A POSA would understand that "the interrupt

program" refers to the previously recited "program of instructions for executing an interrupt function" in limitation 7[d] because the "program of instructions for executing an interrupt function" is the only "program" recited in the claim up to this point. See Ex. 1001, claim 7. The same is true for "instructions of the interrupt program" because the only "instructions" recited in the claim up to this point are the "instructions for executing an interrupt function." See id. Thus, a POSA would understand that "program of instructions for executing an interrupt function during operating in a low power mode", "the interrupt program", and "instructions of the interrupt program" all refer to the same program and the same instructions of that program that are executing in the low power operating mode. Ex. 1001, claim 7 ("executing the interrupt program from said at least part of the cache memory"). As I explain in Section IX.A.1.d (limitation 7[d]), Irie stores the interrupt processing program at addresses (claimed "program of instructions for executing an interrupt function") in ROM 21 and RAM 22 (each of claimed "main memory"). Ex. 1002, ¶¶ 0027-0028, 0032. Thus, Irie discloses "wherein the interrupt program is stored at addresses in main memory" as claimed in limitation 7[e].

98. Limitation 7[e] concludes by requiring "addresses in main memory that have been selected so that all instructions of the interrupt program can be stored together in the cache memory." As I explain in Section VI (Claim Construction), this term should have its plain meaning. The plain meaning of this term at least

includes addresses in main memory that have been selected so that all instructions of the interrupt program can be stored in a <u>single cache memory or a single part of cache memory at the same time</u>.

- 99. The interrupt processing program (claimed "program of instructions" / "interrupt program") of Irie is stored in ROM 21 and RAM 22 (each of claimed "main memory") so that the program can be copied to cache memory 11 by routine 300. Ex. 1002, ¶¶ 0024-0032, Figs. 2-4. As I previously explained, when executed, routine 300 performs the following process:

- CPU 10 determines a starting address location in ROM 21 storing the program instructions. *Id.*, ¶¶ 0028-0032, Fig. 4.

- CPU 10 then copies instructions at that address to a temporary location in RAM 22. *Id*.

- Instructions are next moved from the temporary location in RAM 22 to area 11A of cache memory 11. *Id.*, ¶¶ 0027-0031.

- CPU 10 then determines a subsequent address location in ROM 21 where further program instructions are stored by incrementing the address by 1, reads the content stored at this subsequent address location, copies it to the same temporary location in RAM 22, and the instructions are moved from the temporary location in RAM 22 to cache memory 11. *Id.*, ¶¶ 0028-0032.

• This process is continued until a final address location in ROM 21 is reached. *Id.*, ¶¶ 0029-0030.

100. The entirety of Irie's interrupt processing program, which interrupts CPU 10 from an energy-saving mode, is copied to cache memory 11 due to this copying of instruction content at these addresses. Ex. 1002, ¶¶ 0029-0037. Peripheral circuitry to Irie's mobile information terminal, ROM 21, and RAM 22 are turned off when CPU 10 is in the energy-saving mode, which means there is no other active memory for storing the interrupt processing program that is executed to interrupt CPU 10. Id., ¶¶ 0036-0037. Irie also notes that "the interrupt program [previously] copied to the cache area 11A [of cache memory 11] is executed" when switching CPU 10 out of the energy-saving mode. *Id.*, ¶ 0037. Thus, a POSA would have understood that the entire interrupt processing program (where "program of instructions", "interrupt program", and "instructions of the interrupt program" are all the same) would be stored in cache area 11A of cache memory 11, which is a single part of a single cache memory (stored together in the cache memory), at the same time. This is because there is no other active memory that can store the program. Irie discloses that the interrupt program is executed solely from cache memory 11, and in particular, area 11A of cache memory 11, without recourse to main memory ROM 21 or RAM 22. Id., ¶¶ 0029-0037. Because there is no recourse

to main memory, the only location where the interrupt program can be stored is in cache memory 11. *Id*.

101. In addition, a POSA would have understood that Irie expressly discloses "wherein the interrupt program is stored at addresses in main memory that have been selected so that" all instructions of Irie's interrupt processing program are stored together (as described above) in single cache memory 11 or a single part of cache memory (cache area 11A) at the same time. This is because Irie starts the process of copying the interrupt processing program, via routine 300, at the first address where the instructions of the interrupt processing program have been stored, namely, the starting address in ROM 21 (claimed "main memory") where the instructions of the interrupt processing program are stored. See Ex. 1002, ¶ 0028. Routine 300 then copies the instruction content at that address to a temporary location in RAM 22, and then copies the content from the temporary location to area 11A of cache memory 11, as I discuss above. *Id.*, ¶¶ 0028-0032, Figs. 2-4. The address in ROM 21 is next "incremented by 1", thereby identifying for copying the next address at which instruction content was stored, and the same process of copying instruction content occurs from this incremented address of ROM 21 to cache memory 11. *Id.*, ¶¶ 0028-0030. Route 300 repeats this process until content is copied from a final address of ROM 21 to cache memory 11. Id., ¶ 0030. Thus, in my opinion, Irie stores all of the instruction content of an interrupt processing

program at selected addresses that are the starting address, final address, and intervening addresses in ROM 21 (claimed "main memory") so that this content can be copied to and stored together in cache memory 11 at the same time via routine 300. Therefore, in my opinion, a POSA would understand that Irie describes "wherein the interrupt program is stored at addresses in main memory that have been selected so that" all instructions of Irie's interrupt processing program are stored together in cache memory 11 as claimed.

- f) 7[f]: "detecting that it is no longer necessary to operate in the normal operating mode;"

- 102. Irie discloses limitation 7[f].

- However, the '331 patent mentions U.S. Patent 5,784,628 ("Reneris," Ex. 1021), which I understand provides an example of "detecting" in the '331 patent. Similar to the '331 patent, Reneris describes a "method of reducing power consumption by a data processing apparatus" where the "apparatus switches to a low power mode in which most parts of the apparatus are powered down." Ex. 1021, 1:6-15. The low power mode in Reneris is initiated by a "power down condition" which is "detected" through "any detectable condition which indicates that the computer system should be placed in either a suspended or hibernated power state," such as a "user initiated" condition of "pressing of a suspend or hibernate key." Ex. 1021, 10:11-26. Reneris thus describes an example of "detect[ing]" a user-initiated condition (a pressing of

- a key). *Id.* Because the '331 patent expressly describes Reneris as a prior art method for reducing power consumption using a low power mode, and the '331 patent does not otherwise explain "detecting," a POSA would have understood that the claimed "detecting" encompasses Reneris's disclosure of detecting a power down condition.

- 104. In addition, Hamilton (Ex. 1022), which I have been informed and understand was cited by the Examiner during prosecution, confirms this understanding by listing "a user[] hitting [] a special keypad button" as a condition that causes the system to leave the "normal active mode" and enter an "active sleep mode" because it is no longer necessary to operate in the normal operating mode. Ex. 1022, 7:42-8:16. Hamilton explains that in the "active sleep mode, power consumption is conserved as compared to a normal active state; however, some degree of processing power is left available." *Id.*, 3:46-52.

- 105. Irie describes a similar mechanism for detecting that it is no longer necessary to operate in the normal operating mode. Irie states that power switch 34 is turned "from on to off" to send a signal to the CPU 10. Ex. 1002, ¶¶ 0018-0019, 0036-0037. It states that "power switch 34 does not directly turn the power to the CPU 10 or other circuits, etc., on or off," but rather, "supplies a signal S34 ... to the CPU 10." Id., ¶ 0019. The signal S34 then changes "from H level to L level" in response to the switch, and "when this happens, the CPU 10 recognizes this" and executes routine 100. Id., ¶ 0024. The routine 100 causes CPU 10 to exit the normal

operating mode and enter an energy-saving mode. *Id.*, ¶¶ 0025-0036. I also describe this process in Section IX.A.1.d (limitation 7[d]) above. This disclosure is similar to Reneris's "pressing of a suspend or hibernate key by the user" to indicate it is time to enter "either a suspended or hibernated power state," because Irie's switching of power switch 34 "from on to off" also indicates that it is "*no longer necessary*" to operate in its normal operating mode, and Irie's system recognizes signal S34 to switch to energy-saving mode. Ex. 1021, 10:11-26; Ex. 1002, ¶¶ 0018-0019, 0024-0036.

- 106. This parallel disclosure confirms that a POSA would have understood that Irie's recognition of signal S34 moving from high to low ("H level to L level") after a user switches power switch 34 to be the same kind of "detecting" as described by Reneris and Hamilton and claimed in the '331 patent.

- 107. Irie's "recognition" supplies the element the Applicant argued was missing from prior art during prosecution. During prosecution, the Applicant argued that in the '331 patent application, "the program of instructions is not loaded into the cache memory until it has been detected that it is no longer necessary to operate in the normal operating mode," such that "the decision threshold for loading the program of instructions is whether or not it is necessary to operate in the normal operating mode." Ex. 1011 (Amendment (11/06/07)), 6. In the prior art, on the other hand, Applicant argued that the "decision threshold for loading a program of

instructions ... into a loop cache (26) is whether or not all of the instructions will fit into the loop cache (26)"—not "whether or not it is necessary for the [prior art system] to operate in the normal operating mode." *Id.* The Applicant's statements are consistent with Reneris's description of "detecting," where the user decides to move to a "suspended or hibernated power state" (*i.e.*, decides that it is no longer necessary to operate in the normal operating mode) by "pressing of a suspend or hibernate key." Ex. 1021, 10:11-26. These prosecution history statements are also consistent with the Irie, which recognizes that signal S34 moves "from H level to L level" in response to a switch as a decision threshold for when it is not necessary to operate in the normal operating mode. Ex. 1002, ¶¶ 0024-0036; *see also* Ex. 1011 (Amendment (11/06/07)).

- 108. Irie therefore teaches "detecting that it is no longer necessary to operate in the normal operating mode" as claimed in limitation 7[f].

- g) 7[g]: "switching to the low power operating mode once it is detected that it is no longer necessary to operate in the normal operating mode, by loading the interrupt program into the cache memory from the main memory, wherein all instructions of the interrupt program are stored together in the cache memory;"

- 109. Irie teaches limitation 7[g]. As I already noted for limitation 7[f], Irie discloses "detect[ing] that it is no longer necessary to operate in the normal operating mode" because it discloses recognizing signal S34 by CPU 10. See Section IX.A.1.f (limitation 7[f]).

- 110. When this signal is recognized, routine 100 is executed to cause CPU 10 to switch from a normal operating mode to an energy-saving mode. Ex. 1002, ¶¶ 0024-0036; see also Sections IX.A.1.d (limitation 7[d]), IX.A.1.f (limitation 7[f]), supra. This energy-saving mode is the claimed "low power operating mode" because CPU 10 consumes less current and therefore power in that mode. Ex. 1002, ¶ 0036 (explaining that "the current consumed when the CPU 10 is [in] an energy-saving mode can be saved"); see also id., ¶ 0042. Thus, Irie performs "switching to the low power operating mode once it is detected that it is no longer necessary to operate in the normal operating mode" by executing routine 100 to enter the energy-saving mode when CPU 10 recognizes signal S34 going "from H level to L level." Id., ¶¶ 0024-0036.

- 111. Irie further discloses that switching to the energy-saving mode (the claimed "low power operating mode") is done "by loading the interrupt program into the cache memory from the main memory." Ex. 1002, ¶¶ 0024-0036.

Specifically, Irie explains that in step 106 of routine 100, "programs and tables which are needed for later processes are read into memory 11," and that routine 300 is executed to read and copy the program stored at starting address in ROM 21 to a temporary location in RAM 22, from which it is copied to cache memory 11.

Id., ¶¶ 0027-0031. The address is incremented by CPU 10 to copy the next bit of the program at the next location in ROM 21 to the same temporary location in

- RAM 22, before moving it to cache memory 11. *Id.*, ¶¶ 0028-0029. This loop continues until the final address location of the program in ROM 21 is reached. *Id.*, ¶¶ 0029-0030. The program moved from ROM 21 to cache 11 is an interrupt program. *Id.*, ¶ 0032. Irie thus discloses a "program of instructions for executing an interrupt function"/ "interrupt program," which is "load[ed]" from ROM 21 (claimed "main memory") to "cache area 11A" (claimed "cache memory") using routine 300. *Id.*, ¶¶ 0027, 0032.

- 112. As I explained in section IX.A.1.e (for limitation 7[e]), Irie discloses that the interrupt program is "stored at addresses in main memory that have been selected so that all instructions of the interrupt program can be stored together in the cache memory." Thus, when the interrupt program is loaded into the cache memory from main memory in Irie, "all instructions of the interrupt program are stored together in the cache memory."

- 113. Irie therefore teaches limitation 7[g].

- h) 7[h]: "[switching to the low power operating mode once it is detected that it is no longer necessary to operate in the normal operating mode, by]

deactivating the main memory to reduce power consumption, but keeping active at least a part of the cache memory, that is needed for retrieving the interrupt program and for executing the interrupt function;"

114. Irie discloses limitation 7[h]. As I discuss above in Section IX.A.1.g (limitation 7[g]), Irie discloses "switching to the low power operating mode once it

as claimed because Irie discloses switching a mobile information terminal from a normal operating mode to an energy-saving mode when it detects signal S34 changing "from H level to L level" in response to switch 34 being turned "from on to off." *Id.*, ¶¶ 0018-0019, 0024.

- 115. Irie further discloses that this switching is performed "by deactivating the main memory to reduce power consumption, but keeping active at least a part of the cache memory, that is needed for retrieving the interrupt program and for executing the interrupt function" as claimed.