Paper 26 Date: January 3, 2020

#### UNITED STATES PATENT AND TRADEMARK OFFICE

\_\_\_\_\_

### BEFORE THE PATENT TRIAL AND APPEAL BOARD

APPLE INC., Petitioner,

v.

QUALCOMM INCORPORATED, Patent Owner.

IPR2018-01315 IPR2018-01316 Patent 8,063,674 B2

Before TREVOR M. JEFFERSON, DANIEL J. GALLIGAN, and SCOTT B. HOWARD, *Administrative Patent Judges*.

HOWARD, Administrative Patent Judge.

JUDGMENT

Final Written Decision

Determining All Challenged Claims Unpatentable

35 U.S.C. § 318(a)

#### **INTRODUCTION**

In these *inter* partes reviews, instituted pursuant to 35 U.S.C. § 314, Apple Inc. ("Petitioner") challenges claims 1, 2, 5–9, 12, 13, and 16–22 ("the challenged claims") of U.S. Patent No. 8,063,674 B2 (Ex. 1001, "the '674 patent"), owned by Qualcomm Incorporated ("Patent Owner").

As explained in detail below, the references applied against the challenged claims are identical in each of the cases. A joint hearing was held for these cases. The parties rely on the same declarants submitting identical declarations in each case for testimonial evidence. Under these circumstances, we determine that a combined Final Decision will promote a just, speedy, and inexpensive resolution of these proceedings.

The Board has jurisdiction under 35 U.S.C. § 6(b). This Final Written Decision issues pursuant to 35 U.S.C. § 318(a). For the reasons that follow, we determine that Petitioner has shown by a preponderance of the evidence that the challenged claims are unpatentable.

### A. IPR2018-01315 Procedural History

Petitioner filed a Petition to institute an *inter partes* review of claims 1, 2, and 5–7 of the '674 patent pursuant to 35 U.S.C. §§ 311–319. Paper 2<sup>1</sup> ("Petition" or "Pet."). Patent Owner filed a Preliminary Response. Paper 6. We instituted an *inter partes* review of claims 1, 2, and 5–7 on all grounds of unpatentability alleged in the Petition. Paper 7 ("Institution Decision" or "Inst. Dec.").

<sup>&</sup>lt;sup>1</sup> Unless otherwise noted, all citations are to IPR2018-01315. We note that identical exhibits were filed in each of the proceedings.

IPR2018-01315, IPR2018-01316 Patent 8,063,674 B2

After institution of trial, Patent Owner filed a Response (Paper 12, "PO Resp."), Petitioner filed a Reply (Paper 16, "Pet. Reply"), and Patent Owner filed a Sur-reply (Paper 19, "PO Sur-reply").

A joint hearing for IPR2018-01315 and IPR2018-01316 was held on October 11, 2019. Paper 25 ("Tr.").

## B. IPR2018-01316 Procedural History

Petitioner filed a Petition to institute an *inter partes* review of claims 8, 9, 12, 13, and 16–22 of the '674 patent pursuant to 35 U.S.C. §§ 311–319. IPR2018-01316, Paper 2 ("1316 Pet."). Patent Owner filed a Patent Owner Preliminary Response. IPR2018-01316, Paper 6. We instituted an *inter partes* review of claims 8, 9, 12, 13, and 16–22 on all grounds of unpatentability alleged in the Petition. IPR2018-01318, Paper 7 ("1316 Inst. Dec.").

After institution of trial, Patent Owner filed a Response (IPR2018-01316, Paper 12, "1316 PO Resp."), Petitioner filed a Reply (IPR2018-01316, Paper 16, "1316 Pet. Reply"), and Patent Owner filed a Sur-reply (IPR2018-01316, Paper 19, "1316 PO Sur-reply").

A joint hearing for IPR2018-01315 and IPR2018-01316 was held on October 11, 2019. IPR2018-01316, Paper 25 ("Tr.").

## C. Real Party in Interest

Petitioner identified Apple, Inc. as the real party in interest. Pet. 64.

Patent Owner identified Qualcomm Incorporated as the real party in interest. Patent Owner's Mandatory Notices, Paper 3, 2; IPR2018-01315 Patent Owner's Mandatory Notices, Paper 3, 2.

### D. Related Proceedings

The parties identified the following patent litigation proceedings in which the '674 patent was asserted: *In re Certain Mobile Electronic Devices and Radio Frequency and Processing Components Thereof* (ITC Inv. No. 337-TA-1093) and *Qualcomm Inc. v. Apple Inc.*, Case No. 3:17-cv-02398 (S.D. Cal.). *Id.* at 64–65; Patent Owner's Mandatory Notices, Paper 3, 2.<sup>2</sup>

#### E. The '674 Patent

The '674 patent is titled "Multiple Supply-Voltage Power-Up/Down Detectors." Ex. 1001, code (54). According to the '674 patent, "many newer integrated circuit devices include dual power supplies: one lower-voltage power supply for the internally operating or core applications, and a second higher-voltage power supply for the I/O circuits and devices." *Id.* at 1:22–25.

The '674 patent further states that "[i]n order to facilitate communication between the core and I/O devices, level shifters are employed." *Id.* at 1:28–29. "Because the I/O devices are connected to the core devices through level shifters, problems may occur when the core devices are powered-down." *Id.* at 1:29–32. An example of such a problem described in the '674 patent is how stray currents while the core is powering down can cause the level shifters to "send a signal to the I/O devices for transmission" resulting in the I/O devices "transmit[ting] the erroneous signal into the external environment." *Id.* at 1:34–40.

<sup>&</sup>lt;sup>2</sup> According to Petitioner, the district court proceeding and the ITC investigation have been dismissed. Petitioner's Updated Mandatory Notices, Paper 15, 1.

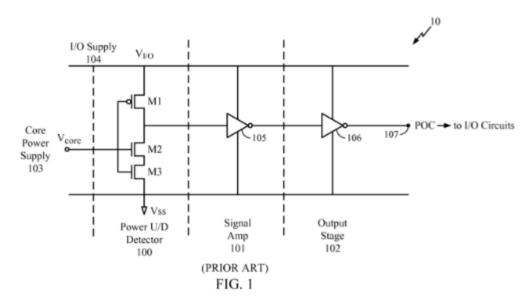

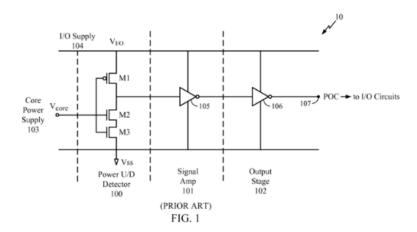

One prior art solution identified in the '674 patent is the use of "power-up/down detectors to generate a power-on/off-control (POC) signal internally [which] instructs the I/O devices when the core devices are shut down." Ex. 1001, 1:55–58. Figure 1 of the '674 patent is reproduced below.

Figure 1 "is a circuit diagram illustrating a conventional POC system for multiple supply voltage devices" which is identified as being prior art. *Id.* at 4:18–19, Fig. 1.

The '674 patent identifies a number of issues associated with the Figure 1 design. For example, when I/O power supply 104 is on and core power supply 103 is off, powering on the core power supply results in "a period in which all three transistors within power up/down detector 100 are on," resulting in a virtual short "to ground causing a significant amount of current to flow from I/O power supply 104 to ground." Ex. 1001, 2:21–29. "This 'glitch' current consumes unnecessary power." *Id.* at 2:29–30. Although the glitch current can be reduced by reducing the size of transistors M1-M3, such a reduction limits "the actual amount of current that can pass through the transistors" and reduces their switching speeds, which

"translates into less sensitivity in detecting power-up/down of core supply voltage 103 or longer processing time for power-up/down events." *Id.* at 2:31–39; *see also id.* at 2:63–3:11.

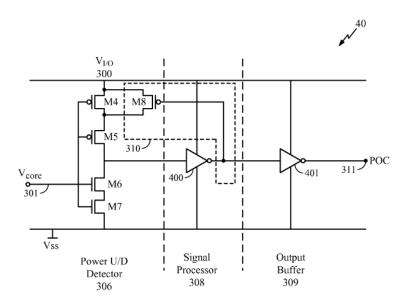

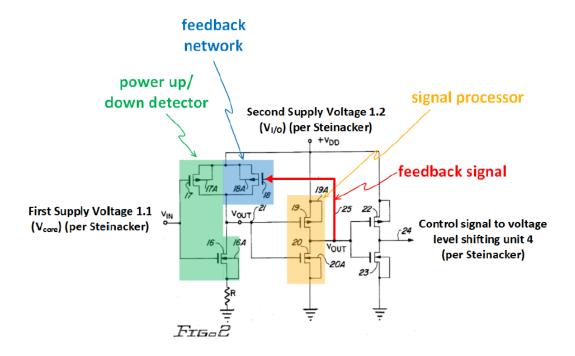

According to the '674 patent, these problems can be solved by using "one or more feedback circuits coupled to the up/down detector" that "are configured to provide feedback signals to adjust a current capacity of said up/down detector." Ex. 1001, 3:31–34. An example of such a feedback circuit is shown in Figure 4, reproduced below:

Figure 4 "is a circuit diagram illustrating another POC network configured according to the teachings of the present disclosure." *Id.* at 4:28–30. The '674 patent describes the operation of the feedback circuit in Figure 4 as follows:

The feedback network 310 comprises a transistor M8 connected in parallel to the transistor M4. The transistor M8 is also configured as a p-type transistor, such that when the feedback signal from the inverting amplifier 400 is high, the transistor M8 is switched off, and when the feedback signal is low, the transistor M8 is switched on. Thus, when the  $V_{core}$  301 is off, producing a high detection signal, the inverting amplifier

400 inverts that signal to a logic low which causes the transistor M8 to switch on. As the  $V_{core}$  301 is powered-on, the detection signal changes to a logic low, which changes the feedback signal from the inverting amplifier 400 to a logic high, which, in turn, turns the transistor M8 off. While the transistor M8 is off, the power up/down detector 306 has a decreased current capacity, i.e., smaller current will flow through the transistor M8 because of the amplified low signal. The voltage level caused by the V<sub>core</sub> 301 on the gate terminals of M4 and M5 could in some glitch or stray signal situations, cause leakage through M4 and M5. Because the feedback signal for the transistor M8 is received from the inverting amplifier 400, when the  $V_{core}$  301 powers-down, the feedback signal will switch quickly from a logic high to a logic low, which will then switch the transistor M8 on. Thus, in the circuit configuration depicted in FIG. 4, the power up/down detector 40 will detect the  $V_{core}$  301 powering down more quickly than the existing POC networks.

Id. at 6:4–28.

#### F. Illustrative Claim

Petitioner challenges claims 1, 2, and 5–9, 12, 13, and 16–22 of the '674 patent. Pet. 1; 1316 Pet. 1. Claim 1 is independent, is illustrative of the subject matter of the challenged claims, and reads as follows:

1. A multiple supply voltage device comprising: a core network operative at a first supply voltage; and

a control network coupled to said core network wherein said control network is configured to transmit a control signal, said control network comprising: an up/down (up/down) detector configured to detect a power state of said core network; processing circuitry coupled to said up/down detector and configured to generate said control signal based on said power state;

one or more feedback circuits coupled to said up/down detector, said one or more feedback circuits configured to

## IPR2018-01315, IPR2018-01316 Patent 8,063,674 B2

provide feedback signals to adjust a current capacity of said up/down detector;

at least one first transistor coupled to a second supply voltage, the at least one more first transistor being configured to switch on when said first supply voltage is powered down and to switch off when said first supply voltage is powered on;

at least one second transistor coupled in series with the at least one first transistor and coupled to said first supply voltage, the at least one second transistor being configured to switch on when said first supply voltage is powered on and to switch off when said first supply voltage is powered down;

at least one third transistor coupled in series between the at least one first transistor and the at least one second transistor.

Ex. 1001, 8:44–9:3 (the '674 patent).

#### G. Prior Art and Asserted Grounds

Petitioner asserts that claims 1, 2, and 5–9, 12, 13, and 16–22 are unpatentable on the following grounds:

| Claims Challenged            | 35 U.S.C. § | References/Basis                                                   |

|------------------------------|-------------|--------------------------------------------------------------------|

| 1, 2, 5–9, 12, 13, 16–<br>22 | $103(a)^3$  | Steinacker, <sup>4</sup> Doyle, <sup>5</sup> and Park <sup>6</sup> |

<sup>&</sup>lt;sup>3</sup> The Leahy-Smith America Invents Act ("AIA") included revisions to 35 U.S.C. §§ 102, 103 that became effective on March 16, 2013. Because the '674 patent issued from an application filed before March 16, 2013, we apply the pre-AIA versions of the statutory bases for unpatentability.

<sup>&</sup>lt;sup>4</sup> Steinacker, US 7,279,943 B2, issued Oct. 9, 2007 (Ex. 1005).

<sup>&</sup>lt;sup>5</sup> Doyle, US 4,717,836, issued Jan. 5, 1988 (Ex. 1006).

<sup>&</sup>lt;sup>6</sup> Park, J. C. & Mooney, V. J. (Nov. 2006). Sleepy Stack Leakage Reduction. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, *14*(11), 1250–1263 (Ex. 1007).

| <b>Claims Challenged</b>        | 35 U.S.C. § | References/Basis                            |

|---------------------------------|-------------|---------------------------------------------|

| 1, 2, 5, 6, 8, 9, 12, 13, 17–21 | 103(a)      | AAPA, <sup>7</sup> Majcherczak              |

| 7, 16, 22                       | 103(a)      | AAPA, Majcherczak,<br>Matthews <sup>8</sup> |

#### **ANALYSIS**

### A. Legal Principles

In Graham v. John Deere Co. of Kansas City, 383 U.S. 1 (1966), the Supreme Court set out a framework for assessing obviousness under 35 U.S.C. § 103 that requires consideration of four factors: (1) the "level of ordinary skill in the pertinent art," (2) the "scope and content of the prior art," (3) the "differences between the prior art and the claims at issue," and (4) "secondary considerations" of non-obviousness such as "commercial success, long-felt but unsolved needs, failure of others, etc." *Id.* at 17–18. "While the sequence of these questions might be reordered in any particular case," KSR Int'l Co. v. Teleflex Inc., 550 U.S. 398, 407 (2007), the Federal Circuit has "repeatedly emphasized that an obviousness inquiry requires examination of all four *Graham* factors and that an obviousness determination can be made only after consideration of each factor." Nike, Inc. v. Adidas AG, 812 F.3d 1326, 1335 (Fed. Cir. 2016), overruled on other grounds by Aqua Products, Inc. v. Matal, 872 F.3d 1290 (Fed. Cir. 2017) (en banc). We note that, with respect to the fourth Graham factor, the parties have not presented argument or evidence directed to secondary

<sup>&</sup>lt;sup>7</sup> Petitioner identifies Figure 1 and the text at column 1, line 22 through column 2, line 39 of the '674 patent as Applicant Admitted Prior Art. *See* Pet. 37, 43, 46.

<sup>&</sup>lt;sup>8</sup> Matthews, US 6,646,844 B1, issued Nov. 11, 2003 (Ex. 1009).

considerations of nonobviousness. The analysis below addresses the first three *Graham* factors.

## B. Level of Ordinary Skill in the Art

The level of ordinary skill in the art is "a prism or lens" through which we view the prior art and the claimed invention. *Okajima v. Bourdeau*, 261 F.3d 1350, 1355 (Fed. Cir. 2001). Factors pertinent to a determination of the "level of ordinary skill in the art include (1) educational level of the inventor; (2) type of problems encountered in the art; (3) prior art solutions to those problems; (4) rapidity with which innovations are made; (5) sophistication of the technology; and (6) educational level of workers active in the field." *Envtl. Designs, Ltd. v. Union Oil Co. of Cal.*, 713 F.2d 693, 696–697 (Fed. Cir. 1983) (citing *Orthopedic Equip. Co. v. All Orthopedic Appliances, Inc.*, 707 F.2d 1376, 1381–82 (Fed. Cir. 1983)). Not all such factors may be present in every case, and one or more of these or other factors may predominate in a particular case. *Id.* Moreover, "[t]hese factors are not exhaustive but are merely a guide to determining the level of ordinary skill in the art." *Daiichi Sankyo Co. Ltd, Inc. v. Apotex, Inc.*, 501 F.3d 1254, 1256 (Fed. Cir. 2007).

Dr. Horst testifies that a person having ordinary skill in the art would have had "at least an undergraduate degree in electrical engineering, or a related field, and three years of experience in circuit and system design." Ex. 1003 ¶ 33. Additionally, Dr. Horst testifies that "a person of ordinary skill with less than the amount of experience noted above could have had a correspondingly greater amount of educational training such a graduate degree in a related field." *Id*.

In our Institution Decision, "we adopt[ed] Dr. Horst's definition of the level of ordinary skill in the art, with the exception of the language 'at least' . . . ." Inst. Dec. 13; 1316 Inst. Dec. 13. Patent Owner agrees with our formulation, *see* PO Resp. 9; 1316 PO Resp. 9, and Petitioner did not address it in its Reply. *See generally* Pet. Reply; 1316 Pet. Reply.

Accordingly, we find on the record as a whole that a person of ordinary skill in the art would have an undergraduate degree in electrical engineering, or a related field, and three years of experience in circuit and system design. Additionally, a person of ordinary skill with less than the amount of experience noted above could have had a correspondingly greater amount of educational training such a graduate degree in a related field.

### C. Claim Construction

In this *inter partes* review, we construe claim terms in an unexpired patent according to their broadest reasonable construction in light of the specification of the patent in which they appear. 37 C.F.R. § 42.100(b) (2018). "Under a broadest reasonable interpretation, words of the claim must be given their plain meaning, unless such meaning is inconsistent with the specification and prosecution history." *Trivascular, Inc. v. Samuels*, 812 F.3d 1056, 1062 (Fed. Cir. 2016). In addition, the Board may not "construe claims during [an *inter partes* review] so broadly that its constructions are unreasonable under general claim construction principles." *Microsoft Corp.*

\_

<sup>&</sup>lt;sup>9</sup> We apply the district court claim construction standard to petitions filed on or after November 13, 2018. *See Changes to the Claim Construction Standard for Interpreting Claims in Trial Proceedings Before the Patent Trial and Appeal Board*, 83 Fed. Reg. 51340 (Oct. 11, 2018) (to be codified at 37 C.F.R. pt. 42). Because Petitioner filed its petitions before November 13, 2018 (*see* Pet.; 1316 Pet.), we apply the BRI standard.

v. Proxyconn, Inc., 789 F.3d 1292, 1298 (Fed. Cir. 2015) (emphasis omitted), overruled on other grounds by Aqua Products, Inc. v. Matal, 872 F.3d 1290 (Fed. Cir. 2017) (en banc). An inventor may provide a meaning for a term that is different from its ordinary meaning by defining the term in the specification with reasonable clarity, deliberateness, and precision. In re Paulsen, 30 F.3d 1475, 1480 (Fed. Cir. 1994).

Use of the word *means* in a claim gives rise to a rebuttable presumption that 35 U.S.C. § 112, sixth paragraph, analysis applies to interpret the claim. Williamson v. Citrix Online, LLC, 792 F.3d 1339, 1348 (Fed. Cir. 2015). Construing a means-plus-function claim term is a two-step process, wherein we first identify the claimed function and then determine what structure, if any, disclosed in the specification corresponds to the claimed function. Id. at 1348–51. Our rules specifically require that a petition for *inter partes* review identify how each challenged claim is to be construed, including identification of the corresponding structure for meansplus-function limitations. See 37 C.F.R. § 42.104(b)(3) (2017) ("Where the claim to be construed contains a means-plus-function . . . limitation as permitted under 35 U.S.C. 112[(6)], the construction of the claim must identify the specific portions of the specification that describe the structure, material, or acts corresponding to each claimed function."). 10 "[S]tructure disclosed in the specification is 'corresponding' structure only if the specification or prosecution history clearly links or associates that structure

\_

<sup>&</sup>lt;sup>10</sup> 37 C.F.R. § 42.104(b)(3) refers to § 112(f). Section 4(c) of the AIA redesignated 35 U.S.C. § 112, sixth paragraph as 35 U.S.C. § 112(f). Because the '674 patent has a filing date before the effective date of this provision of the AIA, we use the citation § 112, sixth paragraph.

to the function recited in the claim." *Med. Instrumentation & Diagnostics Corp. v. Elekta AB*, 344 F.3d 1205, 1210 (Fed. Cir. 2003) (quoting *B. Braun Med. Inc. v. Abbott Labs.*, 124 F.3d 1419, 1424 (Fed. Cir. 1997)).

Petitioner proposes a claim construction for "processing circuitry." Pet. 10; 1316 Pet. 5. Petitioner also contends that the claims contain several means-plus-function limitations. 1316 Pet. 6–9.

Patent Owner does not believe the term "processing circuitry" or the means-plus-function limitations need to be construed. PO Resp. 8; 1316 PO Resp. 8–9.

Having considered the evidence presented, we conclude that, with the exception of the means-plus-function limitations, no express claim construction of any term is necessary. *See Nidec Motor Corp. v. Zhongshan Broad Ocean Motor Co.*, 868 F.3d 1013, 1017 (Fed. Cir. 2017) (stating that "we need only construe those claim limitations 'that are in controversy, and only to the extent necessary to resolve the controversy" (quoting *Vivid Techs., Inc. v. Am. Sci. & Eng'g, Inc.*, 200 F.3d 795, 803 (Fed. Cir. 1999))).

With regard to the means-plus-function limitations, we are persuaded by Petitioner's identification of both the function set forth in the claim and the structure in the written description that is linked to the function, and adopt them as our own. *See* 1316 Pet. 6–9.

## D. Obviousness over AAPA in View of Majcherczak

# 1. Overview of AAPA

The '674 patent describes a prior art "power-up/down detector[] to generate a power-on/off-control (POC) signal internally." Ex. 1001, 1:55–57, Fig. 1. The prior art design is shown in Figure 1, reproduced below.

*Id.* at Fig. 1. "FIG. 1 is a circuit diagram illustrating a conventional POC system for multiple supply voltage devices" and is identified as prior art. *Id.* at 4:18–19, Fig. 1. According to the '674 patent, the POC "is made up of three functional blocks: power-up/down detector 100, signal amplifier 101, and output stage 102. Power-up/down detector 100 has PMOS transistor M1 and NMOS transistors M2-M3." *Id.* at 1:60–63.

## 2. Overview of Majcherczak

Majcherczak is titled "Power Supply Detection Device" and relates "to a power supply detection device for an integrated circuit using at least two power supply voltages." Ex. 1008, code (54), ¶ 1. Majcherczak describes a voltage detection device that detects when the core voltage is powered down or there is an excessively slow build-up of the voltage. Ex. 1008, code (57), ¶¶ 8–11.

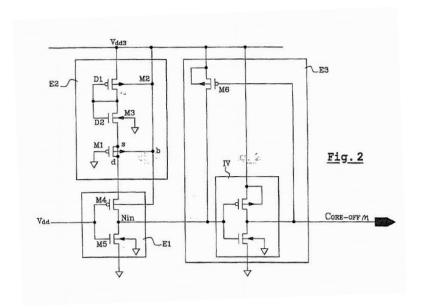

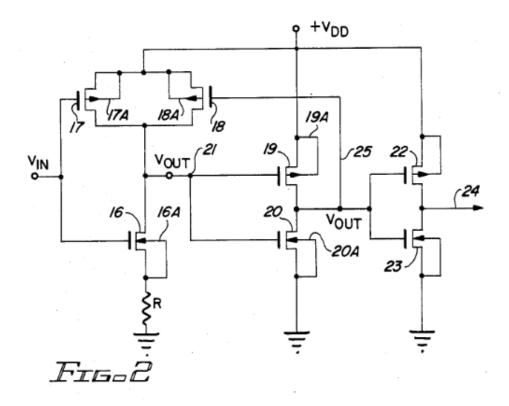

Figure 2 of Majcherczak is shown below.

Figure 2 shows a detection device "compris[ing] an output stage E3 following the input stage E1, to obtain the desired output levels for the inverse detection signal  $C_{ORE-OFFn}$ ." Ex. 1008, ¶¶ 35–37.

- 3. Using Applicant Admitted Prior Art During an Inter Partes Review

- a. Patent Owner's Arguments

Patent Owner argues that the grounds based on AAPA "are improper because the America Invents Act (AIA) does not permit *inter partes* review based on so-called [AAPA]." PO Resp. 17; *see also id.* at 17–20; PO Surreply 1–2.<sup>11</sup> Specifically, Patent Owner argues that "that *inter partes* review be available 'only on the basis of prior art consisting of patents or printed publications" and that "[p]ortions of the patent under review – which the Petitioner has characterized as the AAPA – cannot be considered 'prior art consisting of patents or printed publications' within the plain meaning of the

Although we only cite to IPR2018-01315 in this section, the same arguments were made by the parties in IPR2018-01316.

statute." PO Resp. 17–18 (quoting 35 U.S.C. § 311(b)). Patent Owner further argues that "the regulations governing inter partes review require that the petition 'specify where each element of the claim is found in the prior art patents or printed publications relied upon." *Id.* at 18 (quoting 37 C.F.R. § 42.104(b)(4)). According to Patent Owner, an admission in "the patent under review cannot reasonably be considered a 'prior art patent or printed publication' because the patent is not prior art to itself." PO Resp. 18.

Patent Owner also argues that the Board erred in the Institution Decision by "fail[ing] . . . to recognize other PTAB decisions that have correctly held that AAPA does *not* qualify as prior art under Section 311(b)." *Id.* at 18–19 (citing *LG Electronics, Inc. v. Core Wireless Licensing S.A.R.L.*, IPR2015-01987, Paper 7 at 18 (PTAB Mar. 24, 2016) (Institution Decision); *Sony Corp. v. Collabo Innovations, Inc.*, IPR2016-00940, Paper 7 at 30 (PTAB Oct. 24, 2016) (Institution Decision)).

Additionally, Patent Owner argues that "counsel for Petitioner agrees that AAPA is *not* eligible for *inter partes* review, as evidenced by arguments recently made by Petitioner's counsel in IPR2017-00126." PO Resp. 19 (citing Ex. 2004 (Patent Owner's Request for Rehearing in IPR2017-00126)); Ex. 2005 (Patent Owner's Response in IPR2017-00126)). Moreover, Patent Owner argues that Petitioner's Reply "does not disagree that AAPA is not proper prior art for IPR proceedings" and "never makes the affirmative statement that AAPA should be considered prior art in IPRs." PO Sur-reply 1 (citing Paper 16, 1–2).

Patent Owner further argues that *One World*, cited by Petitioner in the Reply, is distinguishable from the facts of this case. PO Sur-reply 1 n.1. Specifically, Patent Owner argues in *One World* "AAPA was relied on as a

secondary reference in an obviousness ground" but, "in the present case, Petitioner attempts to rely on AAPA as a primary reference." *Id.* (citing *One World Techs., Inc. v. Chamberlain Group, Inc.*, IPR2017-00126, Paper 56, 6 (PTAB Oct. 24, 2018) (Final Written Decision Public Version)).<sup>12</sup>

### b. Petitioner's Arguments

In the Petition, Petitioner did not address whether an *inter partes* review can be based on applicant admitted prior art. *See generally* Pet. In its Reply, Petitioner argues that "Patent Owner provides no basis upon which the Board should revisit the position expressed in the Institution Decision ('ID') that AAPA is an eligible ground for an IPR." Pet. Reply 1 (citing Inst. Dec. 21–22); *see also id.* at 1–2. According to Petitioner, "the Board diligently followed the logic articulated by the panel in IPR2017-

Additionally, Patent Owner argues that "this issue should be elevated for Precedential Opinion Panel review should the Board continue its improper consideration of the alleged AAPA." PO Resp. 19; *see also* Tr. 46:7–11. Patent Owner further argues that allowing a petitioner to rely on AAPA is unsound policy because "it dissuades patent applicants from including a background section in their patent applications." PO Sur-reply 2 n.2.

We do not address Patent Owner's argument that allowing *inter partes* review to consider applicant admitted prior art will dissuade patent applicants from including a background section in their patent applications. *See* PO Sur-reply 2 n.1. Such policy arguments regarding the impact of our decision on what patent applicants will do are beyond our purview. *See* 35 U.S.C. § 3(a)(2)(A) ("The Director shall be responsible for providing policy direction . . . for the Office . . . ."). If Patent Owner wishes the Precedential Opinion Panel to address the policy argument or any alleged inconsistency between PTAB panels, Patent Owner should follow the procedure set forth in Standard Operating Procedure 2, which can be found here: https://www.uspto.gov/sites/default/files/documents/ SOP2%20R10%20FINAL.pdf.

00126 [(*One World*)] regarding the availability of AAPA." Pet. Reply 1. Petitioner further argues that "the exact same language used in 35 U.S.C. § 311(b) to define eligible prior art has been previously held by the Federal Circuit [in the context of pre-AIA reexamination proceedings] to encompass AAPA." *Id.* at 1–2 (citation omitted). Therefore, according to Petitioner, "[b]ecause Patent Owner fails to advance any new arguments that were not otherwise addressed by the ID or by the panel's decisions in IPR2017-00126, Patent Owner's arguments regarding the availability of AAPA in IPRs should be dismissed." *Id.* at 2.

During the Oral Hearing, counsel for Petitioner explicitly stated that it is Petitioner's position that AAPA can be used in an *inter partes* review. Tr. 19:23–20:2.

### c. Our Analysis

We agree with Petitioner that an admission in the patent that is the subject to an *inter partes* review—that is, applicant admitted prior art—can be used to challenge claims in an *inter partes* review.

We begin our analysis with the statute. 35 U.S.C. § 311(b) provides that "[a] petitioner in an inter partes review may request to cancel as unpatentable 1 or more claims of a patent only on a ground that could be raised under section 102 or 103 and *only on the basis of prior art consisting of patents or printed publications.*" (emphasis added). Our regulations provide substantially the same limitation. *See* 37 C.F.R. § 42.104(b)(2) (2019) (requiring the petition to "identify . . . the *patents or printed publications* relied upon for each ground" (emphasis added)). The only requirement is that the "prior art consist[] of patents or printed publications."

Because AAPA is admitted to be prior art and is found in the '674 patent, it can be used to challenge the claims in an *inter partes* review.

This is consistent with prior use of identical statutory language. Prior to enactment of the Leahy-Smith America Invents Act ("AIA"), Congress used the phrase "prior art consisting of patents or printed publications" to exclusively identify the prior art that could be relied upon in reexamination proceedings. See 35 U.S.C. § 302 (1980) ("Any person . . . may file a request for reexamination . . . on the basis of any prior art cited under the provisions of section 301."); 35 U.S.C. § 301 (1980) (identifying "prior art consisting of patents or printed publications" as the only prior art that could be cited in reexamination proceedings). The Federal Circuit found that applicant admitted prior art could be cited and relied upon to support the Board's findings in such proceedings. See In re NTP, Inc., 654 F.3d 1279, 1304 (Fed. Cir. 2011). By finding that applicant admitted prior art could be used in combination with another reference in a pre-AIA reexamination proceeding in which only "prior art consisting of patents or printed publications" could be cited, the Federal Circuit has found, as we do above, that "prior art consisting of patents or publications" includes applicant admitted prior art. See NTP, 654 F.3d at 1304;13 see also In re Nomiva, 509 F.2d 566, 570–71 (CCPA 1975) (holding that applicant admitted prior art may "be considered as prior art in determining obviousness of their

\_

As Patent Owner pointed out during the Oral Hearing, the patent owner in *NTP* did not appeal the Board's decision to rely on the applicant admitted prior art. Tr. 41:8–12; *see also NTP*, 654 F.3d 1279. However, the Federal Circuit's decision is still, at a minimum, persuasive authority for the proposition that application admitted prior art is "prior art consisting of patents . . ."

improvement"). Because Congress used the same language—"prior art consisting of patents or printed publications"—in both the pre-AIA reexamination statute and the *inter partes* review statute, we give the same phrase the same meaning. *See also One World*, Paper 56 at 35–41 (holding that applicant admitted prior art can be used to challenge the claims in an *inter partes* review).

We do not agree with Patent Owner that, based on our rules, an admission in "the patent under review cannot reasonably be considered a "prior art patent or printed publication" because the patent is not prior art to itself." PO Resp. 18 (emphasis in original); see also id. ("Likewise, the regulations governing inter partes review require that the petition "specify where each element of the claim is found in the prior art patents or printed publications relied upon." (quoting 37 C.F.R. § 42.104(b)(4)) (emphasis in original)). However, the language in Rule 42.104(b)(4) cannot be read in isolation, as Patent Owner has done, to contradict the related statutory and regulatory provisions. Instead, it must be read in the context of the entire rule and the governing statute.

The quoted language in 42.104(b)(4) refers back to § 42.104(b)(2): The petition must state "[h]ow the construed claim is unpatentable under the *statutory grounds identified in paragraph* (*b*)(2) of this section." 37 C.F.R. § 42.104(b)(4) (2017) (emphasis added). According to § 42.104(b)(2), the petitioner must state the "*statutory grounds* under 35 U.S.C. 102 or 103 on which the challenge to the claim is based and *the patents or printed publications* relied upon for each ground." 37 C.F.R. § 42.104(b)(2) (2019) (emphases added). Thus, 42.104(b)(2) refers back to the statutory language which requires a challenge to be based "only on a ground that could be

raised under section 102 or 103 and only on the basis of *prior art consisting* of patents or printed publications." 35 U.S.C. § 311(b) (emphasis added). Therefore, considered as a whole, our rules simply reflect the limitations of the governing statute and do not impose any additional limitations that would exclude applicant admitted prior art.

We are not persuaded by the cases cited by Patent Owner—*LG Electronics* and *Sony*—that it is improper in this case for us to consider

AAPA in combination with Majcherczak, a prior art patent. First, both *LG Electronics* and *Sony* are routine decisions. Accordingly, they are not binding on us. *See* Standard Operating Procedure 2 (Revision 10), 3, *available at* https://www.uspto.gov/sites/default/files/documents/

SOP2%20R10%20FINAL.pdf ("Every decision other than a precedential decision by the Precedential Opinion Panel is, by default, a routine decision. A routine decision is binding in the case in which it is made, even if it is not designated as precedential or informative, but it is not otherwise binding authority.").

Second, because they do not address the Federal Circuit's *Nomiya* and *NTP* decisions, we do not find the reasoning of *LG Electronics* and *Sony* sufficiently persuasive. *See LG Elecs.*, Paper 7 at 18; *Sony*, Paper 7 at 30. In contrast, we find the reasoning in *One World* persuasive. The analysis in *One World* spans seven pages, discusses relevant case law—such as *Nomiya* and *NTP*—and addresses the statutory and regulatory language in depth. *One World*, Paper 56 at 35–41.<sup>14</sup>

We note that in *One World* the patent owner sought Precedential Opinion

Nor do we agree with Patent Owner that *One World* is distinguishable because the applicant admitted prior art was a secondary reference in that case but the primary reference in this proceeding. *See* PO Sur-reply 1 n.1. First, none of the reasoning in *One World* depended on whether the applicant admitted prior art was a primary or secondary reference. If applicant admitted prior art may be considered in an *inter partes* review, then it makes no difference if it is the primary reference or the secondary reference.

Second, Patent Owner has not cited any authority for the proposition that the order of references makes any difference in analyzing the patentability of a claim. In other contexts, a reviewing court has found changes to the order of references from A in view of B to B in view of A to be "of little consequence, and that basing arguments on them was 'attempting to make a mountain out of a mole-hill." *In re Bush*, 296 F.2d 491, 496 (CCPA 1961) (quoting *In re Cowles*, 156 F.2d 551, 554 (CCPA 1946)).

Accordingly, Petitioner can challenge the patentability of the claims in this *inter partes* review based on the combination of AAPA and Majcherczak.

#### 4. Claim 1

## a. Undisputed Limitations

Petitioner argues that the combination of AAPA and Majcherczak teaches all of the limitations recited in claim 1. *See* Pet. 37–56. Specifically, Petitioner argues a person of ordinary skill in the art would

challenge claims in an *inter partes* review. *See One World*, Paper 61; *One World*, Ex. 3005. That request was denied. *One World*, Paper 63.

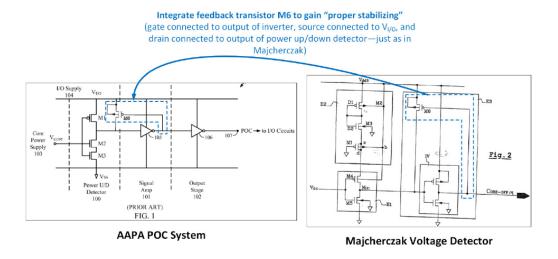

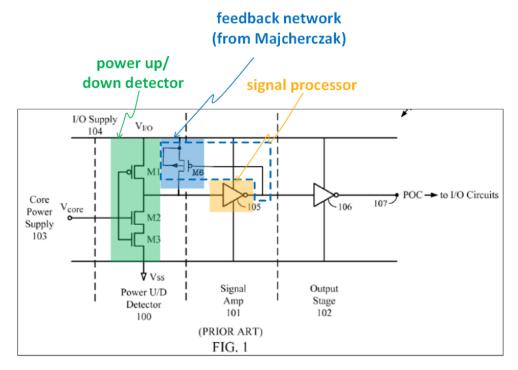

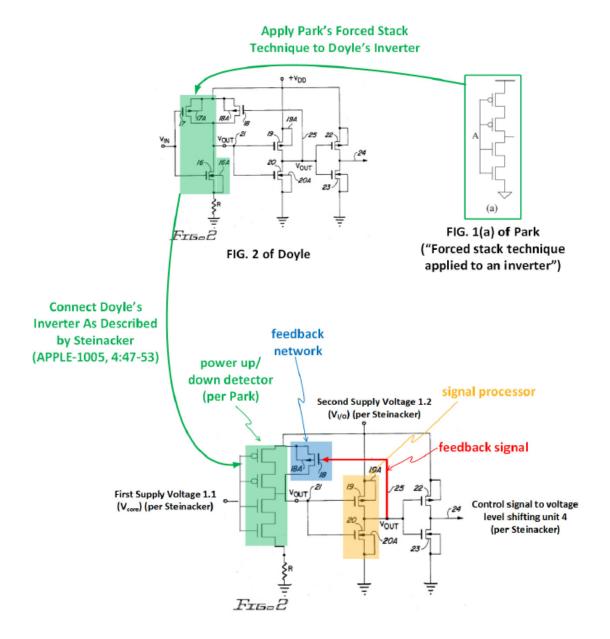

have combined the feedback circuit of Majcherczak with the POC described in AAPA as shown in the annotated figure reproduced below.

Pet. 44. The figure reproduced above shows Majcherczak's Figure 2 annotated by Petitioner (right) and a version of Figure 1 of the '674 patent (AAPA) modified by Petitioner to integrate the feedback transistor M6 from Majcherczak's Figure 2 (left). *Id.* Petitioner also provides a differently annotated version of its proposed combination as reproduced below.

AAPA + Majcherczak POC System

Pet. 50. The figure above shows what Petitioner contends is the combination of the feedback network of Majcherczak with the POC of AAPA. *Id.* Petitioner's annotations show what Petitioner argues is the power up/down detector in green, the signal processor in yellow, and the feedback network from Majcherczak in blue. *Id.*

Petitioner argues that AAPA in combination with Majcherczak teaches "[a] multiple supply voltage device" as recited in claim 1. Pet. 46. According to Petitioner, "AAPA describes that the prior art POC system 10 is useful in 'newer integrated circuit devices include dual power supplies: one lower-voltage power supply for the internally operating or core applications, and a second higher-voltage power supply for the I/O circuits and devices." *Id.* (quoting Ex. 1001, 1:22–25).

Petitioner also argues that AAPA in combination with Majcherczak teaches "a core network operative at a first supply voltage" as recited in claim 1. Pet. 46–47. Specifically, Petitioner argues AAPA includes power up/down detector 100 which is connected to the core power supply, which is a "lower-voltage power supply for the internally operating or core applications." *Id.* (citing Ex. 1001, 1:22–25, 1:60–64).

Petitioner further argues that AAPA in combination with Majcherczak teaches "a control network coupled to said core network wherein said control network is configured to transmit a control signal" as recited in claim 1. Pet. 47. Specifically, Petitioner argues "[t]he prior art power-on/off-control (POC) system 10 is a control network coupled to said core network (via core power supply V<sub>core</sub>), and the POC system 10 is configured to transmit a power-on/off-control (POC) signal 107." *Id.* (citing Ex. 1001, 1:55–58, 1:65–2:13).

Petitioner also argues that AAPA in combination with Majcherczak teaches "said control network comprising: an up/down (up/down) detector configured to detect a power state of said core network; processing circuitry coupled to said up/down detector and configured to generate said control signal based on said power state" as recited in claim 1. *Id.* at 48–49. Specifically, Petitioner directs us to a comparison of Figure 4 of the '674 patent and the combination of AAPA and Majcherczak, both of which show a power/up down detector and a signal amplifier portion. Pet. 48. Petitioner further argues that "[t]he signal amplifier 101 and output stage 102 are processing circuitry coupled to said up/down detector and configured to generate the power-on/off-control (POC) signal 107 based on said power state." *Id.* at 49.

Petitioner argues the combination of AAPA and Majcherczak teaches "one or more feedback circuits coupled to said up/down detector, said one or more feedback circuits configured to provide feedback signals to adjust a current capacity of said up/ down detector" as recited in claim 1.

See Pet. 49–52. Specifically, Petitioner argues that, when the teachings of AAPA and Majcherczak are combined as shown in the figure reproduced above, "the feedback transistor M6 is a feedback circuit coupled to the up/down detector 100 via its output." Pet. 51 (citing Ex. 1003 ¶ 141); see also Pet. 51–52 (citing Ex. 1003 ¶ 142–143). That is, according to Petitioner, "when both transistors M1 and M6 are 'on' (i.e., V<sub>core</sub> is off), the transistor M6 increases the current capacity of the power up/down detector 100" but "when both transistors M1 and M6 are 'off' (i.e., V<sub>core</sub> is on), the transistor M6 decreases the current capacity of the power up/down detector 100." Pet. 51–52 (citing Ex. 1003 ¶¶ 142–143).

Petitioner also argues that AAPA in combination with Majcherczak teaches "at least one first transistor coupled to a second supply voltage, the at least one more first transistor being configured to switch on when said first supply voltage is powered down and to switch off when said first supply voltage is powered on" as recited in claim 1. *See* Pet. 52–53. More specifically, Petitioner argues M1—a first transistor—is coupled to V<sub>I/O</sub>—the I/O power supply or second supply voltage. *Id.* (citing Ex. 1003 ¶ 141; Ex. 1001, 1:62–2:1, 2:8–9). Petitioner further argues that "AAPA explains that the transistor M1 is configured to switch on when said first supply voltage is powered down and to switch off when said first supply voltage is powered on." Pet. 53 (citing Ex. 1001, 1:65–67, 2:8–9).

Petitioner further argues that AAPA in combination with Majcherczak teaches "at least one second transistor coupled in series with the at least one first transistor and coupled to said first supply voltage, the at least one second transistor being configured to switch on when said first supply voltage is powered on and to switch off when said first supply voltage is powered down" as recited in claim 1. *See* Pet. 54–55. More specifically, Petitioner argues transistor M3 is a second transistor and "AAPA explains that the transistor M3 is configured to switch on when said first supply voltage is powered down and to switch off when said first supply voltage is powered on." *Id.* (citing Ex. 1003 ¶¶ 141, 144–147; Ex. 1001, 1:65–67, 2:8–9).

Petitioner also argues that AAPA in combination with Majcherczak teaches "at least one third transistor coupled in series between the at least one first transistor and the at least one second transistor" as recited in claim 1. Pet. 55–56. Specifically, Petitioner points to transistor M2,<sup>15</sup> which, according to Petitioner, "is coupled in series between transistor M1 (i.e., the first transistor) and transistor M3 (i.e., the second transistor)." Pet. 56 (citing Ex. 1003 ¶ 144).

Patent Owner does not dispute Petitioner's contention that the combination of AAPA and Majcherczak teaches each of the limitations recited in claim 1. *See generally* PO Resp. 20–31; *see also* Pet. Reply 2

\_

<sup>&</sup>lt;sup>15</sup> The Petition interchangeably refers to transistor M2 and M3 as the third transistor. Pet. 56. However, the Petition specifically refers to the transistor highlighted in brown, which is transistor M2. We stated in the Institution Decision that we would "treat the reference to transistor M3 as a typographical error." Inst. Dec. 19 n.10. Neither party addressed this point in any subsequent briefing. *See generally* PO Resp.; Pet. Reply.

("Beyond this procedural issue [on whether applicant admitted prior art could be considered], Patent Owner's only substantive argument challenging Ground 2 is a purported lack of motivation to combine."); PO Sur-reply 2–19 (not disputing Petitioner's characterization of Patent Owner's argument).

We previously instructed Patent Owner that "any arguments for patentability not raised in the [Patent Owner Response] may be deemed waived." Scheduling Order, Paper 8, 5; *see also In re NuVasive, Inc.*, 842 F.3d 1376, 1380–81 (Fed. Cir. 2016) (determining Patent Owner waived arguments made only in its Preliminary Response but not raised in the Patent Owner Response after institution).

Based on the undisputed evidence before us and the reasons set forth in the Petition, Pet. 37–56, we find that the combination of AAPA and Majcherczak teaches all of the limitations recited in claim 1.

- b. Whether a Person of Ordinary Skill in the Art Would Have Combined AAPA and Majcherczak

- (1) Petitioner's Arguments

Petitioner argues that a person of ordinary skill in the art "would have been motivated to integrate the feedback transistor M6 from Majcherczak's voltage detector into the POC system 10 of AAPA in order to 'enable[] the proper stabilizing of the detection device." Pet. 45 (quoting Ex. 1008 ¶ 37) (citing Ex. 1003 ¶ 150). According to Petitioner, the "combination would result in AAPA's POC system 10 observing the 'hysteresis detection' described by Majcherczak, facilitating controlled operation of the I/O devices instructed by the POC signal on communications from the core devices when the core supply voltage is stably on." *Id.* (citing Ex. 1003 ¶ 150); *see also* Pet. Reply 2–5.

Petitioner further argues that "[i]t is undisputed in the [Patent Owner's Reponse] or by Dr. Pedram that adding Majcherczak's feedback transistor M6 to the AAPA as described in the Petition achieves the advantageous hysteresis described in Majcherczak." Pet. Reply 5 (citing PO Resp. 20–31; Ex. 2002 ¶¶ 67–85). According to Petitioner, "Dr. Pedram admits that it was possible to add hysteresis to the AAPA circuit shown in FIG. 1 of the '674 [p]atent, and that such an addition could help improve noise immunity of the circuit." *Id.* (citing Ex. 1017, 46:22–47:10).

Petitioner further argues that "it is irrelevant whether the prior art's explicit motivation to integrate Majcherczak's feedback transistor M6 into the AAPA matches the problem statement of the '674 [p]atent." Pet. Reply 6 (citing *Cross Med. Prods., Inc. v. Medtronic Sofamor Danek, Inc.*, 424 F.3d 1293, 1323 (Fed. Cir. 2005)). According to Petitioner, "[i]t is not necessary that the prior art suggest the combination to achieve the same advantage or result purportedly discovered by the Patent Owner." *Id.* (citing *In re Kahn*, 441 F.3d 977, 987 (Fed. Cir. 2006); *Cross*, 424 F.3d at 1323).

Moreover, according to Petitioner, a person of ordinary skill in the art would have a reasonable expectation of success:

A POSITA would have perceived a reasonable expectation of success in making this modification to the POC system 10 of AAPA, because the POC system 10 and Majcherczak's voltage detector share many functionally commensurate elements, operate in a corresponding manner, and are used in the similar types of multiple supply voltage devices. [Ex. 1003] ¶ 151. Indeed, the integration of the feedback transistor M6 from Majcherczak's voltage detector would have simply been the use of a known technique (a feedback transistor to improve hysteresis) to improve similar devices (detection circuits in multiple supply voltage devices) in the same way. *Id*.

Pet. 45.

Petitioner also argues that any potential disadvantages with the modification identified by Patent Owner and Dr. Pedram—additional leakage current compared to AAPA or Majcherczak, glitch current, and DC fighting condition (*see* PO Resp. 21–31)—"fail to demonstrate the absence of motivation." Pet. Reply 8; *see also id.* at 7–12. Specifically, Petitioner argues that "[i]t is well understood that 'a given course of action often has simultaneous advantages and disadvantages, and this does not necessarily obviate motivation to combine." *Id.* at 8 (citing *Medichem, S.A. v. Rolabo, S.L.*, 437 F.3d 1157, 1165 (Fed. Cir. 2006)). According to Petitioner, in this case, "the explicit benefit articulated in Majcherczak is not undone or outweighed by the vague and unsupported disadvantages described in the [Patent Owner's Response] and by Dr. Pedram." *Id.*

Petitioner also argues that there is no evidentiary support for any of the potential disadvantages articulated by Patent Owner and Dr. Pedram. Pet. Reply 7–12. Specifically, Petitioner argues neither Patent Owner nor Dr. Pedram cite to any references to support the list of disadvantages and Dr. Pedram admitted that the list is hypothetical and "that he never simulated any of the prior art or proposed combinations to determine what, if any, performance issues would arise from the proposed combination." *Id.* at 7–8 (citing Ex. 1017, 40:15–41:13, 45:9–15, 59:4–8, 61:4–10, 65:7–14, 167:20–23, 170:13–171, 171:20–172:1, 180:6–16, 187:25–188:9) (footnote omitted). Petitioner further argues that "[w]ithout corroborating evidence to contradict the explicit motivating teaching of Majcherczak, Dr. Pedram's statements are unsupported, exposing them as insufficient to establish substantial evidence addressing or confronting the affirmative proof offered by

Petitioner." *Id.* at 8 (citing *Ericsson Inc. v. Intellectual Ventures I LLC*, 890 F. 3d 1336, 1346 (Fed. Cir. 2018)).

Petitioner further argues that the problems of the asserted combination alleged by Patent Owner are "not inherent in the proposed architectural combination. Rather, such issues would only potentially arise due to an improper selection of design characteristics such as the transistor sizes, threshold voltages, and values of  $V_{I/O}$  and  $V_{core}$ ." Pet. Reply 9 (citing Ex.  $1018 \P 7-9, 74-77$ ); see also id. at 12 ("Even assuming a POSITA would have considered these as potential disadvantages in implementing the proposed combination, the POSITA would nevertheless have been motivated for reasons cited within Majcherczak to make the combination, as the POR's alleged disadvantages and their potential adverse impacts either would not have been observed or a POSITA would have been able to minimize them." (citing Ex.  $1018 \P 50-64$ )).

With regard to additional leakage current (PO Resp. 21–27), Petitioner argues that "Dr. Pedram acknowledged that it is the unclaimed design details—transistor sizes, threshold voltages, and values of  $V_{I/O}$  and  $V_{core}$ —that will determine the amount of leakage present in the proposed combination." Pet. Reply 10 (citing Ex. 1017, 63:22-65:20). Petitioner further argues that "Dr. Horst shows through simulation of these designs" that the proper selection of design details result in "mitigat[ing] any potentially problematic increase in leakage current, leaving the power consumption due to leakage current to be relatively the same or even better than either the AAPA or Majcherczak alone." *Id.* (citing Ex. 1018 ¶¶ 50–64, 68–73).

With regard to glitch current (PO Resp. 27–30), Petitioner argues that because the '674 patent acknowledges that glitch current was an issue with AAPA, "the addition of Majcherczak's feedback transistor would not have created a new problem in the circuit." Pet. Reply 10 (citing Ex. 1001, 2:25–30; Ex. 1018 ¶¶ 31, 56, 57, 75–77). Petitioner further argues that Dr. Horst's simulation shows that the glitch current can be mitigated by a proper selection of threshold voltages. *Id.* at 11 (citing Ex. 1018 ¶¶ 21–31, 50–64). <sup>16</sup>

With regard to the DC fighting condition (PO Resp. 27–30), Petitioner argues that Dr. Pedram states that this "could happen' only on 'rare occasions,' making any assessment of a hypothetical DC fighting condition a 'complicated task." Pet. Reply 11 (quoting Ex. 1017, 181:10–24).

Petitioner further argues that "[t]he condition is so complicated and rare, in fact, that Dr. Pedram believes that a POSITA would not even see or be aware of this disadvantage when analyzing the proposed combinations." *Id.* (citing Ex. 1017, 175:11–15). According to Petitioner, a person of ordinary skill in the art "cannot have been dissuaded by a potential 'rare' problem he/she would not have even been aware of." *Id.* Petitioner further argue that the condition is dependent on the selection of design details and "this alleged problem did not arise in Dr. Horst's simulations." *Id.* at 11–12 (citing Ex. 1017, 172:10–173:16, 178:9–181:24; Ex. 1018 ¶¶ 30, 32, 33).

\_

<sup>&</sup>lt;sup>16</sup> Petitioner's Reply cites to Exhibit 2018. Based on the context of the sentence, this appears to be a typographical error and that Petitioner intended to cite Exhibit 1018.

### (2) Patent Owner's Arguments

Patent Owner argues that, because "Petitioner's proposed combination results in a circuit with numerous operational flaws" that "would operate significantly worse than either the AAPA or Majcherczak had they been left unmodified," a person of ordinary skill in the art would "have had no reason to combine the alleged AAPA and Majcherczak as Petitioner proposes." PO Resp. 21; *see also id.* at 21–31; PO Sur-reply 2–19.

First, Patent Owner argues that "Petitioner's proposed addition of Majcherczak's transistor M6 to Fig. 1 of the '674 Patent (the alleged AAPA) results in *increased* leakage current, and the POSA would not be motivated to make Petitioner's proposed combination for at least this reason." PO Resp. 22 (citing Ex. 2002 ¶ 70); see also id. at 21–25; PO Sur-reply 4–5. Specifically, Patent Owner argues when the core power supply voltage (V<sub>core</sub>) is on, "PMOS transistor M1 and feedback transistor M6 will be 'off,' and NMOS transistors M2 and M3 will be 'on' providing a path between the output of the power U/D detector 100 and ground." PO Resp. 23–24. Patent Owner further argues that "[b]ecause [ $V_{core}$ ] is less then  $V_{I/O}$ , however, PMOS transistor M1 will be quite leaky, providing a high leakage path from V<sub>I/O</sub> to the output terminal of the power U/D detector 100." *Id.* at 24 (citing Ex. 2002 ¶ 72). Patent Owner further argues that "NMOS transistors N2 and M3 will be 'on,' providing a very low resistance path from the output terminal to Vss." Id. According to Patent Owner, as a consequence, "a high leakage DC path will exist between V<sub>I/O</sub> and Vss," which will result in more leakage current than would be present in the unmodified AAPA. *Id.* (citing Ex. 2002 ¶¶ 72–73).

Second, Patent Owner argues that the modified design "would also operate less effectively than Majcherczak alone." PO Resp. 25; *see also id.* at 25–27. Specifically, Patent Owner argues that "a [person having ordinary skill in the art] would have recognized that Majcherczak's power supply stage (E2) operates to reduce leakage current through the pull-up PMOS transistor (M4) in the input stage (E1) and thus helps to offset any additional leakage current introduced by the feedback transistor (M6)." *Id.* at 26 (citing Ex. 2002 ¶¶ 76–78). According to Patent Owner, because Petitioner does not suggest incorporating Majcherczak's power supply stage (E2) into the AAPA, "[t]he power detection circuit depicted in Fig. 2 of Majcherczak would thus operate with significantly less leakage current than Petitioner's proposed combination." *Id.* at 26–27 (citing Ex. 2002 ¶¶ 76–79).

Third, Patent Owner argues that Petitioner's proposed combination "would also introduce substantial operational problems during the process of powering on the core voltage supply (Vcore), causing increased glitch (i.e., crowbar) current and circuit instability." PO Resp. 27; *see also id.* at 27–30. More specifically, Patent Owner argues that "switching delays of the power up/down detector 100 and inverter 105 . . . will cause the feedback transistor M6 . . . to remain on for at least some delay period after the core power supply voltage (Vcore) turns on." *Id.* at 28 (citing Ex. 2002 ¶¶ 81–82). Patent Owner further argues that this can cause an unstable DC fighting condition during the inverter delay period. *Id.* (citing Ex. 2002 ¶ 83). According to Patent Owner, the DC fighting condition "can cause a downstream ripple effect such that Inverter 105 . . . becomes unstable, causing further instability in the 'feedback network' . . ., and potentially

resulting in a complete circuit breakdown" or, at the very least, worsen the glitch current. *Id.* at 28–30 (citing Ex. 2002 ¶¶ 83–84).

Patent Owner further argues that, contrary to Petitioner's arguments, a person of ordinary skill in the art would not seek to add hysteresis. PO Surreply 2–4. According to Patent Owner, a person having ordinary skill in the art would, instead, focus on how to solve the problems articulated in AAPA—high leakage current and slow switching times. *Id.* More specifically, Patent Owner argues that (1) a person having ordinary skill in the art would have avoided adding hysteresis because it would make the problems identified in the '674 patent worse, (2) in light of the switching-speed problem articulated in the AAPA, the addition of hysteresis involves impermissible hindsight, and (3) AAPA does not suggest that stability is a problem in AAPA's circuit. *Id.* at 4–6.

Patent Owner further argues that Petitioner's argument (Pet. Reply 7) that Dr. Pedram does not cite to any references to support his list of disadvantages is misplaced. PO Sur-reply 7. According Patent Owner, no references are needed because the disadvantages "are all well-known phenomena that would be immediately apparent to the [person having ordinary skill in the art] upon considering the proposed combination" and "Petitioner sets forth no argument that the disadvantages described by Dr. Pedram are obscure or not generally understood, and such an assertion would be wrong." *Id.* Patent Owner further argues that "the reply cites no statute, rule, or caselaw to support the proposition that an expert's opinion must be corroborated by independent references." *Id.*

Patent Owner also argue that Petitioner's citation to "Medichem, S.A. v. Rolabo, S.L. that 'a given course of action often has simultaneous

advantages and disadvantages, and this does not necessarily obviate motivation to combine" is misplaced because "the purported advantage of Majcherczak is no advantage at all." PO Sur-reply 7–8.

Finally, Patent Owner presents six arguments explaining why Dr. Horst's simulations do not prove that a person of ordinary skill in the art would have been motivated to combine AAPA and Majcherczak. *See* PO Sur-reply 8–18.

First, Patent Owner argues that "Petitioner's argument misunderstands the proper inquiry for obviousness." *Id.* at 8. According to Patent Owner, "[t]he relevant question is whether the [person of ordinary skill in the art] would be motivated to combine the alleged AAPA and Majcherczak to reach the claimed invention," not whether the person of ordinary skill in the art would combine the references and then use a simulation to determine a set of parameters that would avoid the problems identified by Dr. Pedram. *Id.* at 8–9.

Second, Patent Owner argues that the simulations are unreliable because Dr. Horst's supplemental declaration contained numerous errors. *See* PO Sur-reply 9–11. For example, Patent Owner points out how the results in the simulation of two different circuits were identical. *Id.* at 9 (comparing Ex. 1018 ¶ 12 with Ex. 1018 ¶ 23). Patent Owner points out that a corrective declaration with a new set of graphs intended to replace page 15 of the supplemental declaration introduced a new error in the results of Figure 4. *Id.* at 9–11 (citing Ex. 2007).

Third, Patent Owner argues that Dr. Horst selected unrealistic parameter values that the person of ordinary skill in the art would never use in the proposed combination of AAPA and Majcherczak. *See* PO Sur-

reply 11–16. Specifically, Patent Owner argues Dr. Horst selected a high FET threshold voltage that results in the problem of slow switching speed discussed in the '674 patent, the selected channel length and width parameters were selected from the Voss reference (Exhibit 1022) that is not from the field related to the technology of AAPA, and that the values are divorced from real world considerations. *Id*.

Fourth, Patent Owner argues Dr. Horst "cherry picked" parameter values without providing a sufficient rationale for their selection. PO Surreply 16–17. Specifically, Patent Owner criticizes Dr. Horst for using the values of the Voss reference for most transistors but provides no explanation for why the Voss reference was not used for all transistors. *Id.* Patent Owner further argues that Dr. Horst explained at his deposition that he changed the width of the feedback transistor from that given in Voss because if the Voss parameters were used consistently, the simulation would fail. *Id.* at 17 (citing Ex. 2006, 101:24–102:17).

Fifth, Patent Owner argues that Dr. Horst's simulation does not show that the combination of AAPA and Majcherczak does not result in increased leakage current. PO Sur-reply 17–18. Specifically, Patent Owner argues that ramping the  $V_{core}$  to max value and then immediately pulling back—as done in the simulation—is not an accurate way of measuring leakage current. *Id* at 18. Patent Owner argues that leakage power is primarily a problem when  $V_{core}$  is high and, if the simulation was addressing leakage, it should have left  $V_{core}$  voltage at 3.3V for at least some time. *Id.* at 18.

Sixth, Patent Owner argues that a single simulation is not sufficient. PO Sur-reply 18–19. More specifically, Patent Owner argues that a typical engineer will perform thousands of computer simulations and that "a single

simulation result cannot provide an accurate indication of whether a circuit would operate correctly under realistic, real-world conditions." *Id.* at 19. Patent Owner further argues that, although Dr. Horst's testimony discusses a single simulation, Dr. Horst executed many more simulations, but did not save the results of those simulations. *Id.* at 18–19.

### (3) Our Analysis

A conclusion of unpatentability based on obviousness must be supported by "some articulated reasoning with some rational underpinning to support the legal conclusion of obviousness." *Kahn*, 441 F.3d at 988 (citations omitted), *cited with approval in KSR*, 550 U.S. at 418. The requirement for a reason to combine the reference acts as a check on the potential for the improper use of hindsight. *Plantronics, Inc. v. Aliph, Inc.*, 724 F.3d 1343, 1354 (Fed. Cir. 2013) (holding that an articulated reasoning "is especially important to guard against the dangers of hindsight bias").

Based on the entirety of the record, we find Petitioner has shown sufficiently articulated reasoning with rational underpinning to support the legal conclusion of obviousness. Petitioner provides detailed analysis of the prior art and explains why, based on the teachings of the references, a person of ordinary skill in the art would have combined the references. *See* Pet. 37–45; Pet. Reply 3–6.

It is undisputed that Majcherczak identifies a problem with circuits with multiple supply voltage devices when the core voltage is powered down or slow to power up. *See* Ex. 1008 ¶¶ 7–8; *see also* Pet. 39. Specifically, Majcherczak states that

[w]hen the core supply voltage disappears, the two logic voltages DATA and /DATA fall to zero. The two control transistors are then off. The voltage at an output of the

IPR2018-01315, IPR2018-01316 Patent 8,063,674 B2

> translator becomes uncontrollable and dependent on the leakage currents in the transistors of the translator, or on a contradiction between two logic signals.

Ex. 1008 ¶ 7.

Majcherczak teaches using an output stage E3 which includes a "transistor M6 for pulling the output node Nin of the inverter of the input stage to the interface [I/O] power supply voltage Vdd3." Ex. 1008 ¶ 37. Majcherczak describes that "transistor M6 enables the proper stabilizing of the detection device. It maintains the node Nin at Vdd3, by feedback." *Id.* Majcherczak further describes how this allows for a hysteresis detection:

With the output stage E3, a hysteresis detection is obtained with a low threshold of switching from a state of the presence of a core power supply to a state of the absence of a core power supply, and a high threshold of switching of the detection circuit from a state of absence of the core supply to a state of presence of the core supply. In particular, if the output node Nin of the input stage is at Vdd3, then the signal IN applied to its input rises sufficiently to force the output node Nin downwards, and consequently, cut off the pull-down transistor M6. In a practical example, for integrated circuits using  $0.18~\mu$  technology with a core supply voltage of 1.8~volts, the high threshold may thus be equal to 0.98~volts and the low threshold may be equal to 0.33~volts.

Id. ¶ 38. "[H]ysteresis detection is useful for ensuring that the level shifters only operate to facilitate communications between the core network and the I/O network when the core supply voltage is stably on." Ex. 1003 ¶ 138 (Horst Decl.).

We are persuaded by the evidence in the record that a person having ordinary skill in the art would have "integrate[d] feedback transistor M6 from Majcherczak's voltage detector into the POC system 10 of the AAPA in order to 'enable[] the proper stabilizing of the detection device."

Ex. 1003 ¶ 150 (Horst Decl.) (quoting Ex. 1008 ¶ 37). The person having ordinary skill of the art would have made such a modification to add hysteresis detection to AAPA's POC system 10, thereby "ensuring that the I/O devices instructed by the POC signal only operate on communications from the core devices when the core supply voltage is stably on." *Id*.

It is inapposite that the reason for the modification is different from the problem being addressed in the '674 patent. In *KSR*, the Supreme Court rejected the application of rigid rules, such as considering only the problem the patentee was trying to solve:

The first error of the Court of Appeals in this case was to foreclose this reasoning by holding that courts and patent examiners should look only to the problem the patentee was trying to solve. The Court of Appeals failed to recognize that the problem motivating the patentee may be only one of many addressed by the patent's subject matter. The question is not whether the combination was obvious to the patentee but whether the combination was obvious to a person with ordinary skill in the art. Under the correct analysis, any need or problem known in the field of endeavor at the time of invention and addressed by the patent can provide a reason for combining the elements in the manner claimed.

KSR, 550 U.S. at 420 (emphases added, citations omitted). Instead, the Supreme Court applied a flexible approach, holding that "if a technique has been used to improve one device, and a person of ordinary skill in the art would recognize that it would improve similar devices in the same way, using the technique is obvious unless its actual application is beyond his or her skill." *Id.* at 417; *see also id.* ("When a patent simply arranges old elements with each performing the same function it had been known to perform and yields no more than one would expect from such an

IPR2018-01315, IPR2018-01316 Patent 8,063,674 B2

arrangement, the combination is obvious.") (internal quotation and citation omitted).

Consistent with the Supreme Court's *KSR* holding, the Federal Circuit has similarly rejected arguments based on a reason to combine that were different from the one identified by the patentee. For example, in *Samsung Electronics Co. v. UUSI, LLC*, the Federal Circuit reversed a PTAB decision that required the reason to combine the references to be directed to the same problem as identified in the challenged patent:

UUSI next argues that the Board was correct in finding that Gerpheide was addressed to a different problem, referring us to its expert's testimony regarding the fact that Gerpheide and the '183 patent were directed to different problems and solved those problems in different ways. Samsung argues that under KSR International Co. v. Teleflex Inc., 550 U.S. 398, 127 S.Ct. 1727, 167 L.Ed.2d 705 (2007), the Board's decision was legally erroneous because it required the proffered motivation to combine Gerpheide with Ingraham/Caldwell to be the same as the one that animated the patentee in arriving at the claimed invention. We agree with Samsung. The Board's categorical rejection of the teachings from a single input device to those of a multi input device is not supportable. "[I]f a technique has been used to improve one device, and a person of ordinary skill in the art would recognize that it would improve similar devices in the same way, using the technique is obvious unless its actual application is beyond his or her skill." Id. at 417, 127 S.Ct. 1727.

Samsung Electronics Co. v. UUSI, LLC, 775 F. App'x 692, 695 (Fed. Cir. 2019) (emphasis added); see also In re Conrad, 759 F. App'x 982, 985 (Fed. Cir. 2019) ("The Supreme Court and this court, however, have repeatedly held that the motivation that a person of ordinary skill in the art would have had to combine prior art references need not be the same motivation that inspired the patent owner." (citation omitted)); In re Beattie, 974 F.2d 1309,

1312 (Fed. Cir. 1992) ("As long as some motivation or suggestion to combine the references is provided by the prior art taken as a whole, the law does not required that the references be combined for the reasons contemplated by the inventor.").

Furthermore, the evidence shows that a person having ordinary skill in the art would have had a reasonable expectation of success. *See* Ex. 1003 ¶ 151 (Horst Decl.). Specifically we are persuaded by Dr. Horst's testimony that "the integration of feedback transistor M6 from Majcherczak's voltage detector would have simply been the use of a known technique (a feedback transistor to provide hysteresis) to improve similar devices (detection circuits in multiple supply voltage devices) in the same way." *Id*.

We disagree with Patent Owner's arguments, discussed below.

Explicit Motivation: As a preliminary matter, "for the reasons discussed above with regard to reason to combine, we are not persuaded by Patent Owner's argument that an explicit motivation to combine the references is required for obviousness." *See* PO Sur-reply 2–6. Moreover, Patent Owner's argument that Majcherczak's hysteresis detection does not provide an explicit motivation to combine the references is not timely and waived. *See* PO Sur-reply 2–6. Petitioner made its hysteresis argument in the Petition and Patent Owner did not address the arguments in its Response. *Compare* Pet. 45 (relying on hysteresis detection for the reason to combine the references), *with* PO Resp. 20–31 (not discussing hysteresis); *see also* Tr. 74:13–18 (acknowledging the argument was not raised in the Patent Owner's Response). Although Patent Owner addresses this argument in its Sur-reply, "arguments for patentability not raised in the response may be deemed waived." Scheduling Order, Paper 8, 5; *see also Nuvasive*, 842 F.3d

at 1380–81 (holding that an argument not presented in Patent Owner's response is waived); *Dell Inc. v. Acceleron, LLC*, 884 F.3d 1364, 1369 (Fed. Cir. 2018) (holding that the Board was not obligated to consider an "untimely argument"). Because Patent Owner did not address Petitioner's argument regarding an explicit motivation in the Patent Owner's Response, that argument is waived.

Potential Issues: We do not agree with Patent Owner that a person having ordinary skill in the art would not have combined AAPA with Majcherczak because of the following potential issues identified by Dr. Pedram: additional leakage current compared to AAPA, glitch current, and a DC fighting condition. *See* PO Resp. 21–25, 27–31. Patent Owner's argument relies exclusively on Dr. Pedram's testimony as support for why a person having ordinary skill in the art would not make the proposed modification due to the identified "problems." *See id.* (citing Ex. 2002 ¶¶ 70–74, 81–85). However, Dr. Pedram does not cite to any evidence to support his opinions. *See* Ex. 2002 ¶¶ 70–74, 81–85. That is, Dr. Pedram does not cite to any tests, references, or simulations that support his opinion. *Id.*; Ex. 1017, 41:6–13, 171:20–171:3 (Pedram Dep.).

This stands in marked contrast to Dr. Horst's testimony. In response to Dr. Pedram's argument that the combination of AAPA and Majcherczak would result in increased leakage current, glitch current, or a DC fighting condition, Dr. Horst conducted a computer simulation to demonstrate that, with the appropriate selection of design details, those potential problems

could be managed. See Ex. 1018 ¶¶ 21–33 (Horst Supp. Decl.); Ex. 2007 (Horst Corrective Decl.).  $^{17}$

Our rules provide that "[e]xpert testimony that does not disclose the underlying facts or data on which the opinion is based is entitled to little or no weight." 37 C.F.R. 42.65(a). In light of the failure to provide any corroboration, such as a simulation, we give Dr. Pedram's conclusory, unsupported testimony little weight. *See In re Am. Acad. of Sci. Tech Ctr.*, 367 F.3d 1359, 1368 (Fed. Cir. 2004) ("[T]he Board is entitled to weigh the declarations and conclude that the lack of factual corroboration warrants discounting the opinions expressed in the declarations."); *Verlander v. Garner*, 348 F.3d 1359, 1371 (Fed. Cir. 2003) (noting that the Board has discretion to accord little weight to broad conclusory statements from expert witness); *Ashland Oil, Inc. v. Delta Resins & Refractories, Inc.*, 776 F.2d 281, 294 (Fed. Cir. 1985) (noting that the "[1]ack of factual support" for an expert opinion "may render the testimony of little probative value").

In contrast to the potential issues discussed in the preceding paragraphs, Dr. Pedram provides some factual support for his testimony that the proposed modification would result in an increased leakage current compared to Majcherczak alone. *See* Ex. 2002 ¶¶ 75–80 (citing Ex. 1008). However, although Dr. Pedram may have established that "[t]he power detection circuit depicted in Fig. 2 of Majcherczak would thus operate with significantly less leakage current than Petitioner's proposed combination, which omits the power supply stage (E2) of Majcherczak," (Ex. 2002 ¶ 79), that is not the relevant issue. Instead, the issue is whether a person of

<sup>&</sup>lt;sup>17</sup> We address Patent Owner's arguments regarding Dr. Horst's simulation *infra*.

ordinary skill in the art would have improved AAPA by "integrat[ing] feedback transistor M6 from Majcherczak's voltage detector into the POC system 10 of the AAPA in order to 'enable[] the proper stabilizing of the detection device." Ex. 1003 ¶ 150 (Horst Decl.) (quoting Ex. 1008 ¶ 37).

Moreover, merely identifying potential problems that could arise with a combination of references is not, by itself, enough to demonstrate that the combination would not have been obvious. Rather, "a given course of action often has simultaneous advantages and disadvantages, and this does not necessarily obviate motivation to combine." *Medichem, S.A. v. Rolabo*, S.L., 437 F.3d 1157, 1165 (Fed. Cir. 2006) (citing Winner Int'l Royalty Corp. v. Wang, 202 F.3d 1340, 1349 n. 8 (Fed. Cir. 2000)). Accordingly, "[t]he fact that the motivating benefit comes at the expense of another benefit, however, should not nullify its use as a basis to modify the disclosure of one reference with the teachings of another. Instead, the benefits, both lost and gained, should be weighed against one another." Winner, 202 F.3d at 1349 n.8. Although Patent Owner and Dr. Pedram identify potential problems with the combination of AAPA and Majcherczak, they do not weigh the relative advantages and disadvantages. Considering only one half of the analysis is not sufficient. This is especially true in light of (1) the explicit benefit discussed in Majcherczak and (2) the unsupported identification of potential issues in the Patent Owner's Response and Dr. Pedram's testimony.

Additionally, we are persuaded by Dr. Horst's testimony that any potential problems in the combination would have been addressed by the person having ordinary skill in the art by the selection of appropriate design characteristics such as the transistor sizes, threshold voltages, and values of

$V_{I/O}$  and  $V_{core}$ . See Ex. 1018 ¶¶ 74–77; see also id. ¶¶ 50–73. That is, the simulation performed by Dr. Horst shows that, under at least one set of design characteristics, the problems identified by Dr. Pedram do not exist. Id. ¶¶ 21–31 (Horst Supp. Decl.); Ex. 2007 ¶¶ 2–4 (Horst Corrective Decl.). Although the evidence does not show that every permutation of design characteristics will work, the evidence does show that it would have been within the ability of a person having ordinary skill in the art to determine appropriate design values to minimize or eliminate the potential problems identified by Dr. Pedram.

Reliability of Dr. Horst's Simulations: We do not agree with Patent Owner that Dr. Horst's simulation is unreliable because the results for two different circuits are identical. *See* PO Sur-reply 9 (citing Ex. 1018, ¶¶ 12, 23). As Patent Owner concedes, prior to his deposition, Dr. Horst prepared a corrective declaration pointing out the mistake and replacing the erroneous charts from page 15. *Id.* at 9–10; *see also* Ex. 2007 (Horst Corrective Decl). In light of Dr. Horst's recognition that he "inserted the wrong set of graphs when preparing [his] supplemental report" and timely provided a correction prior to cross examination, *see* Ex. 2007, ¶ 2, we do not find that the original mistake renders the simulation unreliable. To the contrary, we credit Dr. Horst for recognizing his mistake and providing the correct graphs.

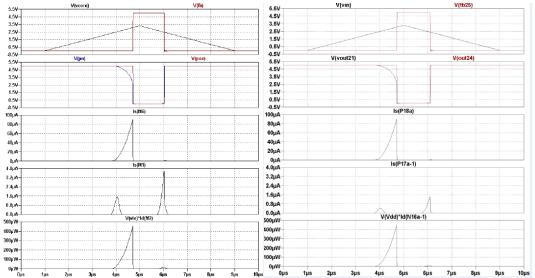

Nor are we persuaded that the introduction of a second mistake in the corrective declaration renders the simulation unreliable. *See* PO Sur-reply 9–11. A comparison of the results of Dr. Horst's simulation relating to Figure 4 of the '674 patent and the combination of AAPA and Majcherczak from his Supplemental Declaration—the original simulation report—is reproduced below.

Simulations of the '674 Figure 4 circuit (left) and AAPA+ Majcherczak (right). Waveforms are nearly identical.

Ex. 1018 ¶ 23 (Horst Supp. Decl.). The figure above shows the results of Dr. Horst's simulation of the circuit of Figure 4 of the '674 patent (left) and the circuit that is the result of the combination of AAPA and Majcherczak (right). *Id.* Relevant to our analysis, the third graph for the Figure 4 circuit is labeled Is(M6). Patent Owner has not alleged any error in the labeling of this chart. *See generally* PO Sur-reply.

However, in the replacement graph of the Corrective Declaration, that graph is relabeled as Is(M2). Ex. 2007, ¶ 2 (Horst Corrective Decl.); *see also* PO Sur-reply. As Patent Owner points out in the Sur-reply, there is no transistor M2 in the Figure 4 embodiment. *See* Ex. 1018 ¶ 22. Because the labeling was correct in the original version and the correction focused on the graphs on the right side, not the left, this appears to be no more than a typographical error. As such, it does not have a substantial impact on Dr. Horst's credibility.

In conclusion, we have considered Patent Owner's arguments. However, based on the entirety of the record, we find Dr. Horst's simulations and Dr. Horst's discussion of those simulations reliable.