US005731768A

# United States Patent [19]

**Tsang**

[11] Patent Number:

5,731,768

[45] Date of Patent:

Mar. 24, 1998

#### [54] METHOD AND APPARATUS FOR IMPLEMENTING CODES WITH MAXIMUM TRANSITION RUN LENGTH

[75] Inventor: Kinhing P. Tsang, Plymouth, Minn.

[73] Assignee: Seagate Technology, Inc., Scotts

Valley, Calif.

[21] Appl. No.: 594,987

[22] Filed: Jan. 31, 1996

[51] Int. Cl.<sup>6</sup> ...... H03M 7/46

[52] U.S. Cl. ...... 341/59

[56] References Cited

U.S. PATENT DOCUMENTS

5,144,304 9/1992 McMahon ...... 341/58

Primary Examiner—Brian K. Young

Attorney, Agent, or Firm-Kinney & Lange, P.A.

57] ABSTRACT

Encoding and decoding systems for data blocks based on forming corresponding code blocks having a maximum number of successive repetitions of a first symbol and a maximum number of successive repetitions of a second symbol, and having code blocks which can represent plural different ones of said data blocks unambiguously by having further code blocks aid in distinguishing data block is being represented.

#### 19 Claims, 15 Drawing Sheets

Mar. 24, 1998

| Gro    | oup A | Group B |     | Gr     | oup C | Gr     | oup D |

|--------|-------|---------|-----|--------|-------|--------|-------|

| Binary | HEX   | Binary  | HEX | Binary | HEX   | Binary | HEX   |

| 100001 | 21    | 100000  | 20  | 000001 | 01    | 000010 | 02    |

| 100011 | 23    | 100010  | 22  | 010001 | 11    | 000100 | 04    |

| 100101 | 25    | 100100  | 24  | 001001 | 09    | 000110 | 06    |

| 101001 | 29    | 100110  | 26  | 011001 | 19    | 001000 | 08    |

| 101011 | 2B    | 101000  | 28  | 000101 | 05    | 001010 | 0A    |

| 101101 | 2D    | 101010  | 2A  | 010101 | 15    | 001100 | 0C    |

| 110001 | 31    | 101100  | 2C  | 001101 | 0D    | 010000 | 10    |

| 110011 | 33    | 110000  | 30  | 000011 | 03    | 010010 | 12    |

| 110101 | 35    | 110010  | 32  | 010011 | 13    | 010100 | 14    |

|        |       | 110100  | 34  | 001011 | 0B    | 010110 | 16    |

|        | ij    | 110110  | 36  | 011011 | 1B    | 011000 | 18    |

|        |       |         |     |        |       | 011010 | 1A    |

FIG. 2

|            | State $0 (S_0)$ |               | State 1 (S <sub>1</sub> ) |                           |

|------------|-----------------|---------------|---------------------------|---------------------------|

| Data (HEX) | Codeword (HEX)  | Next<br>State | Codeword (HEX)            | Next<br>State             |

| 00000 (00) | 100000 (20)     | $S_0$         | 011000 (18)               | $S_0$                     |

| 00001 (01) | 100010 (22)     | $S_0$         | 000010 (02)               | $S_0$                     |

| 00010 (02) | 100100 (24)     | $S_0$         | 000100 (04)               | $S_0$                     |

| 00011 (03) | 100110 (26)     | $S_0$         | 000110 (06)               | $S_0$                     |

| 00100 (04) | 101000 (28)     | $S_0$         | 001000 (08)               | $S_0$                     |

| 00101 (05) | 101010 (2A)     | $S_0$         | 001010 (0A)               | $S_0$                     |

| 00110 (06) | 101100 (2C)     | $S_0$         | 001100 (0C)               | $S_0$                     |

| 00111 (07) | 110110 (36)     | $S_0$         | 010110 (16)               | $\mathrm{S}_{\mathrm{0}}$ |

| 01000 (08) | 110000 (30)     | $S_0$         | 010000 (10)               | $S_0$                     |

| 01001 (09) | 110010 (32)     | $S_0$         | 010010 (12)               | $S_0$                     |

| 01010 (0A) | 110100 (34)     | $S_0$         | 010100 (14)               | $S_0$                     |

| 01011 (0B) | 100001 (21)     | $S_1$         | 010001 (11)               | $S_1$                     |

| 01100 (0C) | 100011 (23)     | $S_1$         | 010011 (13)               | $S_1$                     |

| 01101 (0D) | 100101 (25)     | $S_1$         | 010101 (15)               | $S_1$                     |

| U.            |         | _              |             |       |             |            |

|---------------|---------|----------------|-------------|-------|-------------|------------|

| U.S.          |         | $S_1$          | 011001 (19) | $S_1$ | 101001 (29) | 01110 (0E) |

| Patent        |         | $S_1$          | 011011 (1B) | $S_1$ | 101011 (2B) | 01111 (0F) |

| ent           |         | $S_1$          | 011000 (18) | $S_1$ | 100000 (20) | 10000 (10) |

|               |         | $S_1$          | 000010 (02) | $S_1$ | 100010 (22) | 10001 (11) |

|               |         | $\mathbf{S}_1$ | 000100 (04) | $S_1$ | 100100 (24) | 10010 (12) |

| Mar           |         | $S_1$          | 000110 (06) | $S_1$ | 100110 (26) | 10011 (13) |

| : 24,         |         | $S_1$          | 001000 (08) | $S_1$ | 101000 (28) | 10100 (14) |

| Mar. 24, 1998 |         | $S_1$          | 001010 (0A) | $S_1$ | 101010 (2A) | 10101 (15) |

| <b>∞</b>      | ,       | $S_1$          | 001100 (0C) | $S_1$ | 101100 (2C) | 10110 (16) |

|               |         | $S_1$          | 010110 (16) | $S_1$ | 110110 (36) | 10111 (17) |

| Shee          |         | $S_1$          | 010000 (10) | $S_1$ | 110000 (30) | 11000 (18) |

| Sheet 4 of    |         | $S_1$          | 010010 (12) | $S_1$ | 110010 (32) | 11001 (19) |

| of 15         |         | $S_1$          | 010100 (14) | $S_1$ | 110100 (34) | 11010 (1A) |

|               |         | $S_1$          | 001101 (0D) | $S_1$ | 101101 (2D) | 11011 (1B) |

|               |         | $S_1$          | 000011 (03) | $S_1$ | 110011 (33) | 11100 (1C) |

| (h            |         | $S_1$          | 000101 (05) | $S_1$ | 110101 (35) | 11101 (1D) |

| 5,73          | FIG. 3B | $S_1$          | 001001 (09) | $S_1$ | 110001 (31) | 11110 (1E) |

| 5,731,768     | 110. 50 | $S_i$          | 001011 (0B) | $S_1$ | 011010 (1A) | 11111 (1F) |

| 68            | -       |                |             | ·     |             |            |

|               |         |                |             |       |             |            |

Mar. 24, 1998

| Group   | A   | Group   | В   | Group   | C   | Group   | D          |

|---------|-----|---------|-----|---------|-----|---------|------------|

| Binary  | HEX | Binary  | HEX | Binary  | HEX | Binary  | HEX        |

| 1000001 | 41  | 1000000 | 40  | 0000001 | 01  | 0000010 | 02         |

| 1000011 | 43  | 1000010 | 42  | 0100001 | 21  | 0000100 | 04         |

| 1000101 | 45  | 1000100 | 44  | 0010001 | 11  | 0000110 | 06         |

| 1001001 | 49  | 1000110 | 46  | 0110001 | 31  | 0001000 | 08         |

| 1001011 | 4B  | 1001000 | 48  | 0001001 | 09  | 0001010 | 0 <b>A</b> |

| 1001101 | 4D  | 1001010 | 4A  | 0101001 | 29  | 0001100 | 0C         |

| 1010001 | 51  | 1001100 | 4C  | 0011001 | 19  | 0010000 | 10         |

| 1010011 | 53  | 1010000 | 50  | 0000101 | 05  | 0010010 | 12         |

| 1010101 | 55  | 1010010 | 52  | 0100101 | 25  | 0010100 | 14         |

| 1011001 | 59  | 1010100 | 54  | 0010101 | 15  | 0010110 | 16         |

| 1011011 | 5B  | 1010110 | 56  | 0110101 | 35  | 0011000 | 18         |

| 1100001 | 61  | 1011000 | 58  | 0001010 | 0D  | 0011010 | 1A         |

| 1100011 | 63  | 1011010 | 5A  | 0101101 | 2D  | 0100000 | 20         |

| 1100101 | 65  | 1100000 | 60  | 0000011 | 03  | 0100010 | 22         |

| 1101001 | 69  | 1100010 | 62  | 0100011 | 23  | 0100100 | 24         |

| 1101011 | 6B  | 1100100 | 64  | 0010011 | 13  | 0100110 | 26         |

| 1101101 | 6D  | 1100110 | 66  | 0110011 | 33  | 0101000 | 28         |

|         |     | 1101000 | 68  | 0001011 | 0B  | 0101010 | 2A         |

|         |     | 1101010 | 6A  | 0101011 | 2B  | 0101100 | 2C         |

|         |     | 1101100 | 6C  | 0011011 | 1B  | 0110000 | 30         |

|         |     |         |     |         |     | 0110010 | 32         |

| ł       |     |         |     |         |     | 0110100 | 34         |

|         |     |         |     |         |     | 0110110 | 36         |

FIG. 6

| Group    | Α       | Group    | В   | Group    | C C | Grou     | o D |

|----------|---------|----------|-----|----------|-----|----------|-----|

| Binary   | HEX     | Binary   | HEX | Binary   | HEX | Binary   | HEX |

| Group AA |         | Group BD |     | Group CD |     | Group D1 | - W |

| 1100011  | 63      | 1000000  | 40  | 0000001  | 01  | 0000100  | 04  |

| 1101011  | 6B      | 1000010  | 42  | 0100001  | 21  | 0000110  | 06  |

|          | ******* | 1000100  | 44  | 0010001  | 11  | 0001000  | 08  |

| Group AB |         | 1000110  | 46  | 0110001  | 31  | 0001010  | 0A  |

| 1100001  | 61      | 1001000  | 48  | 0001001  | 09  | 0010000  | 10  |

| 1100101  | 65      | 1001010  | 4A  | 0101001  | 29  | 0010010  | 12  |

| 1101001  | 69      | 1001100  | 4C  | 0011001  | 19  | 0010100  | 14  |

| 1101101  | 6D      | 1010000  | 50  | 0000101  | 05  | 0010110  | 16  |

|          |         | 1010010  | 52  | 0100101  | 25  | 0100100  | 24  |

| Group AC |         | 1010100  | 54  | 0010101  | 15  | 0100110  | 26  |

| 1000011  | 43      | 1010110  | 56  | 0110101  | 35  | 0101000  | 28  |

| 1001011  | 4B      | 1011000  | 58  | 0001010  | 0D  | 0101010  | 2A  |

| 1010011  | 53      | 1011010  | 5A  | 0101101  | 2D  | 0110000  | 30  |

| 1011011  | 5B      |          |     |          |     | 0110010  | 32  |

|          |         | Group BB |     | Group CC |     | 0110100  | 34  |

| Group AD |         | 1100000  | 60  | 0000011  | 03  | 0110110  | 36  |

| 1000001  | 41      | 1100010  | 62  | 0100011  | 23  |          |     |

| 1000101  | 45      | 1100100  | 64  | 0010011  | 13  | Group D2 |     |

| 1001001  | 49      | 1100110  | 66  | 0110011  | 33  | 0000010  | 02  |

| 1001101  | 4D      | 1101000  | 68  | 0001011  | 0B  | 0001100  | 0C  |

| 1010001  | 51      | 1101010  | 6A  | 0101011  | 2B  | 0011000  | 18  |

| 1010101  | 55      | 1101100  | 6C  | 0011011  | 1B  | 0011010  | 1A  |

| 1011001  | 59      |          |     |          |     | 0100000  | 20  |

|          |         |          |     |          |     | 0100010  | 22  |

|          |         |          |     |          |     | 0101100  | 2C  |

FIG. 7

|             | State 0 (    | $(S_0)$          | State 1 (    | $(S_1)$                   | State 2 (    | $(S_2)$        | State 3 (    | $S_3$ ) |

|-------------|--------------|------------------|--------------|---------------------------|--------------|----------------|--------------|---------|

| Data (HEX)  | Codeword     | Next             | Codeword     | Next                      | Codeword     | Next           | Codeword     | Next    |

|             | (HEX)        | State            | (HEX)        | State                     | (HEX)        | State          | (HEX)        | State   |

| 000000 (00) | 1100001 (61) | $\overline{S_2}$ | 1001101 (4D) | $S_2$                     | 0000010 (02) | $S_0$          | 0000100 (04) | $S_0$   |

| 000001 (01) | 1100101 (65) | $S_2$            | 1000010 (42) | $S_0$                     | 0011000 (18) | $S_0$          | 0000110 (06) | $S_0$   |

| 000010 (02) | 1101001 (69) | ${f S}_2$        | 1000100 (44) | $S_0$                     | 0011010 (1A) | $S_0$          | 0001000 (08) | $S_0$   |

| 000011 (03) | 1101101 (6D) | $S_2$            | 1000110 (46) | $S_0$                     | 0011000 (18) | $S_1$          | 0001010 (0A) | $S_0$   |

| 000100 (04) | 1100001 (61) | $S_3$            | 1001000 (48) | $S_0$                     | 0011010 (1A) | $\mathbf{S}_1$ | 0010000 (10) | $S_0$   |

| 000101 (05) | 1100101 (65) | $S_3$            | 1001010 (4A) | $S_0$                     | 0100000 (20) | $\mathbf{S}_1$ | 0010010 (12) | $S_0$   |

|             | 1101001 (69) | $S_3$            | 1001100 (4C) | $S_0$                     | 0000011 (03) | $S_3$          | 0010100 (14) | $S_0$   |

| ` ' '       | 1101101 (6D) | $S_3$            | 1001101 (4D) | $S_3$                     | 0001100 (0C) | $S_0$          | 0010110 (16) | $S_0$   |

| 001000 (08) | 1100000 (60) | $S_0$            | 1010000 (50) | $S_0$                     | 0000011 (03) | $S_2$          | 0100100 (24) | $S_0$   |

| 001001 (09) | 1100010 (62) | $S_0$            | 1010010 (52) | $\mathrm{S}_{\mathrm{o}}$ | 0011000 (18) | $S_2$          | 0100110 (26) | $S_0$   |

| , .         | 1100100 (64) | $S_0$            | 1010100 (54) | $S_0$                     | 0011010 (1A) | $S_2$          | 0101000 (28) | $S_0$   |

| ,           | 1100110 (66) | $S_0$            | 1010110 (56) | $S_0$                     | 0011000 (18) | $S_3$          | 0101010 (2A) | $S_0$   |

| ' '         | 1101000 (68) | $S_0$            | 1011000 (58) | $S_0$                     | 0011010 (1A) | $S_3$          | 0110000 (30) | $S_0$   |

| ` ′         | 1101010 (6A) | $S_0$            | 1011010 (5A) | $S_0$                     | 0100000 (20) | $S_0$          | 0110010 (32) | $S_0$   |

|             | 1101100 (6C) | $S_0$            | 1010001 (51) | $S_2$                     | 0100010 (22) | $S_0$          | 0110100 (34) | $S_0$   |

|             | 1000011 (43) | $S_2$            | 1010001 (51) | $S_3$                     | 0101100 (2C) | $S_0$          | 0110110 (36) | $S_0$   |

FIG. 8A1

| 010000 (10) 1100001 (61) | $\overline{S_1}$                  | 1000101 (45) | $\overline{S}_1$ | 0000010 (02) | $S_1$          | [0000100 (04)] | $S_1$                       |

|--------------------------|-----------------------------------|--------------|------------------|--------------|----------------|----------------|-----------------------------|

| ` ′                      | $\mathbf{S_1}$                    | 1000010 (42) | $\mathbf{S}_{1}$ | 0100001 (21) | $S_1$          | 0000110 (06)   | $\mathbf{S}_{1}$            |

| 010001 (11) 1100101 (65) | •                                 | 1000100 (12) | $S_1$            | 0010001 (11) | $S_1$          | 0001000 (08)   | $S_1$                       |

| 010010 (12) 1101001 (69) | $S_1$                             | 1 1          | •                | , ,          | •              | 1 '1           | $S_1$                       |

| 010011 (13) 1101101 (6D) | $S_1$                             | 1000110 (46) | $\mathbf{S}_{1}$ | 0110001 (31) | $S_1$          | 0001010 (0A)   | •                           |

| 010100 (14) 1001011 (4B) | $S_2$                             | 1001000 (48) | $\mathbf{S}_{1}$ | 0001001 (09) | $S_{i}$        | 0010000 (10)   | $\mathbf{S}_{\mathbf{i}}$   |

| 010101 (15) 1011011 (5B) | $S_2$                             | 1001010 (4A) | $\mathbf{S_1}$   | 0101001 (29) | $S_1$          | 0010010 (12)   | $\mathbf{S}_1$              |

| 010110 (16) 1001011 (4B) | $S_3$                             | 1001100 (4C) | $S_1$            | 0011001 (19) | $S_1$          | 0010100 (14)   | $S_1$                       |

| 010111 (17) 1011011 (5B) | $S_3$                             | 1001001 (49) | $S_1$            | 0001100 (0C) | $S_1$          | 0010110 (16)   | $S_1$                       |

| 011000 (18) 1100000 (60) | $S_1$                             | 1010000 (50) | $S_1$            | 0000101 (05) | $\mathbf{S}_1$ | 0100100 (24)   | $S_1$                       |

| 011001 (19) 1100010 (62) | $\mathbf{S}_1$                    | 1010010 (52) | $S_1$            | 0100101 (25) | $S_1$          | 0100110 (26)   | $S_1$                       |

| 011010 (1A) 1100100 (64) | $\mathbf{S}_{\mathbf{i}}^{\cdot}$ | 1010100 (54) | $\mathbf{S}_1$   | 0010101 (15) | $\mathbf{S}_1$ | 0101000 (28)   | $S_1$                       |

| 011011 (1B) 1100110 (66) | $S_1$                             | 1010110 (56) | $S_1$            | 0110101 (35) | $S_1$          | 0101010 (2A)   | $S_1$                       |

| 011100 (1C) 1101000 (68) | $S_1$                             | 1011000 (58) | $\mathbf{S}_1$   | 0001101 (0D) | $S_1$          | 0110000 (30)   | $S_1$                       |

| 011101 (1D) 1101010 (6A) | $S_1$                             | 1011010 (5A) | $\mathbf{S}_1$   | 0101101 (2D) | $S_1$          | 0110010 (32)   | $\mathbf{S}_1$              |

| 011110 (1E) 1101100 (6C) | $S_1$                             | 1010101 (55) | $S_{i}$          | 0100010 (22) | $S_1$          | 0110100 (34)   | $S_1$                       |

| 011111 (1F) 1000011 (43) | $S_3$                             | 1011001 (59) | $S_1$            | 0101100 (2C) | $S_1$          | 0110100 (34)   | $\mathbf{S}_{\mathfrak{t}}$ |

FIG. 8A2

|             | State 0           | $(S_0)$          | State 1 (         | $(S_1)$       | State 2 (         | $(S_2)$        | State 3 (         | $S_3$ )       |

|-------------|-------------------|------------------|-------------------|---------------|-------------------|----------------|-------------------|---------------|

| Data (HEX)  | Codeword<br>(HEX) | Next<br>State    | Codeword<br>(HEX) | Next<br>State | Codeword<br>(HEX) | Next<br>State  | Codeword<br>(HEX) | Next<br>State |

| 100000 (20) | 1100011 (63)      | $S_2$            | 1000101 (45)      | $S_2$         | 0000010 (02)      | $S_2$          | 0000100 (04)      | $S_2$         |

| ` ′         | 0100011 (23)      | $S_2$            | 1000010 (42)      | $S_2$         | 0100001 (21)      | $S_2$          | 0000110 (06)      | $S_2$         |

| ' '         | 0010011 (13)      | $S_2$            | 1000100 (44)      | $S_2$         | 0010001 (11)      | $S_2$          | 0001000 (08)      | $S_2$         |

|             | 0110011 (33)      | $\mathrm{S}_2$   | 1000110 (46)      | $S_2$         | 0110001 (31)      | $S_2$          | 0001010 (0A)      | $S_2$         |

| 100100 (24) | 0001011 (0B)      | $S_2$            | 1001000 (48)      | $S_2$         | 0001001 (09)      | $S_2$          | 0010000 (10)      | $S_2$         |

| 100101 (25) | 0101011 (2B)      | $S_2$            | 1001010 (4A)      | $S_2$         | 0101001 (29)      | $S_2$          | 0010010 (12)      | $S_2$         |

| 100110 (26) | 0011011 (1B)      | $S_2$            | 1001100 (4C)      | $S_2$         | 0011001 (19)      | $S_2$          | 0010100 (14)      | $S_2$         |

| 100111 (27) | 1101011 (6B)      | $S_2$            | 1001001 (49)      | $S_2$         | 0001100 (0C)      | $S_2$          | 0010110 (16)      | $S_2$         |

| 101000 (28) | 1000001 (41)      | $\overline{S_2}$ | 1010000 (50)      | $S_2$         | 0000101 (05)      | $S_2$          | 0100100 (24)      | $S_2$         |

| 101001 (29) | 1100010 (62)      | $S_2$            | 1010010 (52)      | $S_2$         | 0100101 (25)      | $S_2$          | 0100110 (26)      | $S_2$         |

| 101010 (2A) | 1100100 (64)      | $\mathbf{S}_2$   | 1010100 (54)      | $S_2$         | 0010101 (15)      | $S_2$          | 0101000 (28)      | $S_2$         |

| 101011 (2B) | 1100110 (66)      | $S_2$            | 1010110 (56)      | $S_2$         | 0110101 (35)      | $S_2$          | 0101010 (2A)      |               |

| , ,         | 1101000 (68)      | $S_2$            | 1011000 (58)      | $S_2$         | 0001101 (0D)      | $S_2$          | 0110000 (30)      | $S_2$         |

| , ,         | 1101010 (6A)      | $\mathbf{S}_2$   | 1011010 (5A)      | $S_2$         | 0101101 (2D)      | $S_2$          | 0110010 (32)      | $S_2$         |

|             | 1101100 (6C)      | $S_2$            | 1010101 (55)      | $S_2$         | 0100010 (22)      | $S_2$          | 0110100 (34)      | $S_2$         |

| •           | 1010011 (53)      | S <sub>2</sub>   | 1011001 (59)      | $S_2$         | 0101100 (2C)      | S <sub>2</sub> | 0110110 (36)      | $S_2$         |

FIG. 8B1

| 110000 (30) 1100011 (63)  | $S_3$           | 1000101 (45) | $\overline{S_3}$ | 0000010 (02) | $S_3$ | 0000100 (04) | $S_3$ |

|---------------------------|-----------------|--------------|------------------|--------------|-------|--------------|-------|

| 110001 (31) 0100011 (23)  | $.\mathbf{S_3}$ | 1000010 (42) | $S_3$            | 0100001 (21) | $S_3$ | 0000110 (06) | $S_3$ |

| 110010 (32) 0010011 (13)  | $S_3$           | 1000100 (44) | $S_3$            | 0010001 (11) | $S_3$ | 0001000 (08) | $S_3$ |

| 110011 (33) 0110011 (33)  | $S_3$           | 1000110 (46) | $S_3$            | 0110001 (31) | $S_3$ | 0001010 (0A) | $S_3$ |

| 110100 (34) 0001011 (0B)  | $S_3$           | 1001000 (48) | $S_3$            | 0001001 (09) | $S_3$ | 0010000 (10) | $S_3$ |

| 110101 (35) 0101011 (2B)  | $S_3$           | 1001010 (4A) | $S_3$            | 0101001 (29) | $S_3$ | 0010010 (12) | $S_3$ |

| 110110 (36) 0011011 (1B)  | $S_3$           | 1001100 (4C) | $S_3$            | 0011001 (19) | $S_3$ | 0010100 (14) | $S_3$ |

| 110111 (37) 1101011 (6B)  | $S_3$           | 1001001 (49) | $S_3$            | 0001100 (0C) | $S_3$ | 0010110 (16) | $S_3$ |

| 111000 (38) 1000001 (41)  | $S_3$           | 1010000 (50) | $\overline{S_3}$ | 0000101 (05) | $S_3$ | 0100100 (24) | $S_3$ |

| 111001 (39) 1100010 (62)  | $S_3$           | 1010010 (52) | $S_3$            | 0100101 (25) | $S_3$ | 0100110 (26) | $S_3$ |

| 111010 (3A) 1100100 (64)  | $S_3$           | 1010100 (54) | $S_3$            | 0010101 (15) | $S_3$ | 0101000 (28) | $S_3$ |

| 111011 (3B) 1100110 (66)  | $S_3$           | 1010110 (56) | $S_3$            | 0110101 (35) | $S_3$ | 0101010 (2A) | $S_3$ |

| 111100 (3C) 1101000 (68)  | $S_3$           | 1011000 (58) | $S_3$            | 0001101 (0D) | $S_3$ | 0110000 (30) | $S_3$ |

| 111101 (3D) 1101010 (6A)  | •               | 1011010 (5A) | $S_3$            | 0101101 (2D) | $S_3$ | 0110010 (32) | $S_3$ |

| 111110 (3E) (1101100 (6C) | $S_3$           | 1010101 (55) | $S_3$            | 0100010 (22) | $S_3$ | 0110100 (34) | $S_3$ |

| 111111 (3F) 1010011 (53)  | $S_3$           | 1011001 (59) | $S_3$            | 0101100 (2C) | $S_3$ | 0110110 (36) | $S_3$ |

|                           |                 |              |                  |              |       |              |       |

FIG. 8B2

#### METHOD AND APPARATUS FOR IMPLEMENTING CODES WITH MAXIMUM TRANSITION RUN LENGTH

#### BACKGROUND OF THE INVENTION

The present invention relates in general to information storage systems and, more particularly, to a method and apparatus for implementing maximum transition run (MTR) codes in a digital data magnetic recording system. In digital data magnetic recording systems, digital data is recorded in a moving magnetic media layer by a storage, or "write" electrical current-to-magnetic field transducer, or "head", positioned immediately adjacent thereto. The data is stored or written to the magnetic media by switching the direction of flow of a substantially constant magnitude write current which flows through windings in the write transducer. Each write current direction transition results in a reversal of the magnetization direction in that portion of the magnetic media just passing by the transducer during current flow in the new direction, with respect to the magnetization direction in the media induced by the previous current flow in the opposite direction. In one scheme (NRZI), a magnetization direction reversal over a portion of the media moving past the transducer represents a binary digit "1", and the lack of any reversal in that portion represents a binary digit "0".

When such recorded data is to be recovered, a retrieval, or "read" magnetic field-to-voltage transducer, (which may be the same as the write transducer if both are inductive) is positioned to have the magnetic media, containing previously stored data, pass thereby such that flux reversal regions in that media either induce, or change a circuit parameter to provide, a voltage pulse to form an output read signal for that transducer. Such a read signal has an analog character in the recording retrieval process. In the scheme 35 described above, each such voltage pulse due to the magnetizations in corresponding media portions is taken to represent a binary digit "1" and the absence of a pulse in correspondence with such portions because of no magnetization reversals therein is taken to represent a binary digit 40 "0".

In digital magnetic recording systems, the times between voltage pulses are used to reconstruct the timing information concerning the time base used in recording the data previously stored in the magnetic media to define the path 45 portions described above. More specifically, the output of the read signal information detector is used as an input signal to a phase-locked loop forming a controlled oscillator, or phase-lock oscillator (PLO), or synchronizer, which produces an output clock signal from the positions of the 50 detected peaks of the read signal. In other words, the PLO locks the phase of the timing clock signal to the phase of the signal resulting from peak detection of the read signal voltage pulses. Absolute time is not used in operating the motor which drives the magnetic media varies over time both during recording and retrieval which results in nonuniform time intervals between read signal voltage pulses.

A data encoding scheme known as run-length-limited (RLL) coding is commonly used to improve the PLO's 60 word, there are exactly 24 or 16 words which remain. This reconstructed clock signal accuracy based on avoiding drift in the frequency thereof because of too much time occurring between successive voltage read signal pulses. When RLL code is employed, the time durations between read signal number of binary digits of value "0" that can separate binary digits of value "1" in the read signal is limited. This

constraint is known overall as a (d,k) constraint where the individual constraint "d" represents the minimum run length of zeros, or the number thereof between ones, while the individual constraint "k" represents the maximum run length of zeros permitted. The "d" portion of the constraint can be chosen so as to avoid crowding of voltage pulses in the read signals which can reduce intersymbol interference problems in which portions of read signal voltage pulses overlap. By limiting the number of consecutive zeros, the "k" constraint maintains the reliability of the PLO in providing an accurate clock signal for the retrieval system. An automatic gain control (AGC) system is usually used to maintain signal amplitude in the retrieval signal processing channel, and the "k" restraint also maintains the reliability of the AGC.

As the recording densities become greater, the result is that transitions representing binary "1's" become recorded very close to each other in the magnetic media such that severe intersymbol-interference results. At densities considerably greater than those in currently commercially available products, the most likely error sequence has been demonstrated to consist of write patterns that contain three or more unspaced consecutive transitions. A class of block codes that limits the number of consecutive symbol transitions, typically representing binary "1's", are known as maximum transition run (MTR) codes. To avoid three or more consecutive transitions, codes with MTR values (no more than two successive binary "1's" in the coding result) equal to two are desirable.

When data is encoded into codewords that satisfy certain 30 constraints, data words (blocks of successive coding symbols typically binary "1's" and "0's") having "m" successive bits are translated into code words (blocks of successive coding symbols again typically binary "1's" and "0's") having "n" bits where "n" is greater than "m". The ratio "m/n" of the data word symbol length to the codeword symbol length is known as the code rate, "r". The upper bound of the MTR=2 code rate in which k=∞ has been found to be 0.8791 as indicated in the Seagate Annual Report. This upper bound is also known as the capacity of the code. This means there exists MTR codes with MTR=2 that map m data bits into n code bits as long as the ratio of m to n is smaller than 0.8791. For practical implementation, m and n are usually chosen to be small integers and the ratio m/n is as close to the code capacity as possible.

To design a MTR code with MTR=2 having a rate of m/n and using one-to-one block mapping in which the "m" data symbols, or binary data bits, in a block are mapped into the "n" code symbols, or binary data bits, in a block, an exhaustive search of the possible n bit blocks is used to find 2<sup>m</sup> different n-bit words which satisfy the MTR=2 constraint. In addition, in order for these words to satisfy the MTR=2 constraint when concatenated as code words, the bit patterns therein must begin and end with '00', '01' or '10'. That is, bit patterns can be considered in these words found data retrieval system portion since the rotational speed of the 55 in the exhaustive search which start or end with '11' and those words can be invalidated insofar as being used as code words. For instance, if n=5 and if one removes all the 5-bit words having three or more consecutive "1's", having bit patterns that start or end with '11', and the all zero bit pattern is just enough to form a 4/5 rate MTR code with MTR=2 using one-to-one mapping between the data words and the

However, when attempting to extend this method to a 5/6 voltage pulse transitions is bounded, that is, effectively, the 65 rate MTR code with MTR=2, there are only thirty words with valid bit patterns available, two short of the 2<sup>5</sup> or 32 words required. Although one may achieve the same code

rate by mapping 10-bit data words to 12-bit data words, the 2<sup>10</sup> or 1024 code words will significantly complicate the encoder and decoder which use Boolean logic to implement the bit pattern mapping. Thus, in the context of the above example, there is a desire to provide an encoding algorithm 5 which satisfies the MTR=2 constraint that is easy to implement using Boolean logic and is not limited by invalid patterns beginning or ending with '11'. Of course, the present invention is not limited to such codes which satisfy the MTR=2 constraint, but rather is applicable to any such 10 code regardless of the coding constraints chosen.

#### SUMMARY OF THE INVENTION

The present invention provides a system for encoding selected data blocks having selected ordered symbols therein 15 into corresponding code blocks having selected ordered symbols therein numbering more than the symbols in the data blocks with the data blocks received at a receiver in the system. An encoder provides a corresponding said code block for each of the data block, such that each of the code 20 blocks, and any concatenations thereof, are without more than a preselected number of successive repetitions of a first symbol throughout, and without more than a preselected number of successive repetitions of a second symbol throughout. In addition, any of said code blocks that can be 25 provided for more than one of different ones of the data blocks, in coming to the receiver to represent a data block, comes in a concatenation of code blocks such that such that a code block that can represent more than one different data block comes to the receiver together with at least one other 30 code block in the concatenation so that they are together sufficient to determine which of the different ones of the data blocks that could be represented is being represented. The symbols in the blocks can be from the binary number

#### BRIEF DESCRIPTION OF THE DRAWINGS

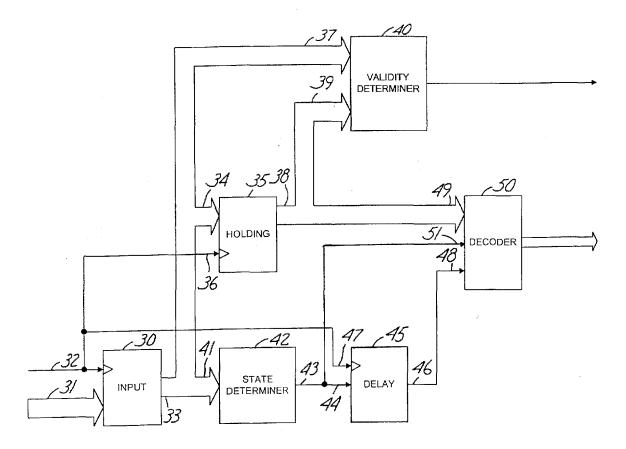

FIG. 1 is a two-state trellis diagram for associating concatenated code word bit patterns with each other according to the present invention;

FIG. 2 is a table illustrating all of the 6 obit binary patterns which satisfy the MTR=2 constraint according to the present invention:

FIG. 3 is a code word assignment and next state table of a 5/6 rate MTR=2, k=9 code according to the present 45 invention:

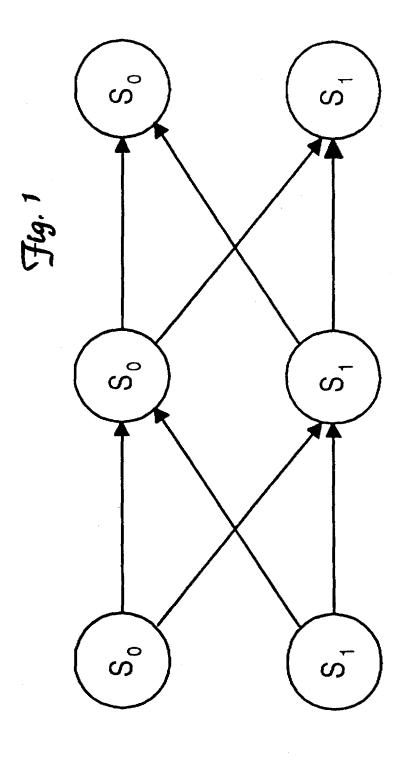

FIG. 4A is a block diagram of an encoder for the 5/6 rate code of FIG. 3;

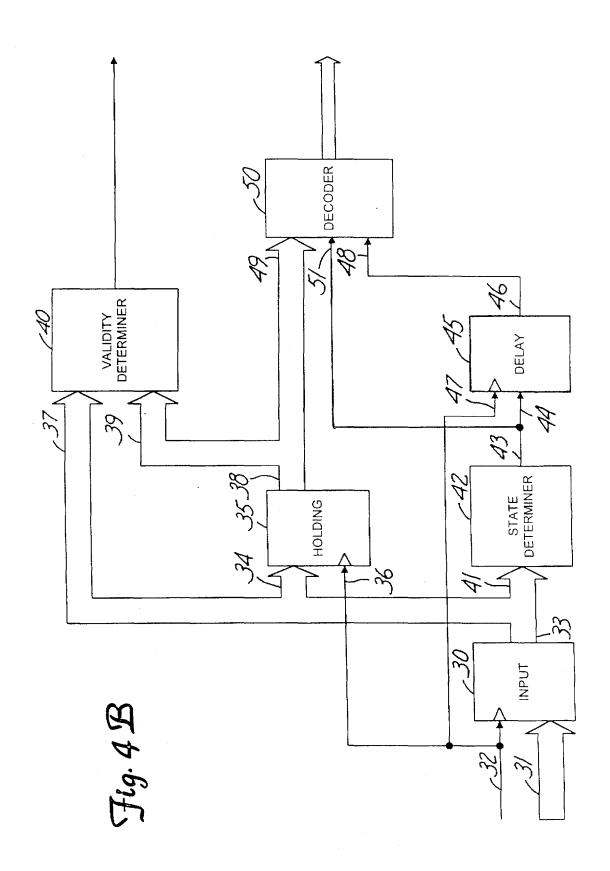

FIG. 4B is a block diagram of a decoder for the 5/6 rate code of FIG. 3;

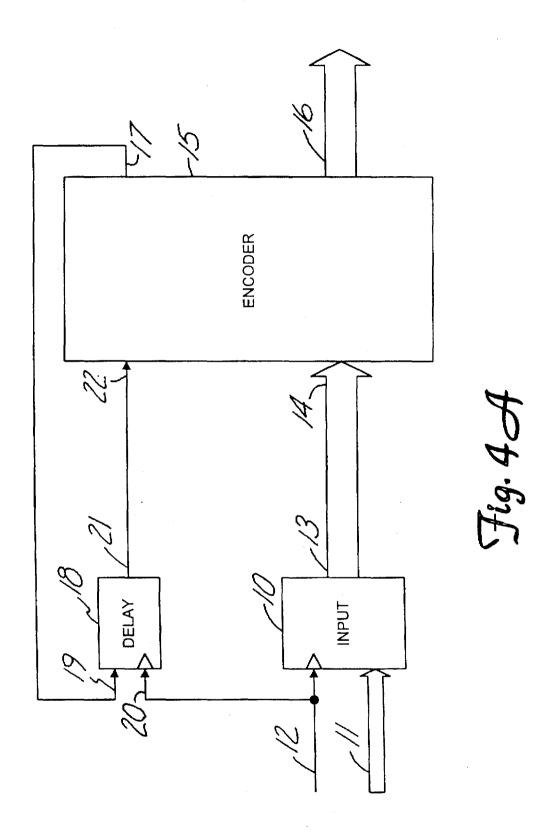

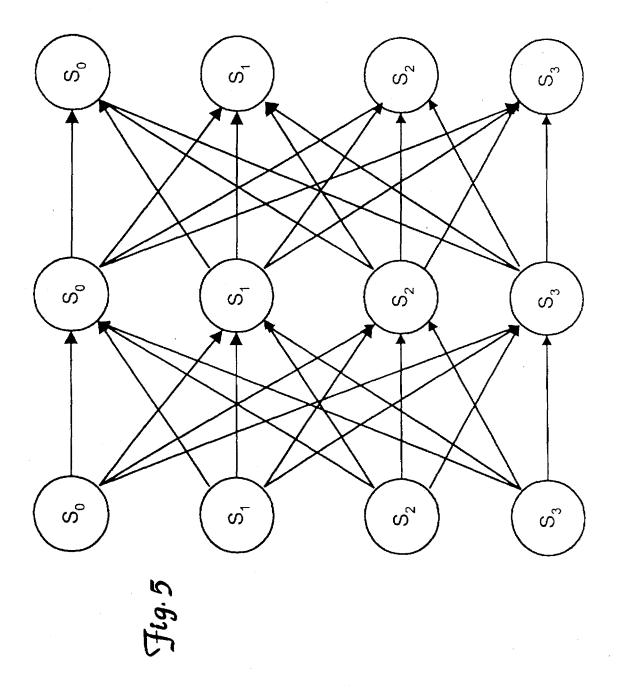

FIG. 5 is a four-state trellis diagram for associating concatenated code word bit patterns with each other according to another embodiment of the present invention;

FIG. 6 is a table illustrating all of the 7-bit binary patterns which satisfy the MTR=2 constraint according to the present invention:

FIG. 7 is a table of sub-groups of the 7-bit patterns which satisfy the MTR=2 constraint according to the present invention:

FIGS. 8A and 8B are a code word assignment and next state table of a 6/7 rate MTR=2, k=9 code according to the present invention;

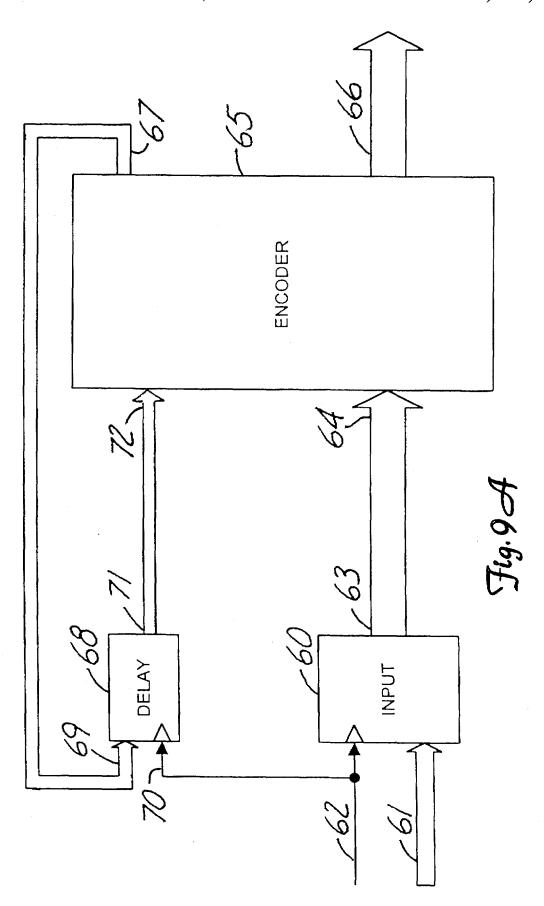

FIG. 9A is a block diagram of an encoder for the 6/7 rate code of FIG. 8; and

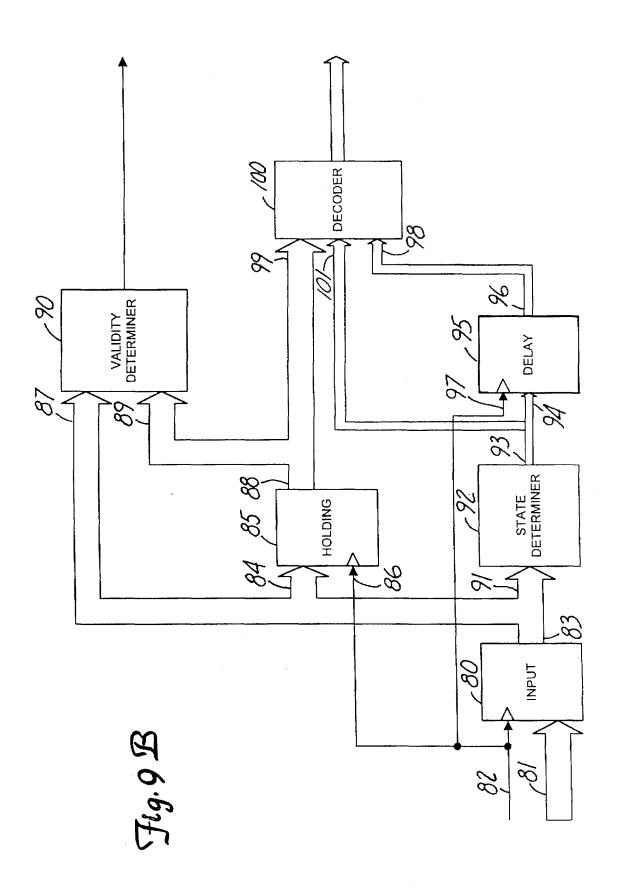

FIG. 9B is a block diagram of a decoder for the 6/7 rate code of FIG. 8.

4

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

To achieve a m/n rate equal to 5/6 in an MTR code with MTR=2 using code words of 6 bits in length (n=6), an initial list is provided of all such 6 bit words including those that begin or end with bit patterns '11'. According to the present invention, these 6-bit words are assigned to branchings to the next state during a state transition from a selected corresponding state in a finite state machine represented by a two-state trellis diagram in such a manner that invalid patterns (three or more consecutive 1's) do not occur when these code words are concatenated. Referring to FIG. 1, the two states in the trellis diagram are indicated there as state So and state S1 which have been found to be sufficient in number for this code. Two branches are shown leading into and out of each of the states So and S1 if viewed across the entire diagram, but with each of the branches shown in fact representing several branches in parallel.

As shown in FIG. 2, an exhaustive search of this initial list is made to find all of the 6-bit words in the list having bit patterns therein which satisfy the MTR=2 constraint results in the listing shown there after being divided into four selected groups of words based on selected bit patterns in those words:

Group A: '1XXXX1' (9 different words),

Group B: '1XXXX0' (11 different words),

Group C: '0XXXX1' (11 different words),

Group D: '0XXXX0' (12 different words),

where  $\hat{X}$  represents either a "1" or an "0". This grouping is, as indicated, based on the bit patterns of the two end bits in each of these words.

In order to limit the resulting code to having the MTR value therefor equal to two in concatenations of the code words resulting from successive transmissions thereof, constraints are imposed on the transition branches in the trellis diagram so that the branches may only be associated with certain code words having suitable bit patterns to avoid the occurrence of three or more successive "1's". If all code words arising upon state transitions leaving states along branches leading to a state So in the diagram have bit patterns that are restricted to those that end with '0', code words arising upon a subsequent state transition along branches leaving that So state can be from any group. If all code words arising upon state transitions along branches leaving a state  $S_1$  in the diagram have bit patterns that are restricted to those that begin with '0', code words arising in an immediately preceding state transition along branches leading to that state S<sub>1</sub> can be from any group. As a result of following these constraints, the above code word groups are acceptable to arise along each branch as listed below:

S<sub>0</sub> to S<sub>0</sub> Branch: Groups B and D (end with "0"),

S<sub>0</sub> to S<sub>1</sub> Branch: Groups A, B and D (all but these chosen to allow a unique state assignment as set out below)

$S_1$  to  $S_0$  Branch: Groups D (begin and end with "0"),

S<sub>1</sub> to S<sub>1</sub> Branch: Groups C and D (begin with "0").

In order to make the code words uniquely decodable and limit the error propagation, code words arising upon leaving each state in a state transition must be unique. That means each code word cannot be used upon transitions from more than one state. Groups A and B are assigned so that code words arise therefrom upon state transitions along branches leaving just state  $S_0$  in view of their association with branches leaving that state as shown above, and Groups C and D are assigned so that code words arise therefrom upon state transitions along branches leaving state  $S_1$  for that

same reason. However, since this is a 5/6 rate code, 2<sup>5</sup> or 32 different code words are necessary for transitions from each state so that a data word can be represented by each such transition, but code words assigned for branchings from a selected state can be repeated for branchings from that state to each of the different next states branched to therefrom since they will still be uniquely decodable because of their differing next state characteristics. The use of the fewest states possible, of course, tends to reduce complexity and cost.

One code word '011010' from Group D is therefore moved to arise on transitions from state  $S_0$  (which group is also associated with branches leaving that state in the second listing above) to thereby provide 32 code words available to arise on transitions from that state. As a result, that moved code word now forms Group D" leaving the rest of former Group D to now form Group D'. The code words are, as a result, distributed to the branches as follows:

From S<sub>0</sub> to S<sub>0</sub>: B (11 different words) and D" (1 word), From S<sub>0</sub> to S<sub>1</sub>: A (9 different words) and B (11 different 20 words),

From  $S_1$  to  $S_0$ : D' (11 different words),

From S<sub>1</sub> to S<sub>1</sub>: C (11 different words) and D' (11 different words).

There is thus a total of 32 code words for branchings from 25 state  $S_0$ , and 33 words for branchings from state  $S_1$  thus showing two states in the finite state machine to be sufficient. To keep the "0's" run length "k" constraint small, we may eliminate the former code word '000001' from Group C to form Group C' and so then leave 32 code words for 30 branchings from state  $S_1$  also. FIG. 3 shows the next state table of the resulting maximum transition run code having a 5/6 rate with MTR=2 and k=9, providing the next state and code word corresponding to each data word for branchings from both of states  $S_0$  and  $S_1$  during state transitions, and 35 showing the corresponding hexadecimal value for these words. The k=9 constraint is equaled when the code words '100000' and '000010' occur successively in a transmission thereof.

Since the code words are unique to the branchings from 40 each state, the decoder will only have to look ahead one code word. For example, the code word '36' (hex) may be received by the decoder. This code word from the table of FIG. 3 can be seen there to be the possible result of either data words '07' or '17' (hex). To determine which, the 45 decoder must check on the next code word and determine whether it was associated branchings from either state  $S_0$  or state  $S_1$  as it is uniquely associated with one or the other. If the next code word is one resulting from a branching from state S<sub>0</sub>, the data word '07' (hex) will be the decoded output 50 since state S<sub>0</sub> was the next state of the preceding code word '36' (hex) now being decoded that represented data word '07' (hex), otherwise the next code word is from state S<sub>1</sub> and data word '17' (hex) is decoded. Errors confined to a single code word will thus only affect two decoded data words, that 55 data word represented by the erroneous code word and the preceding data word for which the erroneous code word was the next code word.

The logic structures of the encoder and decoder for the maximum transition run code set out in the table of FIG. 3, 60 having a rate 5/6 with MR=2 and k=9, can be expressed in Boolean logic expressions in which a "\*" between Boolean variables denotes an AND logic operation, a "+" between Boolean variables denotes an OR logic operation, and a "-" over a Boolean variable denotes a NOT logic operation. 65 These Boolean functions can be implemented into such encoders and decoders by well known logic gate circuits in

well known manners based on forming a finite state machine therewith. Alternatively, such encoders and decoders can be similarly implemented in a microprocessor, or microprocessors, in well known manners.

In the encoder system shown in block diagram form in FIG. 4A, each input data word of five bits  $A_4$ ,  $A_3$ ,  $A_2$ ,  $A_1$  and A<sub>0</sub> is successively supplied to a clocked five bit input register, 10, as the data word receiver at a system input, 11, during a corresponding period of the system clocking signal 10 supplied at a clock signal input, 12. Each such input data word stored in input register 10 is transferred during the next clock period from an output, 13, of that register into an input, 14, of an encoder, 15, comprising a finite state machine based on the table in FIG. 3 to be encoded into a code word of six bits C<sub>5</sub>, C<sub>4</sub>, C<sub>3</sub>, C<sub>2</sub>, C<sub>1</sub> and C<sub>0</sub> provided at a code word output, 16, of that encoder. From the table of FIG. 3, we can see the input data words are divided into two groups. The first group of data words extends '00' to '0A' (hex) and, for state transitions from either state So or state S1, has state So as its next state. The second group of data words extends from '0B' to '1F' (hex) and, for state transitions from either state  $S_0$  or state  $S_1$ , has state  $S_1$  as its next state. Data words can be identified as being from two sublists in the data word listing, data words in the listing from '00' (hex) to '0A' (hex) and from '10' (hex) to '1A' (hex), by the following expression taking a Boolean value of 1:

$$KK = \overline{A}_3 + (\overline{A}_2 * (\overline{A}_1 + \overline{A}_0)).$$

[Eq. 1]

Since data words in this first group for state transitions from either state  $S_0$  or state  $S_1$  have the next state as  $S_0$ , and the data words from the second group do not, negating KK and placing it in an OR relationship with the fourth data word digit  $A_4$  allows the next state to be expressed by the equation

$$N_{S}=\overline{KK}+A_{4}$$

[Eq. 2]

for use in encoder 15. Ns=0 represents state  $S_0$  as the next state, and Ns=1 represents state  $S_1$  as the next state.

The bits of the code words arising on branchings from state  $S_0$  during state transitions as set out in the table of FIG. 3 can be expressed as follows for use in encoder 15:

$$Y_{A_5} = KK + \bar{A}_4 + A_4 * (\bar{A}_2 + \bar{A}_2 + \bar{A}_0),$$

[Eq. 3]

$$Y_{A_4} = KK * (A_3 + A_2 * A_1 * A_0) + \overline{KK} * (A_4 * A_2)$$

[Eq. 4]

$$Y_{A_3} = KK * (A_2 * (\bar{A}_1 + \bar{A}_0)) + \overline{KK} * (\bar{A}_4 * A_2 * A_1 + A_4 * A_1 * A_0),$$

[Eq. 5]

$$Y_{A_2} = KK * A_1 + \overline{KK} * (H_{13} + A_4 * H_{11}),$$

[Eq. 6]

$$Y_{A_1} = KK * A_0 + \overline{KK} * (H_{12} + H_{15}),$$

[Eq. 7]

$$Y_{A_0} = \overline{KK} * (\bar{A}_4 + \bar{H}_{15}),$$

[Eq. 8]

where the corresponding Boolean variables  $\mathbf{H}_{x}$  are defined below.

The bits of the code words arising on branchings from state  $S_1$  during state transitions as set out in the table of FIG. 3 can be expressed as follows again for use in encoder 15:

$$YB_{5}=0, \qquad [Eq. 9]$$

$$YB_{4}=KK^{*}(A_{3}+A_{2}*A_{1}*A_{0})+KK^{*}H_{0}+\overline{KK}*A_{4}, \qquad [Eq. 10]$$

$$YB_{3}=KK^{*}(A_{2}*(\overline{A}_{1}+\overline{A}_{0})+H_{0})+\overline{KK}^{*}(\overline{A}_{4}A_{2}*A_{1}+A_{4}*A_{1}), \qquad [Eq. 11]$$

$$YB_{2}=KK^{*}A_{1}+\overline{KK}^{*}(H_{13}+A_{4}*H_{11}), \qquad [Eq. 12]$$

$$YB_{1}=KK^{*}A_{0}+\overline{KK}^{*}(H_{12}+H_{15}), \qquad [Eq. 13]$$

The corresponding Boolean variables  $H_x$  used in the preceding encoding expressions for the code word bits are defined as follows:

$$H_0 = \bar{A}_3 * \bar{A}_2 * \bar{A}_1 * \bar{A}_0$$

, [Eq. 15]

$H_{11} = A_3 * \bar{A}_2 * A_1 * A_0$ , [Eq. 16]

$H_{12} = A_3 * A_2 * \bar{A}_1 * \bar{A}_0$ , [Eq. 17] 10

$H_{13} = A_3 * A_2 * \bar{A}_1 * A_0$ , [Eq. 18]

$H_{15} = A_3 * A_2 * A_1 * A_0$ . [Eq. 19]

The output code words of the encoder are provided by the  $^{15}$  code word bits  $C_5$ ,  $C_4$ ,  $C_3$ ,  $C_2$ ,  $C_1$  and  $C_0$  formed by selecting the proper one of the corresponding preceding code word bit expressions from the two sets thereof through use of the next state expression associated therewith delayed by one state transition (or one system clock period) to  $^{20}$  provide the current state indication therefor, the expressions for the six code word bits being as follows:

| $C_5 = \bar{K}_S * YA_5 + K_S * YB_5,$  | [Eq. 20] |

|-----------------------------------------|----------|

| $C_4 = \bar{K}s * YA_4 + Ks * YB_4,$    | [Eq. 21] |

| $C_3 = \bar{K}s * YA_3 + Ks * YB_3,$    | [Eq. 22] |

| $C_2 = \bar{K}s * YA_2 + Ks * YB_2,$    | [Eq. 23] |

| $C_1 = \bar{K}s * YA_1 + Ks * YB_1,$    | [Eq. 24] |

| $C_0 = \bar{K}_S * Y A_0 + K_S * Y B_0$ | [Eq. 25] |

Here Ks is a bit representing the current state, and it is the bit Ns provided at a next state output, 17, of encoder 15 35 delayed by one state transition, or clock period, in a clocked one bit delay register, 18, having its next state input, 19, connected to encoder output 17. The system clock signal is also provided to register 18 at a clocking input, 20, thereof. An output, 21, of register 18 is connected to a current state 40 input, 22, of encoder 15.

In the corresponding decoder system for this 5/6 rate MTR code shown in block diagram form in FIG. 4B, output data words formed of five bits A<sub>4</sub>, A<sub>3</sub>, A<sub>2</sub>, A<sub>1</sub> and A<sub>0</sub> are recovered based on successive pairs of input code words of 45 six bits each taken from a sequence thereof where each input code word in such a pair occurs in succession the sequence thereof. Current code words, provided by bits C<sub>5</sub>, C<sub>4</sub>, C<sub>3</sub>, C<sub>2</sub>, C<sub>1</sub> and C<sub>0</sub>, carry the information as to corresponding current states of the encoder, and the code word next following the 50 current code word, provided by the bits C<sub>11</sub>,C<sub>10</sub>,C<sub>9</sub>,C<sub>8</sub>,C<sub>7</sub>, and C<sub>6</sub>, carries the information as to the corresponding next encoder state. Together, they point to the corresponding unique data word to result from the decoding process in the decoder.

In this decoder system, each input code word of six bits is successively supplied to a clocked six bit input register, 30, at a system input, 31, during a corresponding period of the system clocking signal supplied at a clock signal input, 32. Each such input data word stored in input register 30 60 represents the following or next code word  $(C_{11}, C_{10}, C_{9}, C_{8}, C_{7}, C_{6})$  after storage in input register 30, but is transferred during the next clock period from an output, 33, of that register into an input, 34, of another clocked six bit holding register, 35, where it becomes the current code word  $(C_{5}, C_{4}, 65 C_{3}, C_{2}, C_{1}, C_{0})$  after storage therein. The system clock signal is also applied to a clocking input, 36, of register 35. The

8

new input code word stored in input register 30 during the time the preceding code word is stored in holding register 35 then becomes the next code word during the time held in register 30.

The code word in input register 30, as the next code word, is also supplied at output 33 thereof to a first input, 37, as is the current code word from an output, 38, of delay register 35 to a second input, 39, of a code word legality checker, 40. If the six code bits in any code word received form an illegal code word representing an eliminated six bit word (any of the words that were eliminated in forming Groups A, B, C, (D' and D" above), a flag signal taking a Boolean value of 1 at the output of checker 40 will indicate so as a basis for a user to arrange some corresponding action if desired. This flag signal LL as implemented in checker 40 can be expressed as:

$$LL=L_1+L_2+L_3+L_4,$$

[Eq. 26]

where

25

30

$$L_1 = C_5 * C_4 * C_3 + C_4 * C_3 * C_2 + C_3 * C_2 * C_1 + C_2 * C_1 * C_0,$$

[Eq. 27]

$$L_2 = \bar{C}_5 * \bar{C}_4 * \bar{C}_3 * \bar{C}_2 * \bar{C}_1,$$

[Eq. 28]

$$L_3 = C_{11} * C_{10} * C_9 + C_{10} * C_9 * C_8 + C_9 * C_8 * C_7 + C_8 * C_7 * C_6,$$

[Eq. 29]

$$L_4 = \bar{C}_{11} * \bar{C}_{10} * \bar{C}_9 * \bar{C}_8 * \bar{C}_7.$$

[Eq. 30]

The current states of the received code words imposed by the encoder can be expressed by the equations:

$$Ts_0 = (C_5 * C_0) + (C_5 * \bar{C}_0) + (G_1 * H_{10}),$$

[Eq. 31]

$$Ts_1 = (\overline{C}_5 * \overline{C}_0) + (\overline{C}_5 * \overline{C}_0 * (\overline{C}_4 + C_4 * (\overline{C}_3 + (C_3 * \overline{C}_1)))),$$

[Eq. 32]

where  $G_1$  and  $H_{10}$  are defined below.  $Ts_0=1$  indicates state  $S_0$  is the current state and  $Ts_1=1$  indicates state  $S_1$  is the current state. These two states can be represented in one bit by Ks by

$$Ks=Ts_1$$

. [Eq. 33]

Rather than using the expression preceding the last directly to form the last expression to obtain the current state, the decoder system determines the next state and then delays use of it for one state transition to thereby then have it represent the current state. This is accomplished through the code word in input register 30, as the next code word, being also supplied at output 33 thereof to an input, 41, of a state determiner, 42. The next states of the encoder corresponding to the input code words received in input register 30 can be expressed by the equation:

$$Ns = (\overline{C}_{11} * C_6) + (\overline{C}_{11} * \overline{C}_6 * (\overline{C}_{10} + C_{10} * (\overline{C}_9 + (C_9 * \overline{C}_7)))).$$

[Eq. 34]

Ns=0 indicates state  $S_0$  is the next state, and Ns=1 indicates state  $S_1$  is the next state. This expression, implemented in determiner 42, provides the next state at an output, 43, thereof connected to an input, 44, of a clocked one bit delay register, 45, having an output, 46, at which is provided the current state indication. Delay register 45 also has a further clocking input, 47, to receive the system clock signal.

Output 46 of delay register 45 is connected to a first input, 48, and output 38 of holding register 35 is connected to a second input, 49, of a decoder, 50, to thereby provide the current state indication and the current code word to that decoder. In addition, output 43 of state determiner 42 is connected to decoder 50 at a third input, 51, thereof to provide the next state indication thereto. For the implementation of the decoding logic gates in decoder 50, the code

words are divided into four groups A'=A+D", B, C and D' as described above taking into account the final adjustments made in the assignment of code words to transition branchings from the states. Code words can be identified as belonging to these groups by the corresponding variables  $K_a$ ,  $K_b$ ,  $K_c$  and  $K_d$  in the expressions below taking a Boolean value of 1:

| Group A') $K_a = (C_5 * C_0) + (G_1 * H_{10}),$                                                                            | [Eq. 35] |

|----------------------------------------------------------------------------------------------------------------------------|----------|

| Group B) $K_b = C_5 * \bar{C}_0$ ,                                                                                         | [Eq. 36] |

| Group C') $K_c = (\overline{C}_5 * C_0) * (C_4 + C_3 + C_2 + C_1),$                                                        | [Eq. 37] |

| Group $D'$ ) $K_d = \overline{C}_5 * \overline{C}_0 * (\overline{C}_4 + C_4 * (\overline{C}_3 + (C_3 * \overline{C}_1))).$ | [Eq. 38] |

Here, the code word taken from Group D to thereby form Group D" as described above has been added to Group A to form Group A' leaving Group D' consisting of the rest of former Group D. Group C' is formed from Group C less the word eliminated therefrom above.

The data word bits recovered from received code words arising on branchings from state  $S_0$  during state transitions as set out in the table of FIG. 3 can be expressed as follows for use in decoder 50 based on the variables for identifying code words from Groups A' and B:

where the corresponding Boolean variables  $G_x$  and  $H_x$  are defined below.

The data word bits recovered from received code words arising on branchings from state  $S_1$  during state transitions as set out in the table of FIG. 3 can be expressed as follows again for use in decoder 50 but based on the variables for identifying code words from Groups C and D":

| $XB_4 = (K_c * \bar{C}_4) + (K_d * N_s),$                                                                                                               | [Eq. 44] |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| $XB_3 = K_c + (K_d^*(C_4^*\bar{C}_3^*(\overline{C}_2 + \bar{C}_1))),$                                                                                   | [Eq. 45] |

| $XB_2\!\!=\!\!(K_c\!\!*\!\!\bar{H}_1\!\!*\!\!\bar{H}_{13})\!\!+\!\!(K_d\!\!*\!\!((\overline{C}_4\!\!*\!\!C_3)\!\!+\!\!(C_4\!\!*\!\!C_2\!\!*\!\!C_1))),$ | [Eq. 46] |

| $XB_1 = (K_c * (C_3 + H_1)) + (K_d * C_2),$                                                                                                             | [Eq. 47] |

| $XB_0 = (K_c * (C_2 + H_1 + H_{11})) + (K_d * C_1).$                                                                                                    | [Eq. 48] |

The corresponding Boolean variables  $G_x$  and  $H_x$  used in the preceding decoding expressions for the data word bits are defined as follows:

| [Eq. 50]<br>55 |

|----------------|

| [Eq. 51]       |

| [Eq. 52]       |

| [Eq. 53]       |

| [Eq. 54]       |

| [Eq. 55]       |

| [Eq. 56]       |

|                |

The output data words of the encoder are provided by the code word bits  $A_4, A_3, A_2, A_1$  and  $A_0$  at the output of decoder

50 formed by selecting the proper one of the corresponding two preceding data word bit expressions through use of the next state expression delayed by one state transition (or one system clock period) to provide the current state indication, the expressions therefor being as follows:

| $A_4 = \overline{K}s * XA_4 + Ks * XB_4,$ | [Eq. 57] |

|-------------------------------------------|----------|

| $A_3 = \bar{K}_S * XA_3 + K_S * XB_3,$    | [Eq. 58] |

| $A_2 = \bar{K}s * XA_2 + Ks * XB_2,$      | [Eq. 59] |

| $A_1 = \overline{K}s * XA_1 + Ks * XB_1,$ | [Eq. 60] |

| $A_0 = \overline{K}s * XA_0 + Ks * XB_0,$ | [Eq. 61] |

Ks is the current state indication provided at the output of delay register 45.

A further maximum transition run code example is provided by such a code having a 6/7 rate with MTR=2 and k=9 using a 4-state trellis diagram as shown in FIG. 5 with again the branches shown representing several branches in parallel. To implement this code, all of the possible 7-bit blocks or words, excluding those not satisfying MTR=2, are divided into four groups of possible code words based on those bit patterns involving the end bits of each such word just as was done for the 5/6 rate code design above. As a result, there are 17 such blocks or words in Group A with the bit pattern given therefor above, 20 such words in each of Groups B and C with the bit patterns corresponding to those patterns given above for those groups, and 23 such words in Group D with the corresponding bit pattern given therefor above, as shown in the table of FIG. 6. A 6/7 rate code needs 26 or 64 different code words for transitions from each state so that a different data word can be represented by each such transition from a state. The code words in these four groups have been found to be insufficient in number to implement such a code with this rate using either a 2-state or 3-state trellis.

To implement this code in a finite state machine represented by a 4-state trellis, we further restrict certain words for branchings from each state. Words arising on branchings from state S<sub>0</sub> may begin with any two bits including '11', and so words arising on branchings leading to state So must end with '0' to satisfy MTR=2 in code word concatenations arising from branchings into and out of that state. Words arising on branchings from state S<sub>1</sub> may only begin with '10', and so words arising on branchings to state S<sub>1</sub> may end with '00' or '01' again to satisfy MTR=2 in code word concatenations arising from branchings into and out of that state. Words arising on branchings from either of states S<sub>2</sub> and S<sub>3</sub> only begin with '0', and so any words arising on branchings leading to states S<sub>2</sub> and S<sub>3</sub> are satisfactory. With these restrictions, the four groups of words indicated above can be further divided into subgroups as follows:

```

Group A:

Group AA: '11XXX11' (2 different words),

Group AB: '11XXX01' (4 different words),

Group AC: '10XXX11' (4 different words),

Group AD: '10XXX01' (7 different words),

Group B:

Group BD: '10XXXX0' (13 different words),

Group BB: '11XXXX0' (7 different words),

Group C:

Group CD: '0XXXX01' (13 different words),

Group CC: '0XXXXX11' (7 different words),

Group D: '0XXXXX0' (23 different words),

```

where X='0' or '1'. Again, code words arising from branchings from in each state must be unique in order for the code

Page 21

11

words to be uniquely decodable and to limit any error propagation. Group D is further divided into two groups (D' and D") such that sixteen words therein are used in one state and the other seven words are used in another state. To satisfy the 64 different words per state requirement, we may 5 assign the words to branches as follows:

From S<sub>0</sub> to S<sub>0</sub>: BB (7 different words),

From S<sub>0</sub> to S<sub>1</sub>: AB and BB (4+7=11 different words),

From S<sub>0</sub> to S<sub>2</sub>: AA, AB, AC, BB and CC (2+4+4+7+7=24 different words),

From  $S_0$  to  $S_3$ : AA, AB, AC, BB and CC (2+4+4+7+7=24 different words),

From  $S_1$  to  $S_0$ : BD (13 different words),

From  $S_1$  to  $S_1$ : AD and BD (7+13=20 different words), 15

From S<sub>1</sub> to S<sub>2</sub>: AD and BD (7+13=20 different words),

From S<sub>1</sub> to S<sub>3</sub>: AD and BD (7+13=20 different words),

From  $S_2$  to  $S_0$ : D' (7 different words),

From  $S_2$  to  $S_1$ : CD and D' (13+7=20 different words),

From S<sub>2</sub> to S<sub>2</sub>: CD and D' (13+7=20 different words),

From  $S_2$  to  $S_3$ : CD and D' (13+7=20 different words),

From  $S_3$  to  $S_0$ : D" (16 different words),

From  $S_3$  to  $S_1$ : D" (16 different words),

From S<sub>3</sub> to S<sub>2</sub>: D" (16 different words),

From S<sub>3</sub> to S<sub>3</sub>: D" (16 different words).

There is a total of 66 different words for S<sub>0</sub>, a total of 73 different words for  $S_1$ , a total of 67 different words for  $S_2$ , and a total of 64 different words for S<sub>3</sub> as shown in the table of FIG. 7. This satisfies the minimum requirement of a total 30 of 64 different words per state with some to spare. Some adjustment can be made in order to keep the "k" constraint small. Words '1000000' from Group BD and '0000001' from Group CD are eliminated to avoid long runs of zero to form Groups BD' and CD'. Word '1000001' of Group AD is 35 moved to transition from state S<sub>0</sub>. Word '0000011' of Group CC is moved to transition from state S2. FIG. 8 shows the next state table of the resulting maximum transition run code having a 6/7 rate with MTR=2 and k=9. The k=9 constraint is equaled when either of the code words '1010000' or  $^{40}$ '0010000' is followed by either of code words '0000010' or '0000011' in sequence.

In the encoder for implementing this maximum transition run code having a 6/7 rate shown in block diagram form in FIG. 9A comprising a finite state machine based on FIG. 8, each data word of six bits (A<sub>5</sub>, A<sub>4</sub>, A<sub>3</sub>, A<sub>2</sub>, A<sub>1</sub>, A<sub>0</sub>) is successively supplied to a clocked six bit input register, 60, at a system input, 61, during a corresponding period of the system clocking signal supplied at a clock signal input, 62. Each such input data word stored in input register 60 is transferred during the next clock period from an output, 63, of that register into an input, 64, of an encoder, 65, comprising a finite state machine based on the table in FIG. 8 to be encoded into a code word of seven bits (C<sub>6</sub>, C<sub>5</sub>, C<sub>4</sub>, C<sub>3</sub>, C<sub>2</sub>, C<sub>1</sub>, C<sub>0</sub>) provided at a code word output, 66, of that encoder.

The data words associated with code words of Group BD' for branching from state  $S_1$  (located by their hex values in FIGS. 7 and 8), and those data words associated with code words of Group CD' for branching from state  $S_2$  (similarly located) can be identified by the following equations taking a Boolean value of 1:

$$K_{bd} = (\overline{A}_3 * \overline{H}_0 * \overline{H}_7) + (A_3 * \overline{H}_{14} * \overline{H}_{15})$$

[Eq. 62]

and

$$K_{cd} = ((\vec{A}_3 * \vec{H}_0 * \vec{H}_7) + (A_3 * \vec{H}_{14} * \vec{H}_{15})) * (A_4 + A_5).$$

[Eq. 63]

12

The corresponding Boolean variables  $H_x$  are defined below. The code word bits of the code words for branchings from state  $S_0$  in the table of FIG. 8 can be expressed as follows for use in encoder 65:

$$YA_{6}=\bar{A}_{5}+(A_{5}*(A_{3}+H_{0}+H_{7})), \qquad [Eq. 64]$$

$$YA_{5}=(\bar{H}_{15}*(G_{0}+(G_{1}*(A_{3}+\bar{A}_{2}))))+A_{5}*\bar{H}_{8}*\bar{H}_{15}*(\bar{A}_{3}*A_{0}+H_{0}+A_{4})Eq. 65]$$

$$YA_{4}=(G_{1}*(H_{5}+H_{7}))+A_{5}*(H_{2}+H_{3}+H_{6}+H_{15}), \qquad [Eq. 66]$$

$$YA_{3}=((G_{0}+G_{1})*\bar{A}_{3}*A_{1})+(A_{3}*A_{2}*\bar{H}_{15})+((A_{5}+A_{4})*\bar{A}_{3}*A_{2}), \qquad [Eq. 67]$$

$$YA_{2}=(G_{0}*\bar{A}_{3}*A_{0})+(A_{3}*A_{1}*\bar{H}_{15})+(G_{1}*\bar{A}_{3}*\bar{A}_{2}*A_{0}), \qquad [Eq. 68]$$

$$YA_{1}=(A_{3}*A_{0})+(A_{4}*\bar{A}_{3}*A_{2})+(A_{5}*\bar{A}_{3}), \qquad [Eq. 69]$$

$$YA_{0}=(\bar{A}_{3}+H_{15})+(A_{5}*H_{8}), \qquad [Eq. 70]$$

where the corresponding Boolean variables  $G_x$  and  $H_x$  are defined below.

The two bits representing the next state for the code words for branchings from state  $S_0$  out of the four possible next states can be expressed as follows for use in encoder 65:

$$NA_1 = A_5 + (G_0 * (\overline{A}_3 + H_{15})) + (G_1 * (\overline{A}_3 * A_2 + H_{15})),$$

[Eq. 71]

$NA_0 = (G_0 * \overline{A}_3 * A_2) + (G_1 * \overline{H}_4 * \overline{H}_5) + G_3.$  [Eq. 72]

The code word bits of the code words for branchings from state  $S_1$  in the table of FIG. 8 can be expressed as follows for use in encoder 65:

$$YB_{6}=1$$

[Eq. 73]

$$YB_{5}=0$$

[Eq. 74]

$$YB_{4}=(K_{bd}*A_{3})+H_{14}+H_{15}$$

[Eq. 75]

$$YB_{3}=(K_{bd}*A_{2})+H_{7}+(H_{15}*(A_{4}+A_{5}))+(H_{0}*\bar{A}_{4}*\bar{A}_{5})$$

[Eq. 76]

$$YB_{2}=(K_{bd}*A_{1})+H_{0}+(H_{14}*(A_{4}+A_{5}))+(H_{7}*\bar{A}_{4}*\bar{A}_{5})$$

[Eq. 77]

$$YB_{1}=(K_{bd}*A_{0})$$

[Eq. 78]

$$YB_{0}=\bar{K}_{bd}$$

[Eq. 79]

The two bits representing the next state for the code words for branchings from state  $S_1$  can be expressed as follows for use in encoder 65:

$$NB_1 = A_5 + ((H_0 + H_7 + H_{14} + H_{15}) *G_0)$$

[Eq. 80]

$NB_0 = A_4 + (A_2 *A_1 *A_0 *G_0)$  [Eq. 81]

The code word bits of the code words for branchings from state S<sub>2</sub> in the table of FIG. 8 can be expressed as follows for use in encoder 65:

| <i>YC<sub>6</sub></i> =0                                                                                                               | [Eq. 82] |

|----------------------------------------------------------------------------------------------------------------------------------------|----------|

| $YC_5 = (K_{cd} * A_0) + H_{14} + H_{15} + H_5 + H_{13}$                                                                               | [Eq. 83] |

| $YC_4\!\!=\!\!(K_{cd}\!\!*\!\!A_1)\!\!+\!\!(A_1\!\!*\!\!\bar{A}_2)\!\!+\!\!(G_0\!\!*\!\!(H_1\!\!+\!\!H_4\!\!+\!\!H_9\!\!+\!\!H_{12}))$ | [Eq. 84] |

| $YC_3 = (K_{cd}*A_2) + (G_0*(\overline{A}_2*(A_1+A_0))) + H_4 + H_7 + H_{12} + H_{15}$                                                 | [Eq. 85] |

| $YC_2 = (K_{cd} * A_3) + H_7 + H_{15}$                                                                                                 | [Eq. 86] |

| $YC_1 = (G_0 * \bar{A}_0) + H_0 + H_{14}$                                                                                              | [Eq. 87] |

| $YC_0=K_{cd}+H_6+H_8$                                                                                                                  | [Eq. 88] |

The two bits representing the next state for the code words for branchings from state  $S_2$  can be expressed as follows for use in encoder 65:

$$NC_1=A_5+(G_0*((A_3*\bar{A}_2)+H_6+H_{12}))$$

[Eq. 89]

$NC_0=A_4+(G_0*(H_3+H_4+H_5+H_6+H_{11}+H_{12}))$  [Eq. 90]

The code word bits of the code words for branchings from state  $S_3$  in the table of FIG. 8 can be expressed as follows for use in encoder 65:

| YD <sub>6</sub> =0                             | [Eq. 91] |    |

|------------------------------------------------|----------|----|

| YD <sub>5</sub> =A <sub>3</sub>                | [Eq. 92] | 10 |

| $YD_4=A_2$                                     | [Eq. 93] |    |

| $YD_3 = \overline{A}_2 * A_1$                  | [Eq. 94] |    |

| $YD_2 = (\bar{A}_2 * \bar{A}_1) + (A_2 * A_1)$ | [Eq. 95] | 15 |

| $YD_i=A_0$                                     | [Eq. 96] |    |

| <i>YD</i> <sub>0</sub> =0                      | [Eq. 97] |    |

The two bits representing the next state for the code words  $^{20}$  for branchings from state  $S_3$  can be expressed as follows for use in encoder 65:

$$ND_1=A_5$$

[Eq. 98]  $ND_0=A_4$  [Eq. 99]

The corresponding Boolean variables  $G_x$  and  $H_x$  used in the preceding encoding expressions for the code word bits are defined as follows:

|                                                                   |           | 30 |

|-------------------------------------------------------------------|-----------|----|

| $G_0=\bar{A}_s*\bar{A}_4$                                         | [Eq. 100] |    |

| $G_1=\bar{A}_5*A_4$                                               | [Eq. 101] |    |

| $G_2 = A_5 * \bar{A}_4$                                           | [Eq. 102] | 35 |

| G <sub>3</sub> =A <sub>5</sub> *A <sub>4</sub>                    | [Eq. 103] |    |

| $H_0 = \bar{A}_3 * \bar{A}_2 * \bar{A}_1 * \bar{A}_0$             | [Eq. 104] |    |

| $H_1 = \bar{A}_3 * \bar{A}_2 * \bar{A}_1 * A_0$                   | [Eq. 105] | 40 |

| $H_2 = \bar{A}_3 * \bar{A}_2 * A_1 * \bar{A}_0$                   | [Eq. 106] |    |

| $H_3 = \bar{A}_3 * \bar{A}_2 * A_1 * A_0$                         | [Eq. 107] |    |

| $H_4\!\!=\!\!ar{A}_3\!\!*\!\!A_2\!\!*\!\!ar{A}_1\!\!*\!\!ar{A}_0$ | [Eq. 108] | 45 |

| $H_5 = \bar{A}_3 * A_2 * \bar{A}_1 * A_0$                         | [Eq. 109] |    |

| $H_6 = \bar{A}_3 * A_2 * A_1 * \bar{A}_0$                         | [Eq. 110] |    |

| $H_7 = \bar{A}_3 * A_2 * A_1 * A_0$                               | [Eq. 111] | 50 |

| $H_8 = A_3 * \bar{A}_2 * \bar{A}_1 * \bar{A}_0$                   | [Eq. 112] |    |

| $H_9 = A_3 * \bar{A}_2 * \bar{A}_1 * A_0$                         | [Eq. 113] |    |

| $H_{10} = A_3 * \bar{A}_2 * A_1 * \bar{A}_0$                      | [Eq. 114] | 55 |

| $H_{11}=A_3*\bar{A}_2*A_1*A_0$                                    | [Eq. 115] |    |

| $H_{12} = A_3 * A_2 * \bar{A}_1 * \bar{A}_0$                      | [Eq. 116] |    |

| $H_{13} = A_3 * A_2 * \bar{A}_1 * A_0$                            | [Eq. 117] | 60 |

| $H_{14}=A_3*A_2*A_1*\bar{A}_0$                                    | [Eq. 118] |    |

| $H_{15} = A_3 * A_2 * A_1 * A_0$                                  | [Eq. 119] |    |

The output code words of the encoder are formed by the 65 code word bits  $C_6$ ,  $C_5$ ,  $C_4$ ,  $C_3$ ,  $C_2$ ,  $C_1$  and  $C_0$  formed by selecting the proper one of the corresponding preceding

code word bit expressions from each of the four sets thereof through use of the next state expression associated therewith delayed by one state transition (or one system clock period) to provide the current state indication therefor, the expressions for the seven code word bits being as follows:

$C_6 = (\overline{K}s_1 * \overline{K}s_0) * YA_6 + (\overline{K}s_1 * Ks_0) * YB_6 + (Ks_1 * \overline{K}s_0) * YC_6 +$

$$(Ks_1*Ks_0)*YD_6 \qquad [Eq. 120]$$

$$C_5 = (\overline{K}s_1*\overline{K}s_0)*YA_5 + (\overline{K}s_1*Ks_0)*YB_5 + (Ks_1*\overline{K}s_0)*YC_5 + (Ks_1*\overline{K}s_0)*YD_5 \qquad [Eq. 121]$$

$$C_4 = (\overline{K}s_1*\overline{K}s_0)*YA_4 + (\overline{K}s_1*Ks_0)*YB_4 + (Ks_1*\overline{K}s_0)*YC_4 + (Ks_1*\overline{K}s_0)*YD_4 \qquad [Eq. 122]$$

$$C_3 = (\overline{K}s_1*\overline{K}s_0)*YA_3 + (\overline{K}s_1*Ks_0)*YB_3 + (Ks_1*\overline{K}s_0)*YC_3 + (Ks_1*\overline{K}s_0)*YD_3 \qquad [Eq. 123]$$

$$C_2 = (\overline{K}s_1*\overline{K}s_0)*YA_2 + (\overline{K}s_1*Ks_0)*YB_2 + (Ks_1*\overline{K}s_0)*YC_2 + (Ks_1*\overline{K}s_0)*YD_2 \qquad [Eq. 124]$$

$$C_1 = (\overline{K}s_1*\overline{K}s_0)*YA_1 + (\overline{K}s_1*Ks_0)*YB_1 + (Ks_1*\overline{K}s_0)*YC_1 + (Ks_1*\overline{K}s_0)*YD_1 \qquad [Eq. 125]$$

$$C_0 = (\overline{K}s_1*\overline{K}s_0)*YA_0 + (\overline{K}s_1*Ks_0)*YB_0 + (Ks_1*\overline{K}s_0)*YC_0 + (Ks_1*\overline$$

The associated next state is selected in the same manner resulting in the two bits representing the next state being expressed as follows:

$(Ks_1*Ks_0)*YD_0$

$$Ns_{1} = (\overline{K}s_{1} * \overline{K}s_{0}) * NA_{1} + (\overline{K}s_{1} * Ks_{0}) * NB_{1} + (Ks_{1} * \overline{K}s_{0}) * NC_{1} + (Ks_{1} * Ks_{0}) * ND_{1}$$

$$Eq. 127$$

$$Ns_{0} = (\overline{K}s_{1} * \overline{K}s_{0}) * NA_{0} + (\overline{K}s_{1} * Ks_{0}) * NB_{0} + (Ks_{1} * \overline{K}s_{0}) * NC_{0} + (Ks_{1} * \overline{K}s_{0}) * ND_{0}$$

$$(Eq. 128]$$

[Eq. 126]

where (Ks<sub>1</sub>,Ks<sub>0</sub>) is an ordered pair of bits representing the current state. (Ks<sub>1</sub>, Ks<sub>0</sub>) equal to the Boolean values (0,0) represents state S<sub>0</sub>, equal to (0,1) represents state S<sub>1</sub>, equal to (1,0) represents state S<sub>2</sub> and equal to (1,1) represents state S<sub>3</sub>. Here (Ks<sub>1</sub>,Ks<sub>0</sub>) are bits representing the current state, and are the bits (Ns<sub>1</sub>,Ns<sub>0</sub>) provided at a next state output, 67, of encoder 65 delayed by one state transition, or clock period, in a clocked two bit delay register, 68, having its next state input, 69, connected to encoder output 67. The system clock signal is also provided to register 68 at a clocking input, 70, thereof. An output, 71, of register 68 is connected to a current state input, 72, of encoder 65.

In the corresponding decoder system for this 6/7 rate MTR code shown in block diagram form in FIG. 9B, output data words formed of six bits A<sub>5</sub>, A<sub>4</sub>, A<sub>3</sub>, A<sub>2</sub>, A<sub>1</sub> and A<sub>0</sub> are recovered based on successive pairs of input code words of seven bits each taken from the sequence of code words where each input code word in such a pair is in succession in the sequence thereof. Current code words, formed of the bits C<sub>6</sub>, C<sub>5</sub>, C<sub>4</sub>, C<sub>3</sub>, C<sub>2</sub>, C<sub>1</sub> and C<sub>0</sub>, provide the information as to the corresponding current states of the encoder, and the next following code word of each current code word, formed by the bits C<sub>13</sub>, C<sub>12</sub>, C<sub>11</sub>, C<sub>10</sub>, C<sub>9</sub>, C<sub>8</sub> and C<sub>7</sub>, provides the information as to the corresponding next state. Together, they point to the corresponding unique data word to result from the decoding.

In this decoder system, each input code word of seven bits is successively supplied to a clocked seven bit input register, 80, at a system input, 81, during a corresponding period of the system clocking signal supplied at a clock signal input, 82. Each such input data word stored in input register 80 represents the following or next code word (C<sub>13</sub>, C<sub>12</sub>, C<sub>11</sub>, C<sub>10</sub>, C<sub>9</sub>, C<sub>8</sub>, C<sub>7</sub>) after storage in input register 80, but is transferred during the next clock period from an output, 83, of that register into an input, 84, of another clocked seven bit

holding register, 85, where it becomes the current code word  $(C_6, C_5, C_4, C_3, C_2, C_1, C_0)$  after storage therein. The system clock signal is also applied to a clocking input, 86, of register 85. The new input code word stored in input register 80 during the time the preceding code word is stored in 5 holding register 85 then becomes the next code word during the time held in register 80.

The code word in input register 80, as the next code word, is also supplied at output 83 thereof to a first input, 87, as is the current code word from an output, 88, of delay register 10 85 to a second input, 89, of a code word legality checker, 90. If the seven code bits in any code word received form an illegal code word representing an eliminated seven bit word (any of the words that were eliminated in forming Groups AA, AB, AC, AD, BB, BD', CC, CD', D' and D" above), a 15 flag signal taking a Boolean value of 1 at the output of checker 90 will indicate so as a basis for a user to arrange some corresponding action if desired. This flag signal LL as implemented in checker 90 can be expressed as:

$$LL=L_1+L_2+L_3+L_4$$

, [Eq. 129]

where

The code words can be divided into groups AA, AB, AC, AD', BB, BD, CC', CD, D' and D" as described above. Group AD' is formed by removing code word 1000001 therefrom as indicated above, and its occurrence in a transition from state So is provided for directly in the decoder data word digit expressions below. Similarly, Group CC' is formed by removing code word 0000011 therefrom as indicated above, and its occurrence in a transition from state S<sub>2</sub> is also provided for directly in the decoder data word digit expressions below. Groups BD and CD are used rather than Groups BD' and CD' resulting from the removal of code words 1000000 and 0000001 therefrom, respectively, as indicated above, and relying on signal LL to indicate their occurrence. Current state code words can be identified as belonging to Groups AA, AB, AC, AD', BB, BD, CC', CD, D' and D" by the corresponding variables  $K_{aa}$ ,  $K_{ab}$ ,  $K_{ac}$ ,  $K_{adv}$  $K_{bb}$ ,  $K_{bd}$ ,  $K_{cc}$ ,  $K_{cd}$ ,  $K_{d'}$  and  $K_{d''}$  in the expressions below taking a Boolean value of 1:

| Group AA) $K_{aa} = C_6 * C_5 * C_1 * C_0$ ,                                                                                                                                        | [Eq. 134] |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Group AB) $K_{ab} = C_6 * C_5 * \bar{C}_1 * C_0$ ,                                                                                                                                  | [Eq. 135] |

| Group AC) $K_{ac} = C_6 * \bar{C}_5 * C_1 * C_0$ ,                                                                                                                                  | [Eq. 136] |

| Group $AD$ ) $K_{ad} = C_6 * \overline{C}_5 * (C_4 + C_3 + C_2) * \overline{C}_1 * C_0$ ,                                                                                           | [Eq. 137] |

| Group $BB'$ ) $K_{bb} = C_6 * C_5 * \bar{C}_0$ ,                                                                                                                                    | [Eq. 138] |

| Group $BD$ ) $K_{bd}=C_6*\bar{C}_5*\bar{C}_0$ ,                                                                                                                                     | [Eq. 139] |

| Group $CC'$ ) $K_{cc} = \bar{C}_6 * C_1 * C_0 * (C_5 + C_4 + C_3),$                                                                                                                 | [Eq. 140] |

| Group $CD$ ) $K_{cd} = \bar{C}_6 * \bar{C}_1 * C_0$ ,                                                                                                                               | [Eq. 141] |

| $\text{Group }D")\ \textit{K}_{d^*}\!\!=\!\!\bar{C}_6\!\!*\!\!\bar{C}_0\!\!*\!\!(\overline{C}_3\!\!*\!\!(C_4\!\!+\!\!C_2)\!\!+\!\!\!\overline{C}_4\!\!*\!\!C_3\!\!*\!\!\bar{C}_2),$ | [Eq. 142] |

| Group $D'$ ) $K_d = \bar{C}_6 * \bar{C}_0 * \bar{K}_{d^n}$ .                                                                                                                        | [Eq. 143] |

60

16

The current states of the received code words imposed by the encoder can be expressed by the equations: